2021.07.06

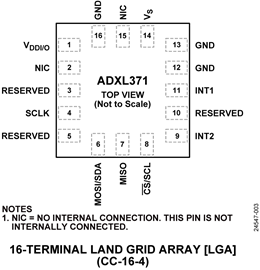

▶ 정 범위 ±200g

▶ 4극 앨리어스 필터를 사용한 160Hz ~ 2560Hz 사용자 선택 가능 대역폭

▶ 선택 가능한 오버샘플링 비율

▶ 조절 가능한 하이패스 필터

▶ 초저전력

▶ 동력은 코인 셀 배터리에서 얻을 수 있음

▶ 2560Hz ODR에서 28μA, 3.3V 공급

▶ 저전력, 저활성 감지를 위한 웨이크업 모드

▶ 1.7μA 인스턴트 온 모드(임계값 조절 가능)

▶ <0.1μA 대기 모드

▶ 시스템 레벨 절전 기능을 위한 내장 기능

▶ 프로세서 개입 없이 자동 인터럽트 처리

▶ 초저전력 이벤트 모니터링으로 영향을 감지하고 일시적 이벤트를 캡처할 수 있을 만큼 빠르게 웨이크업

▶ 조절 가능한 낮은 g 임계값 활동 및 비활성 감지

▶ 넓은 작동 전압 범위: 2.5V ~ 3.5V

▶ 외부 트리거를 통한 가속 샘플 동기화

▶ SPI 디지털 인터페이스 및 I2C 인터페이스 형식 지원

▶ 100mg/LSB 스케일 팩터에서 12비트 출력

▶ 넓은 온도 범위: -40°C~+105°c

▶ 소형, 얇은, 3mm × 3.25mm × 1.06mm 패키지