신규 제품

- All

- Amplifiers

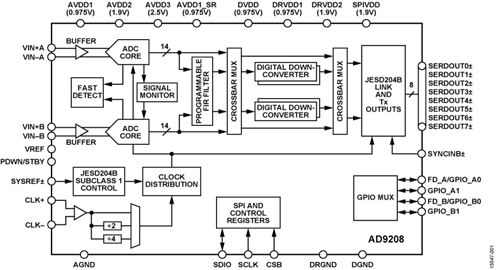

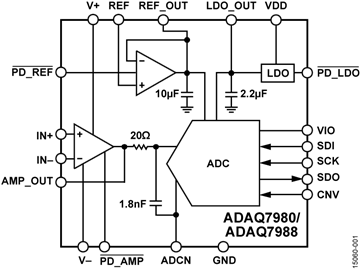

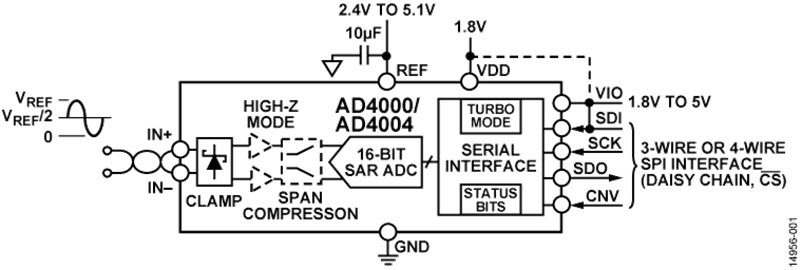

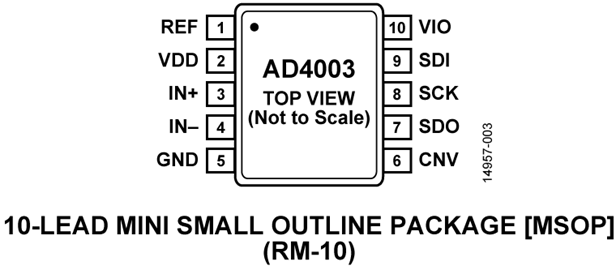

- Analog to Digital Converters

- Application Specific

- Audio & Video Products

- Broadband

- Clock & Timing

- Digital to Analog Converters

- High Speed Logic

- Interface & Isolation

- Linear Products

- MEMS

- Optical

- Power Management

- Processors & DSP

- RF & Microwave

- Sensors

- Switches & Multiplexers

- Industrial Ethernet

- Power Monitor Control& Protection

- ETC

- DC-DC