기술기고문

초저잡음 LDO 레귤레이터로 깨끗한 전력 공급

글 : 스티브 노스(Steve Knoth) / 아나로그디바이스(Analog Devices, Inc.)

선형 레귤레이터 IC는 인덕터를 사용하지 않으면서 높은 전압에서 낮은 전압으로 전압을 강하한다. 저전압 강하(LDO) 선형 레귤레이터는 강하 전압(레귤레이션을 유지하는 데 필요한 입력 전압과 출력 전압의 차이)이 통상 400mV 미만인 특수한 종류의 선형 레귤레이터이다. 초기 선형 레귤레이터 설계는 ~1.3V 정도의 강하를 제공했다. 이는 5V 입력의 경우 디바이스가 레귤레이션을 유지하기 위해 최대 달성 가능한 출력이 ~3.7V에 불과하다는 것을 의미한다. 한편 오늘날에는 더 정교한 설계 기법과 웨이퍼 제조 공정이 도입되면서, 낮은 강하는 대략 100mV ~ 300mV로 정의되고 있다.

LDO 레귤레이터는 특정 시스템에서 가장 비용이 적게 드는 부품의 하나인 경우가 많지만, 비용 대비 편익 기준에서 가장 효용이 높은 부품의 하나이기도 하다. 출력 전압 레귤레이션 외에도 LDO 레귤레이터가 하는 또 다른 중요한 일은 과도 전압, 전원 잡음, 역 전압, 전류 서지 등과 같은 열악한 환경 조건으로부터 값비싼 다운스트림 부하를 보호하는 일이다. 따라서 레귤레이터 설계는 견고해야 하며, 부하를 보호하는 동시에 환경으로부터 발생하는 나쁜 영향을 흡수하는 데 필요한 모든 보호 기능을 포함해야 한다. 많은 저가형 LDO 선형 레귤레이터는 필요한 보호 기능이 없어 고장이 발생하고, 그에 따라 종종 레귤레이터 자체뿐 아니라 다운스트림 부하까지 손상을 입을 수 있다.

LDO 레귤레이터 vs. 기타 레귤레이터

저전압 스텝다운 변환과 레귤레이션은 다양한 방법을 통해 달성할 수 있다.

스위칭 레귤레이터는 넓은 범위의 전압에서 높은 효율로 동작하지만, 동작하려면 인덕터와 커패시터 같은 외부 부품을 필요로 하므로 비교적 넓은 보드 공간을 차지한다. 또한 인덕터리스 차지 펌프(또는 스위치드 커패시터 전압 컨버터)를 사용하여 낮은 전압으로 변환할 수 있는데, 변환 영역에 따라 보통 더 높은 효율로 동작하지만 출력 전류 성능이 제한되므로 과도 상태 성능이 좋지 않고 선형 레귤레이터에 비해 더 많은 외부 부품을 필요로 한다.

FPGA, DSP, CPU, GPU 및 ASIC와 같은 오늘날의 최신 고속, 고전류, 저전압 디지털 IC는 코어 및 I/O 채널에 전력을 공급하는 전원에 보다 엄격한 요구를 하고 있다. 전통적으로 차지 펌프는 필요한 출력 전류와 과도 응답이 부족하기 때문에 효율적인 스위칭 레귤레이터를 사용하여 이러한 디바이스에 전력을 공급해 왔다.

그러나 스위처는 잡음 간섭 문제가 있을 수 있으며, 때때로 과도 응답이 느리거나 레이아웃이 제한될 수 있다.

따라서 LDO 레귤레이터는 이러한 애플리케이션뿐 아니라 다른 저전압 시스템에 대안을 제공한다. 최근의 제품 혁신과 기능 향상 덕분에 LDO 레귤레이터는 더욱 매력적인 성능 장점을 제공한다.

또한 잡음에 민감한 아날로그/RF 애플리케이션(시험 및 계측 시스템에서 흔히 볼 수 있으며, 이들 시스템은 기계 또는 장비의 측정 정확도가 측정되는 대상보다 수백 배는 더 우수해야 한다)에 전력을 공급하는 경우 일반적으로 LDO 레귤레이터가 스위칭 레귤레이터보다 선호된다. 저잡음 LDO 레귤레이터는 주파수 합성기(PLL/VCO), RF 믹서 및 변조기, 고속 고분해능 데이터 컨버터, 정밀 센서를 포함하여 다양한 종류의 아날로그/RF 설계에 전력을 공급한다. 그럼에도 이러한 애플리케이션은 기존 저잡음 LDO 레귤레이터의 한계를 시험하는 수준의 감도에 도달해 있다. 예를 들어 많은 하이엔드 VCO에서 전원 잡음은 VCO 출력 위상 잡음(지터)에 직접적인 영향을 미친다. 전체 시스템 효율 요구사항을 만족하기 위해 일반적으로 LDO 레귤레이터는 비교적 잡음이 많은 스위칭 컨버터 출력을 포스트 레귤레이트 하는데, LDO의 고주파 PSRR(power supply ripple rejection) 성능이 무엇보다 중요하다. 뿐만 아니라 잡음 수준은 LDO 레귤레이터에 의해 mV(rms) 범위에서 한 자릿수 μV(rms) 범위로 표준 산업 스위칭 레귤레이터에 비해 수백, 수천 배까지 더욱 감소시킬 수 있다.

LDO 설계 과제

연산 증폭기, 계측 증폭기와 같은 일부 IC와 디지털-아날로그 컨버터(DAC), 아날로그-디지털 컨버터(ADC) 같은 데이터 컨버터는 전력 공급을 위해 2개의 입력 전원을 필요로 하므로 듀얼 극성이라고 한다(양의 극성 하나, 음의 극성 하나). 양의 레일은 보통 양의 전압 레퍼런스에 의하거나 더 바람직하게는 선형 또는 저전압 강하 레귤레이터에 의해 전력을 공급받아 왔다. 음의 레일은 전통적으로 네거티브 스위칭 레귤레이터 또는 인버터에 의해 전력을 공급받았다. 그러나 인덕터 기반 스위처는 쉽게 잡음을 시스템에 유입할 수 있다. 네거티브 레귤레이터가 등장하면서 네거티브 LDO 레귤레이터를 사용하여 음의 시스템 레일에 전력을 공급하고, 모든 LDO 레귤레이터 기능(인덕터 불필요, 저잡음, 높은 PSRR, 빠른 과도 응답, 완벽한 보호)을 이용하기가 유리해졌다. 오래된 구형 LDO 레귤레이터는 PSRR 및 잡음 성능이 훨씬 떨어지지만, 여전히 이러한 유형의 조용한 전원을 생성하는 데 사용할 수 있다. 하지만 이 경우 시스템을 완성하는 데 많은 추가적인 부품, 보드 공간, 설계 시간이 들어간다. 또한 이와 같은 별도의 부품은 특성(기생 저항 등)에 따라 전력 예산에 부정적인 영향을 미칠 수 있다.

연산 증폭기, ADC 또는 다른 신호 체인 부품을 사용하는 고객의 경우 또 다른 어려운 시스템 성능 특성이 있다. 이들 IC는 무한한 전원전압 변동 제거비 성능을 갖지 못하며, 더욱 나쁘게는 전원전압 변동 제거비 성능이 높은 주파수에서 상당히 낮을 수 있다. 과거에는 이에 따라 보드에 별도의 필터링 부품을 사용해야 했다. 이는 솔루션 크기를 증가시킨다. 뿐만 아니라 설계자가 높은 정확도를 얻고자 하는 경우 레귤레이터 전원이 과도한 잡음을 발생시켜 측정 시나리오에 원하지 않은 진동을 일으킴으로써 더 많은 문제가 나타날 수 있다.

많은 산업 표준 선형 레귤레이터는 단일 전압 전원으로 저전압 강하 동작을 수행하지만, 대부분은 매우 낮은 전압 변환과 낮은 출력 잡음, 넓은 범위의 입/출력 전압, 광범위한 보호 기능을 함께 달성하지 못한다. PMOS LDO 레귤레이터는 전압 강하를 달성하고 단일 전원으로 동작하지만 통과 트랜지스터의 VGS 특성으로 인해 낮은 입력 전압으로 제한되며, 고성능 레귤레이터의 많은 보호 기능들이 없다. NMOS 기반 디바이스는 빠른 과도 응답을 제공하지만, 디바이스를 바이어스하기 위해 2개의 전원을 필요로 한다. NPN 레귤레이터는 넓은 입/출력 전압 범위를 제공하지만, 2개의 전원 전압 또는 더 높은 전압 강하를 필요로 한다. 반면에 적절한 설계 아키텍처를 갖는 PNP 레귤레이터는 저전압 강하, 높은 입력 전압, 낮은 잡음, 높은 PSRR, 매우 낮은 전압 변환을 달성하고 완벽한 보호를 제공할 뿐 아니라 이 모든 것이 단일 전원 레일에서 제공된다.

최상의 전체 효율을 달성하기 위해 많은 고성능 아날로그 및 RF 회로들이 스위칭 컨버터의 출력을 포스트 레귤레이트하는 LDO 레귤레이터로부터 전력을 공급받는다. 이렇게 하기 위해서는 LDO 레귤레이터 전반에 걸쳐 낮은 입력-출력 차이로 높은 PSRR과 낮은 출력 전압 잡음을 달성해야 한다. 높은 PSRR을 갖는 LDO 레귤레이터는 부피가 큰 필터링 부품을 사용하지 않고도 스위처의 출력에서 잡음을 쉽게 필터링하고 제거한다. 뿐만 아니라 넓은 대역폭에 걸쳐 낮은 출력 전압 잡음을 갖는 디바이스는 잡음 민감도가 중요한 고려사항인 오늘날의 최신 레일에 유용하다. 높은 전류에서 낮은 출력 전압 잡음은 필수적인 규격이 되고 있다.

새로운 초저잡음, 매우 높은 PSRR LDO 레귤레이터

위에서 언급한 문제를 해결하는 LDO 솔루션은 다음과 같은 특성을 갖춰야 한다.

선형 레귤레이터 IC는 인덕터를 사용하지 않으면서 높은 전압에서 낮은 전압으로 전압을 강하한다. 저전압 강하(LDO) 선형 레귤레이터는 강하 전압(레귤레이션을 유지하는 데 필요한 입력 전압과 출력 전압의 차이)이 통상 400mV 미만인 특수한 종류의 선형 레귤레이터이다. 초기 선형 레귤레이터 설계는 ~1.3V 정도의 강하를 제공했다. 이는 5V 입력의 경우 디바이스가 레귤레이션을 유지하기 위해 최대 달성 가능한 출력이 ~3.7V에 불과하다는 것을 의미한다. 한편 오늘날에는 더 정교한 설계 기법과 웨이퍼 제조 공정이 도입되면서, 낮은 강하는 대략 100mV ~ 300mV로 정의되고 있다.

LDO 레귤레이터는 특정 시스템에서 가장 비용이 적게 드는 부품의 하나인 경우가 많지만, 비용 대비 편익 기준에서 가장 효용이 높은 부품의 하나이기도 하다. 출력 전압 레귤레이션 외에도 LDO 레귤레이터가 하는 또 다른 중요한 일은 과도 전압, 전원 잡음, 역 전압, 전류 서지 등과 같은 열악한 환경 조건으로부터 값비싼 다운스트림 부하를 보호하는 일이다. 따라서 레귤레이터 설계는 견고해야 하며, 부하를 보호하는 동시에 환경으로부터 발생하는 나쁜 영향을 흡수하는 데 필요한 모든 보호 기능을 포함해야 한다. 많은 저가형 LDO 선형 레귤레이터는 필요한 보호 기능이 없어 고장이 발생하고, 그에 따라 종종 레귤레이터 자체뿐 아니라 다운스트림 부하까지 손상을 입을 수 있다.

LDO 레귤레이터 vs. 기타 레귤레이터

저전압 스텝다운 변환과 레귤레이션은 다양한 방법을 통해 달성할 수 있다.

스위칭 레귤레이터는 넓은 범위의 전압에서 높은 효율로 동작하지만, 동작하려면 인덕터와 커패시터 같은 외부 부품을 필요로 하므로 비교적 넓은 보드 공간을 차지한다. 또한 인덕터리스 차지 펌프(또는 스위치드 커패시터 전압 컨버터)를 사용하여 낮은 전압으로 변환할 수 있는데, 변환 영역에 따라 보통 더 높은 효율로 동작하지만 출력 전류 성능이 제한되므로 과도 상태 성능이 좋지 않고 선형 레귤레이터에 비해 더 많은 외부 부품을 필요로 한다.

FPGA, DSP, CPU, GPU 및 ASIC와 같은 오늘날의 최신 고속, 고전류, 저전압 디지털 IC는 코어 및 I/O 채널에 전력을 공급하는 전원에 보다 엄격한 요구를 하고 있다. 전통적으로 차지 펌프는 필요한 출력 전류와 과도 응답이 부족하기 때문에 효율적인 스위칭 레귤레이터를 사용하여 이러한 디바이스에 전력을 공급해 왔다.

그러나 스위처는 잡음 간섭 문제가 있을 수 있으며, 때때로 과도 응답이 느리거나 레이아웃이 제한될 수 있다.

따라서 LDO 레귤레이터는 이러한 애플리케이션뿐 아니라 다른 저전압 시스템에 대안을 제공한다. 최근의 제품 혁신과 기능 향상 덕분에 LDO 레귤레이터는 더욱 매력적인 성능 장점을 제공한다.

또한 잡음에 민감한 아날로그/RF 애플리케이션(시험 및 계측 시스템에서 흔히 볼 수 있으며, 이들 시스템은 기계 또는 장비의 측정 정확도가 측정되는 대상보다 수백 배는 더 우수해야 한다)에 전력을 공급하는 경우 일반적으로 LDO 레귤레이터가 스위칭 레귤레이터보다 선호된다. 저잡음 LDO 레귤레이터는 주파수 합성기(PLL/VCO), RF 믹서 및 변조기, 고속 고분해능 데이터 컨버터, 정밀 센서를 포함하여 다양한 종류의 아날로그/RF 설계에 전력을 공급한다. 그럼에도 이러한 애플리케이션은 기존 저잡음 LDO 레귤레이터의 한계를 시험하는 수준의 감도에 도달해 있다. 예를 들어 많은 하이엔드 VCO에서 전원 잡음은 VCO 출력 위상 잡음(지터)에 직접적인 영향을 미친다. 전체 시스템 효율 요구사항을 만족하기 위해 일반적으로 LDO 레귤레이터는 비교적 잡음이 많은 스위칭 컨버터 출력을 포스트 레귤레이트 하는데, LDO의 고주파 PSRR(power supply ripple rejection) 성능이 무엇보다 중요하다. 뿐만 아니라 잡음 수준은 LDO 레귤레이터에 의해 mV(rms) 범위에서 한 자릿수 μV(rms) 범위로 표준 산업 스위칭 레귤레이터에 비해 수백, 수천 배까지 더욱 감소시킬 수 있다.

LDO 설계 과제

연산 증폭기, 계측 증폭기와 같은 일부 IC와 디지털-아날로그 컨버터(DAC), 아날로그-디지털 컨버터(ADC) 같은 데이터 컨버터는 전력 공급을 위해 2개의 입력 전원을 필요로 하므로 듀얼 극성이라고 한다(양의 극성 하나, 음의 극성 하나). 양의 레일은 보통 양의 전압 레퍼런스에 의하거나 더 바람직하게는 선형 또는 저전압 강하 레귤레이터에 의해 전력을 공급받아 왔다. 음의 레일은 전통적으로 네거티브 스위칭 레귤레이터 또는 인버터에 의해 전력을 공급받았다. 그러나 인덕터 기반 스위처는 쉽게 잡음을 시스템에 유입할 수 있다. 네거티브 레귤레이터가 등장하면서 네거티브 LDO 레귤레이터를 사용하여 음의 시스템 레일에 전력을 공급하고, 모든 LDO 레귤레이터 기능(인덕터 불필요, 저잡음, 높은 PSRR, 빠른 과도 응답, 완벽한 보호)을 이용하기가 유리해졌다. 오래된 구형 LDO 레귤레이터는 PSRR 및 잡음 성능이 훨씬 떨어지지만, 여전히 이러한 유형의 조용한 전원을 생성하는 데 사용할 수 있다. 하지만 이 경우 시스템을 완성하는 데 많은 추가적인 부품, 보드 공간, 설계 시간이 들어간다. 또한 이와 같은 별도의 부품은 특성(기생 저항 등)에 따라 전력 예산에 부정적인 영향을 미칠 수 있다.

연산 증폭기, ADC 또는 다른 신호 체인 부품을 사용하는 고객의 경우 또 다른 어려운 시스템 성능 특성이 있다. 이들 IC는 무한한 전원전압 변동 제거비 성능을 갖지 못하며, 더욱 나쁘게는 전원전압 변동 제거비 성능이 높은 주파수에서 상당히 낮을 수 있다. 과거에는 이에 따라 보드에 별도의 필터링 부품을 사용해야 했다. 이는 솔루션 크기를 증가시킨다. 뿐만 아니라 설계자가 높은 정확도를 얻고자 하는 경우 레귤레이터 전원이 과도한 잡음을 발생시켜 측정 시나리오에 원하지 않은 진동을 일으킴으로써 더 많은 문제가 나타날 수 있다.

많은 산업 표준 선형 레귤레이터는 단일 전압 전원으로 저전압 강하 동작을 수행하지만, 대부분은 매우 낮은 전압 변환과 낮은 출력 잡음, 넓은 범위의 입/출력 전압, 광범위한 보호 기능을 함께 달성하지 못한다. PMOS LDO 레귤레이터는 전압 강하를 달성하고 단일 전원으로 동작하지만 통과 트랜지스터의 VGS 특성으로 인해 낮은 입력 전압으로 제한되며, 고성능 레귤레이터의 많은 보호 기능들이 없다. NMOS 기반 디바이스는 빠른 과도 응답을 제공하지만, 디바이스를 바이어스하기 위해 2개의 전원을 필요로 한다. NPN 레귤레이터는 넓은 입/출력 전압 범위를 제공하지만, 2개의 전원 전압 또는 더 높은 전압 강하를 필요로 한다. 반면에 적절한 설계 아키텍처를 갖는 PNP 레귤레이터는 저전압 강하, 높은 입력 전압, 낮은 잡음, 높은 PSRR, 매우 낮은 전압 변환을 달성하고 완벽한 보호를 제공할 뿐 아니라 이 모든 것이 단일 전원 레일에서 제공된다.

최상의 전체 효율을 달성하기 위해 많은 고성능 아날로그 및 RF 회로들이 스위칭 컨버터의 출력을 포스트 레귤레이트하는 LDO 레귤레이터로부터 전력을 공급받는다. 이렇게 하기 위해서는 LDO 레귤레이터 전반에 걸쳐 낮은 입력-출력 차이로 높은 PSRR과 낮은 출력 전압 잡음을 달성해야 한다. 높은 PSRR을 갖는 LDO 레귤레이터는 부피가 큰 필터링 부품을 사용하지 않고도 스위처의 출력에서 잡음을 쉽게 필터링하고 제거한다. 뿐만 아니라 넓은 대역폭에 걸쳐 낮은 출력 전압 잡음을 갖는 디바이스는 잡음 민감도가 중요한 고려사항인 오늘날의 최신 레일에 유용하다. 높은 전류에서 낮은 출력 전압 잡음은 필수적인 규격이 되고 있다.

새로운 초저잡음, 매우 높은 PSRR LDO 레귤레이터

위에서 언급한 문제를 해결하는 LDO 솔루션은 다음과 같은 특성을 갖춰야 한다.

▶ 매우 낮은 출력 잡음

▶ 넓은 범위의 주파수에서 높은 PSRR

▶ 저전압 강하 동작

▶ 단일 전원 동작(사용 편의성, 수월한 전원 시퀀싱)

▶ 빠른 과도 응답 시간

▶ 넓은 입/출력 전압 범위에서 동작

▶ 적절한 출력 전류 성능

▶ 뛰어난 열 성능

▶ 초소형 풋프린트

이러한 요구를 충족하기 위해 아나로그디바이스(Analog Devices)는 매우 높은 PSRR, 초저잡음의 포지티브 LDO 레귤레이터 LT304x 제품군을 출시했다. 가장 최근 출시된 제품은 보완적인 LT3094로, 초저잡음 매우 높은 PSRR의 저전압 강하 500mA 네거티브 선형 레귤레이터이다. 이 디바이스는 인기 있는 500mA LT3045(200mA의 경우 LT3042)의 네거티브 버전이다. LT3094의 고유한 설계는 10kHz일 때 단 2nV/√Hz의 초저 스폿 잡음과 10Hz ~ 100kHz의 넓은 대역폭에서 0.85µVrms의 적분 출력 잡음을 달성한다. PSRR 성능은 유례없는 수준으로, 저주파 PSRR은 거의 4kHz까지 100dB를 넘고, 고주파 PSRR은 2MHz까지 70dB를 넘는다. 따라서 잡음이 있거나 높은 리플의 입력 전원을 조용하고 깨끗하게 유지할 수 있다. LT3094는 정밀 전류 소스 레퍼런스에 이어 고성능 단위 이득 버퍼로 구성된 고유의 LDO 아키텍처를 채택함으로써 출력 전압과 관계없이 거의 일정한 대역폭, 잡음, PSRR, 부하 레귤레이션 성능을 제공한다. 또한 이 아키텍처는 여러 개의 LT3094를 병렬 연결하여 잡음을 추가로 감소시키고, 출력 전류를 높이고, PCB에서 열을 분산시킬 수 있게 한다.

LT3094는 –2V ~ –20V의 넓은 입력 전압 범위에 걸쳐 전체 부하에서 230mV 강하 전압으로 최대 500mA 출력 전류를 제공한다. 출력 전압 범위는 0V ~ –19.5V이고, 출력 전압 허용오차는 라인, 부하 및 온도에서 ±2%로 매우 정확하다. 디바이스의 넓은 입력 및 출력 전압 범위, 높은 대역폭, 높은 PSRR 및 매우 낮은 잡음 성능은 PLL/VCO/믹서/LNA, 그리고 시험 및 계측과 같은 초저잡음 계측, 고속/고정밀 데이터 컨버터 및 이미징, 진단과 같은 의료용 애플리케이션, 정밀 전원 및 스위칭 전원을 위한 포스트 레귤레이터와 같은 잡음에 민감한 애플리케이션에 전력을 공급하는 데 이상적이다.

LT3094는 소형의 저가 10µF 세라믹 출력 커패시터로 동작하여 안정성 및 과도 응답을 최적화한다. 단일 저항으로 외부 정밀 전류 제한(전체 온도 범위에서 최대 ±10% 오차)을 프로그래밍할 수 있다. 디바이스의 VIOC 핀은 앞 단의 레귤레이터(LT3094로 전원을 공급하는 스위칭 레귤레이터)를 제어하여 전력 소모를 최소화하고 PSRR을 최적화한다. 단일 SET 핀 커패시터는 출력 잡음을 낮추고 레퍼런스 소프트 스타트 기능을 제공함으로써 턴온 시 출력 전압 오버슛을 방지한다. 또한 디바이스의 내부 보호 회로는 폴드백을 이용한 내부 전류 제한, 히스테리시스를 이용한 열 제한을 포함한다. 그 밖의 기능으로는 빠른 스타트업 기능(큰 값의 SET 핀 커패시터를 사용할 때 유용) 및 출력 전압 레귤레이션을 표시하는 프로그래밍 가능한 임계값을 갖는 Power Good 플래그(이 기능을 탑재한 업계 최초 네거티브 LDO 레귤레이터) 등이 있다.

LT3094는 열 성능 강화된 12핀, 3mm × 3mm DFN 및 MSOP 패키지로 제공되며, 모두 초소형 풋프린트를 달성한다. 현재 –40°C ~ +125°C 동작 접합부 온도의 E 및 I 등급 버전을 구매할 수 있다.

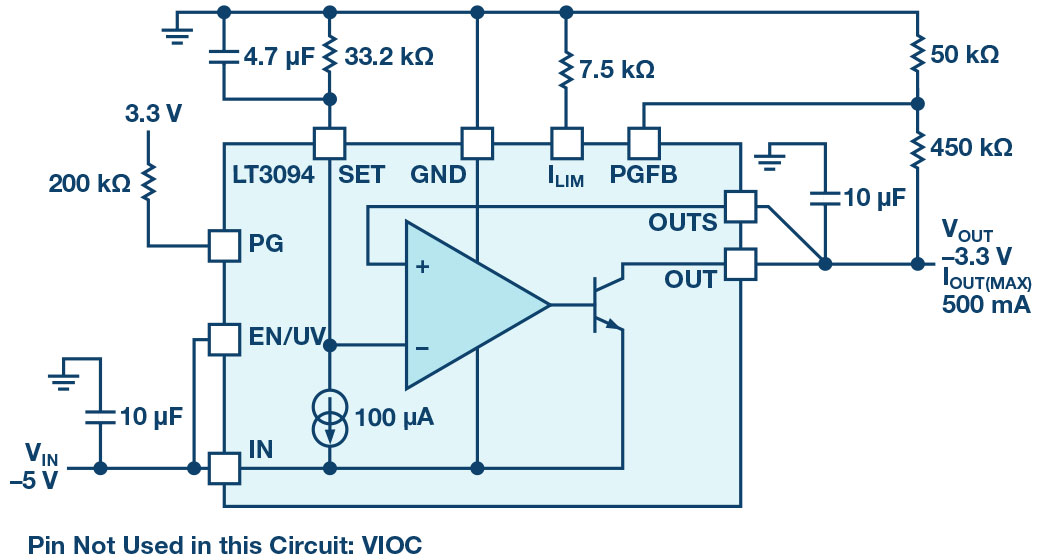

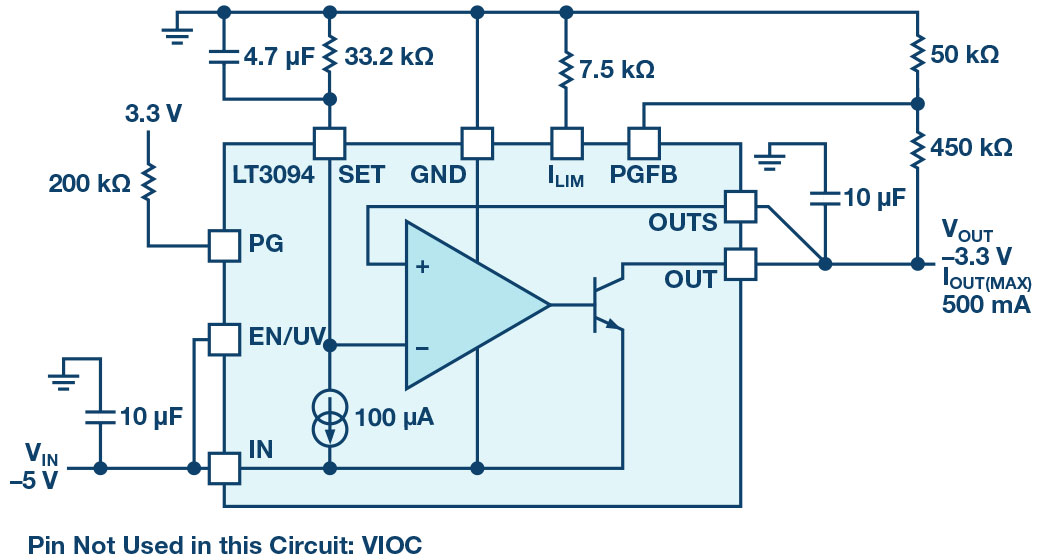

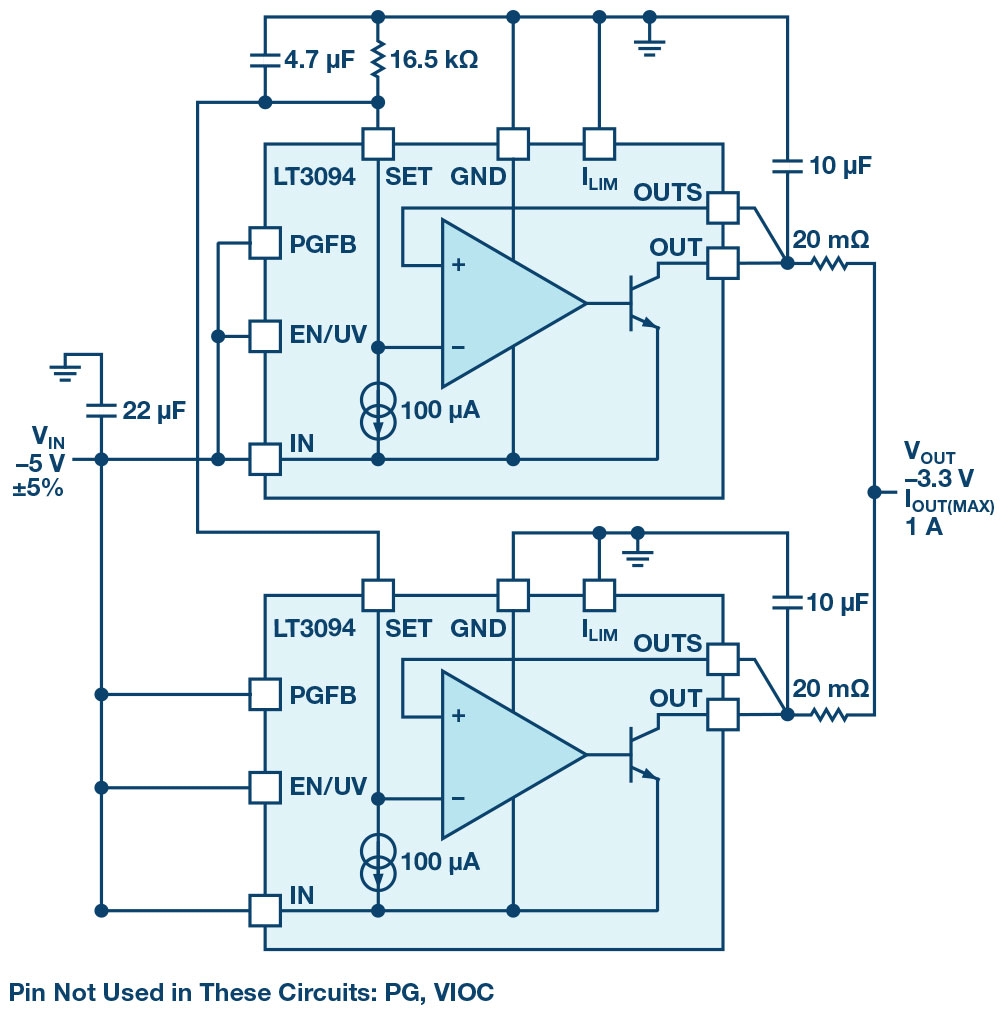

그림 1. LT3094 일반적인 애플리케이션 회로도 및 특징

LT3094는 안정성을 위해 출력 커패시터를 필요로 한다. 높은 대역폭을 고려하여 낮은 ESR 및 ESL의 세라믹 커패시터를 사용할 것을 권장한다. 안정성을 위해서는 ESR이 30mΩ 미만, ESL이 1.5nH 미만이면서 최소 10µF 출력 커패시턴스가 필요하다. 단일 10µF 세라믹 출력 커패시터를 사용하여 높은 PSRR 및 저잡음 성능을 달성하므로 이보다 높은 값의 출력 커패시터를 사용해도 성능을 조금밖에는 향상시키지 못한다. 출력 커패시턴스가 증가함에 따라 레귤레이터 대역폭이 감소하기 때문인데, 이 상충관계에 따라 최소 10µF 출력 커패시터보다 높은 값을 사용하더라도 얻을 수 있는 성능은 거의 없다. 그렇지만, 더 높은 값의 출력 커패시턴스는 부하 과도 상태 동안 피크 출력 편차를 감소시킬 수 있다.

병렬 디바이스의 이점

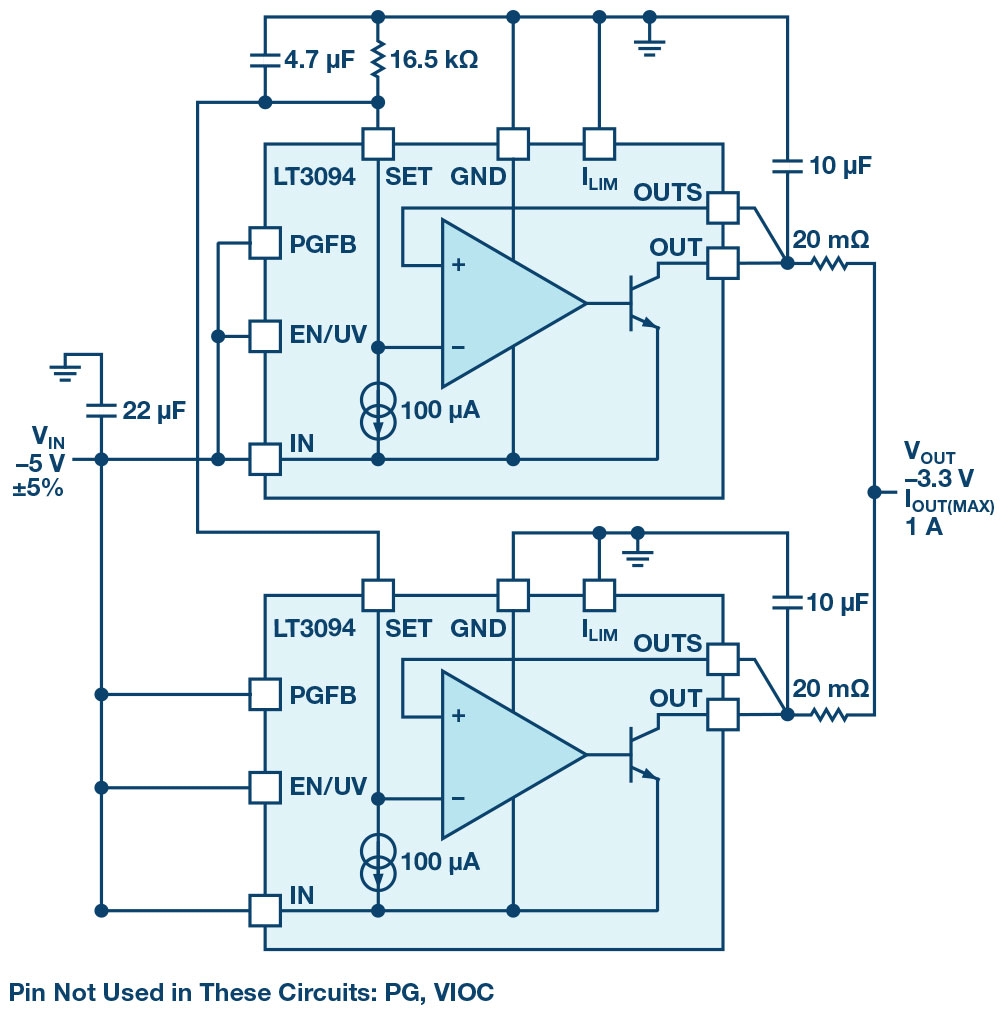

여러 개의 LT3094를 병렬 연결하면 더 높은 출력 전류를 얻을 수 있다. 이를 달성하려면 모든 SET 핀을 함께 연결하고 모든 IN 핀을 함께 연결하면 된다. 짧은 PCB 트레이스(밸러스트 저항으로 사용)를 사용하여 OUT 핀을 한데 연결하여 LT3094에서 전류를 균등화 한다. 2개 이상의 LT3094를 병렬로 연결하여 심지어 더 높은 전류와 더 낮은 출력 잡음을 생성할 수 있다. 출력 잡음 감소는 병렬 연결되는 디바이스 수의 제곱근에 비례한다. 여러 개의 LT3094를 병렬로 연결하면 PCB에서 열을 분산시키는 데도 유용하다. 입력-출력 전압 차가 높은 애플리케이션에서는 LT3094와 병렬로 입력 직렬 저항 또는 저항을 사용해서도 열을 분산시킬 수 있다. 그림 4는 병렬 회로 구현을 보여준다.

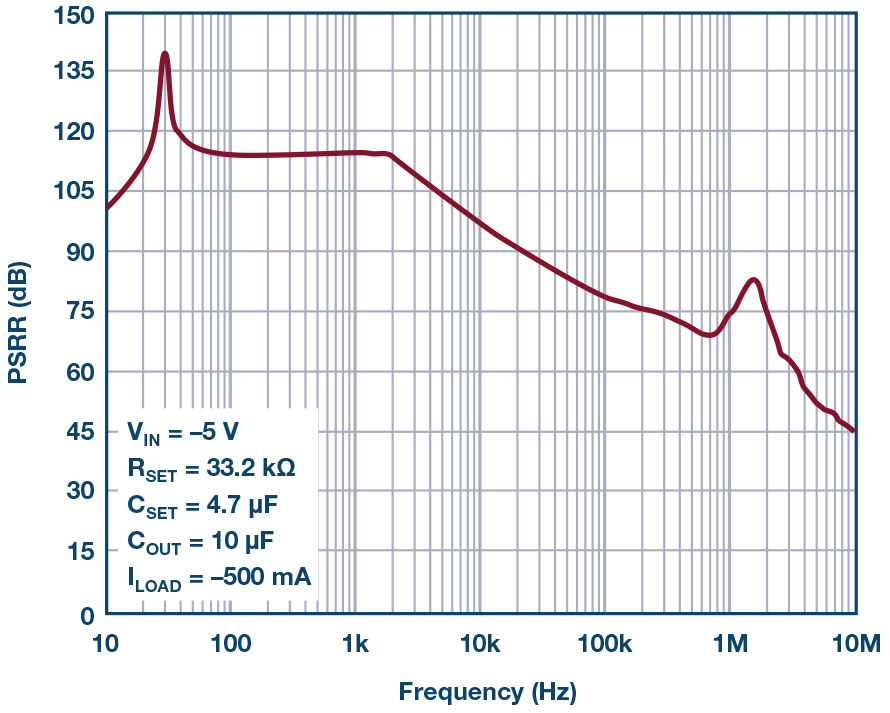

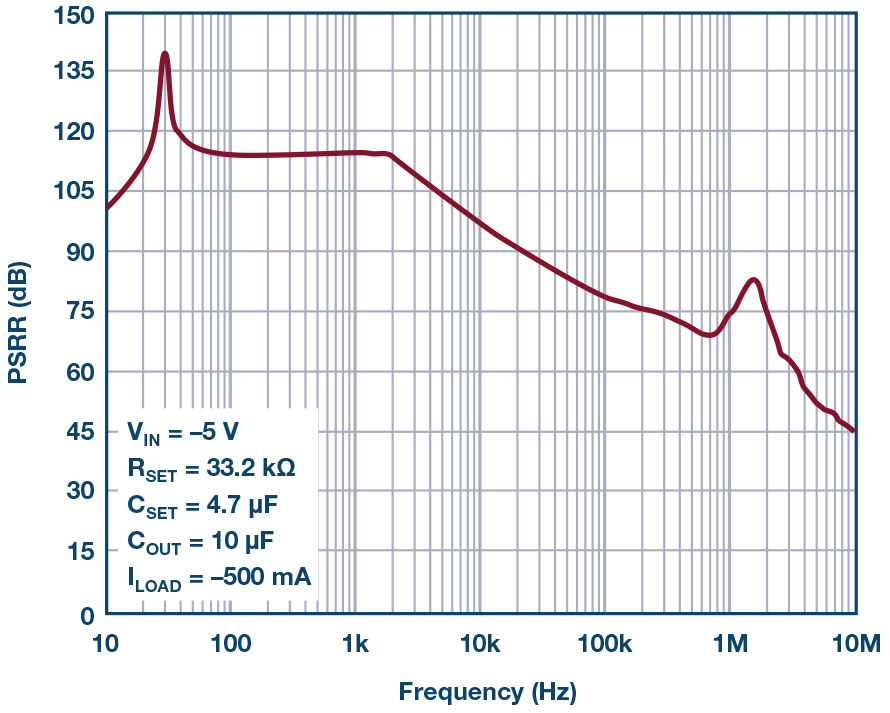

그림 2. LT3094 PSRR 성능

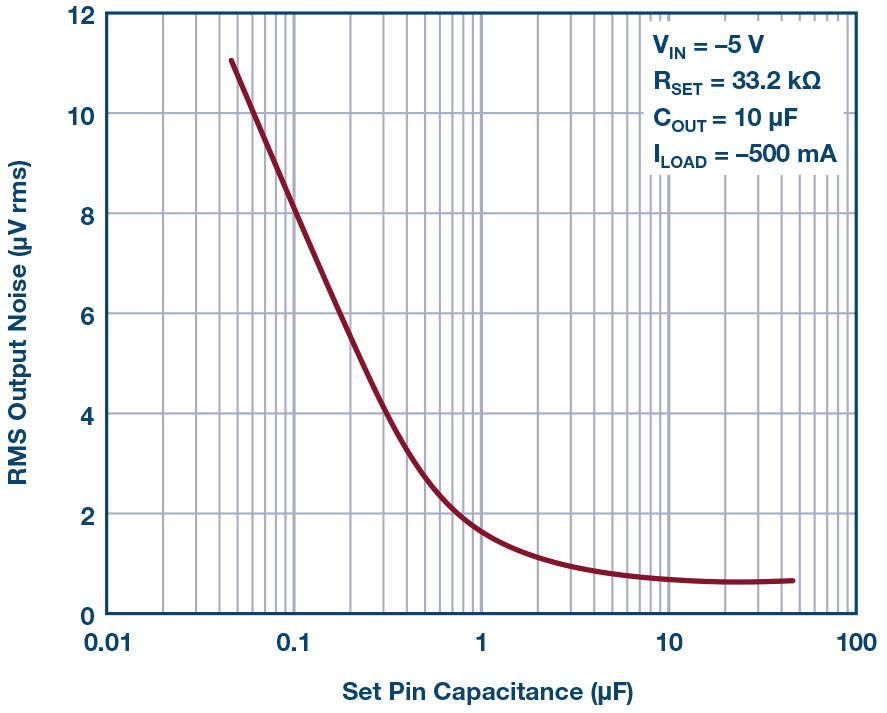

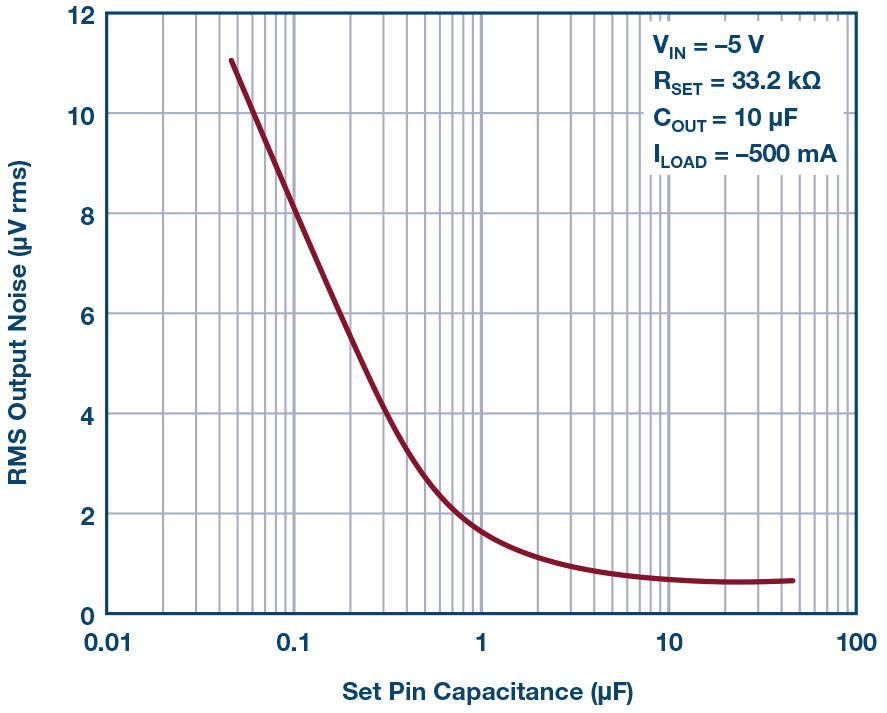

그림 3. LT3094 출력 잡음 성능

그림 4. LT3094 병렬 동작

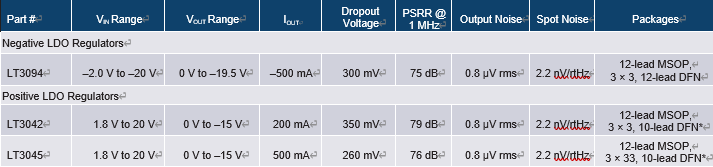

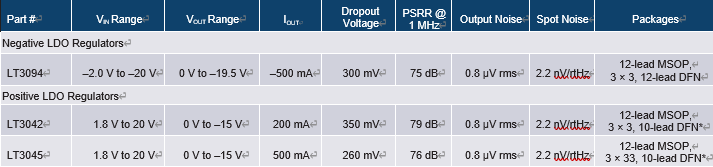

표 1은 ADI의 매우 높은 PSRR, 초저잡음 LDO 레귤레이터 제품군의 제품들을 보여준다.

표 1. 매우 높은 PSRR, 초저잡음 LDO 레귤레이터

*핀 호환 가능

결론

포지티브 200mA LT3042, 500mA LT3045 및 최근 출시된 새로운 보완적인 LT3094 네거티브 500mA LDO는 혁신적인 잡음 성능과 PSRR 성능을 제공한다. 이들 제품은 이러한 특성과 넓은 전압 범위, 저전압 강하, 광범위한 보호 기능/견고성, 사용 용이성 등을 결합함으로써 시험 및 계측 장비 또는 의료용 이미징 시스템 등에서 잡음에 민감한 양극성 양/음의 레일에 전력을 공급하는 데 이상적이다. 전류 레퍼런스 기반 아키텍처를 채택하여 잡음과 PSRR 성능은 출력 전압과 관계없이 일정하게 유지된다. 또한 여러 개의 디바이스를 직접 병렬 연결하여 출력 잡음을 추가로 감소시키고, 출력 전류를 높이고, PCB 보드에서 열을 분산시킬 수 있다. LT3042, LT3045, LT3094는 시간과 비용을 절감하면서 애플리케이션 성능을 향상시킨다.

글쓴이

스티브 노스(Steve Knoth)는 아나로그디바이스의 Power by Linear Group 수석 제품 마케팅 엔지니어이다. 모든 전력 관리 IC(PMIC) 제품, LDO 레귤레이터, 배터리 차저, 차지 펌프, 차지 펌프 기반 LED 드라이버, 수퍼커패시터 차저, 저전압 모노리식 스위칭 레귤레이터 및 아이디얼 다이오드 디바이스를 담당하고 있다. 2004년 리니어테크놀로지(현 ADI)에 합류하기 전 1990년부터 마이크로파워시스템(Micro Power Systems), 아나로그디바이스(Analog Devices), 마이크렐반도체(Micrel Semiconductor)에서 다양한 마케팅 및 제품 엔지니어링 직책을 거쳤다. 산호세 주립대학에서 1988년에 전기공학 학사학위를, 1995년에 물리학 석사학위를 받았다. 2000년에는 피닉스대학에서 기술 경영학 MBA를 받았다. 자녀와 함께 시간을 보내는 것 외에도 핀볼, 아케이드 게임이나 머슬카를 다루고 빈티지 토이, 영화, 스포츠, 자동차 기념품을 수집하는 것이 취미이다(연락처 steve.knoth@analog.com).

이러한 요구를 충족하기 위해 아나로그디바이스(Analog Devices)는 매우 높은 PSRR, 초저잡음의 포지티브 LDO 레귤레이터 LT304x 제품군을 출시했다. 가장 최근 출시된 제품은 보완적인 LT3094로, 초저잡음 매우 높은 PSRR의 저전압 강하 500mA 네거티브 선형 레귤레이터이다. 이 디바이스는 인기 있는 500mA LT3045(200mA의 경우 LT3042)의 네거티브 버전이다. LT3094의 고유한 설계는 10kHz일 때 단 2nV/√Hz의 초저 스폿 잡음과 10Hz ~ 100kHz의 넓은 대역폭에서 0.85µVrms의 적분 출력 잡음을 달성한다. PSRR 성능은 유례없는 수준으로, 저주파 PSRR은 거의 4kHz까지 100dB를 넘고, 고주파 PSRR은 2MHz까지 70dB를 넘는다. 따라서 잡음이 있거나 높은 리플의 입력 전원을 조용하고 깨끗하게 유지할 수 있다. LT3094는 정밀 전류 소스 레퍼런스에 이어 고성능 단위 이득 버퍼로 구성된 고유의 LDO 아키텍처를 채택함으로써 출력 전압과 관계없이 거의 일정한 대역폭, 잡음, PSRR, 부하 레귤레이션 성능을 제공한다. 또한 이 아키텍처는 여러 개의 LT3094를 병렬 연결하여 잡음을 추가로 감소시키고, 출력 전류를 높이고, PCB에서 열을 분산시킬 수 있게 한다.

LT3094는 –2V ~ –20V의 넓은 입력 전압 범위에 걸쳐 전체 부하에서 230mV 강하 전압으로 최대 500mA 출력 전류를 제공한다. 출력 전압 범위는 0V ~ –19.5V이고, 출력 전압 허용오차는 라인, 부하 및 온도에서 ±2%로 매우 정확하다. 디바이스의 넓은 입력 및 출력 전압 범위, 높은 대역폭, 높은 PSRR 및 매우 낮은 잡음 성능은 PLL/VCO/믹서/LNA, 그리고 시험 및 계측과 같은 초저잡음 계측, 고속/고정밀 데이터 컨버터 및 이미징, 진단과 같은 의료용 애플리케이션, 정밀 전원 및 스위칭 전원을 위한 포스트 레귤레이터와 같은 잡음에 민감한 애플리케이션에 전력을 공급하는 데 이상적이다.

LT3094는 소형의 저가 10µF 세라믹 출력 커패시터로 동작하여 안정성 및 과도 응답을 최적화한다. 단일 저항으로 외부 정밀 전류 제한(전체 온도 범위에서 최대 ±10% 오차)을 프로그래밍할 수 있다. 디바이스의 VIOC 핀은 앞 단의 레귤레이터(LT3094로 전원을 공급하는 스위칭 레귤레이터)를 제어하여 전력 소모를 최소화하고 PSRR을 최적화한다. 단일 SET 핀 커패시터는 출력 잡음을 낮추고 레퍼런스 소프트 스타트 기능을 제공함으로써 턴온 시 출력 전압 오버슛을 방지한다. 또한 디바이스의 내부 보호 회로는 폴드백을 이용한 내부 전류 제한, 히스테리시스를 이용한 열 제한을 포함한다. 그 밖의 기능으로는 빠른 스타트업 기능(큰 값의 SET 핀 커패시터를 사용할 때 유용) 및 출력 전압 레귤레이션을 표시하는 프로그래밍 가능한 임계값을 갖는 Power Good 플래그(이 기능을 탑재한 업계 최초 네거티브 LDO 레귤레이터) 등이 있다.

LT3094는 열 성능 강화된 12핀, 3mm × 3mm DFN 및 MSOP 패키지로 제공되며, 모두 초소형 풋프린트를 달성한다. 현재 –40°C ~ +125°C 동작 접합부 온도의 E 및 I 등급 버전을 구매할 수 있다.

그림 1. LT3094 일반적인 애플리케이션 회로도 및 특징

LT3094는 안정성을 위해 출력 커패시터를 필요로 한다. 높은 대역폭을 고려하여 낮은 ESR 및 ESL의 세라믹 커패시터를 사용할 것을 권장한다. 안정성을 위해서는 ESR이 30mΩ 미만, ESL이 1.5nH 미만이면서 최소 10µF 출력 커패시턴스가 필요하다. 단일 10µF 세라믹 출력 커패시터를 사용하여 높은 PSRR 및 저잡음 성능을 달성하므로 이보다 높은 값의 출력 커패시터를 사용해도 성능을 조금밖에는 향상시키지 못한다. 출력 커패시턴스가 증가함에 따라 레귤레이터 대역폭이 감소하기 때문인데, 이 상충관계에 따라 최소 10µF 출력 커패시터보다 높은 값을 사용하더라도 얻을 수 있는 성능은 거의 없다. 그렇지만, 더 높은 값의 출력 커패시턴스는 부하 과도 상태 동안 피크 출력 편차를 감소시킬 수 있다.

병렬 디바이스의 이점

여러 개의 LT3094를 병렬 연결하면 더 높은 출력 전류를 얻을 수 있다. 이를 달성하려면 모든 SET 핀을 함께 연결하고 모든 IN 핀을 함께 연결하면 된다. 짧은 PCB 트레이스(밸러스트 저항으로 사용)를 사용하여 OUT 핀을 한데 연결하여 LT3094에서 전류를 균등화 한다. 2개 이상의 LT3094를 병렬로 연결하여 심지어 더 높은 전류와 더 낮은 출력 잡음을 생성할 수 있다. 출력 잡음 감소는 병렬 연결되는 디바이스 수의 제곱근에 비례한다. 여러 개의 LT3094를 병렬로 연결하면 PCB에서 열을 분산시키는 데도 유용하다. 입력-출력 전압 차가 높은 애플리케이션에서는 LT3094와 병렬로 입력 직렬 저항 또는 저항을 사용해서도 열을 분산시킬 수 있다. 그림 4는 병렬 회로 구현을 보여준다.

그림 2. LT3094 PSRR 성능

그림 3. LT3094 출력 잡음 성능

그림 4. LT3094 병렬 동작

표 1은 ADI의 매우 높은 PSRR, 초저잡음 LDO 레귤레이터 제품군의 제품들을 보여준다.

표 1. 매우 높은 PSRR, 초저잡음 LDO 레귤레이터

*핀 호환 가능

결론

포지티브 200mA LT3042, 500mA LT3045 및 최근 출시된 새로운 보완적인 LT3094 네거티브 500mA LDO는 혁신적인 잡음 성능과 PSRR 성능을 제공한다. 이들 제품은 이러한 특성과 넓은 전압 범위, 저전압 강하, 광범위한 보호 기능/견고성, 사용 용이성 등을 결합함으로써 시험 및 계측 장비 또는 의료용 이미징 시스템 등에서 잡음에 민감한 양극성 양/음의 레일에 전력을 공급하는 데 이상적이다. 전류 레퍼런스 기반 아키텍처를 채택하여 잡음과 PSRR 성능은 출력 전압과 관계없이 일정하게 유지된다. 또한 여러 개의 디바이스를 직접 병렬 연결하여 출력 잡음을 추가로 감소시키고, 출력 전류를 높이고, PCB 보드에서 열을 분산시킬 수 있다. LT3042, LT3045, LT3094는 시간과 비용을 절감하면서 애플리케이션 성능을 향상시킨다.

글쓴이

스티브 노스(Steve Knoth)는 아나로그디바이스의 Power by Linear Group 수석 제품 마케팅 엔지니어이다. 모든 전력 관리 IC(PMIC) 제품, LDO 레귤레이터, 배터리 차저, 차지 펌프, 차지 펌프 기반 LED 드라이버, 수퍼커패시터 차저, 저전압 모노리식 스위칭 레귤레이터 및 아이디얼 다이오드 디바이스를 담당하고 있다. 2004년 리니어테크놀로지(현 ADI)에 합류하기 전 1990년부터 마이크로파워시스템(Micro Power Systems), 아나로그디바이스(Analog Devices), 마이크렐반도체(Micrel Semiconductor)에서 다양한 마케팅 및 제품 엔지니어링 직책을 거쳤다. 산호세 주립대학에서 1988년에 전기공학 학사학위를, 1995년에 물리학 석사학위를 받았다. 2000년에는 피닉스대학에서 기술 경영학 MBA를 받았다. 자녀와 함께 시간을 보내는 것 외에도 핀볼, 아케이드 게임이나 머슬카를 다루고 빈티지 토이, 영화, 스포츠, 자동차 기념품을 수집하는 것이 취미이다(연락처 steve.knoth@analog.com).

제품스펙

바로가기>