기술기고문

외부 LO를 사용할 때 트랜시버 위상 잡음 예측 기법

글: 피터 딜로스(Peter Delos) 테크니컬 디렉터 / 아나로그디바이스(Analog Devices, Inc.)

요약

소프트웨어 정의 무선(SDR)은 오늘날 업계에서 주목하고 있는 기술 중 하나이다. 소프트웨어 정의 무선 기술은 최근 포괄적인 무선 솔루션을 모놀리식 IC로 제공하는 RF 트랜시버가 출시됨으로써 더욱 활성화할 수 있게 되었다. 아나로그디바이스(Analog Devices)의 트랜시버 제품이 바로 그러한 IC 중 하나인데, 이 제품은 전적으로 소프트웨어에 의해 제어되는 많은 무선 시스템 설계에 채택되고 있다. 이러한 디바이스를 낮은 위상 잡음이 요구되는 애플리케이션에 사용하고자 할 때 주의할 부분이 있다. 이 글에서는 외부 주파수 소스가 제공되는 애플리케이션에 이처럼 높은 통합 수준의 RFIC를 사용할 때의 위상 잡음 성능에 대해서 살펴본다.

외부 로컬 오실레이터(LO)를 사용할 때의 아나로그디바이스 ADRV9009 트랜시버에 대한 측정 결과를 살펴보면, 저잡음 LO를 사용함으로써 위상 잡음 특성을 크게 향상시킬 수 있다는 것을 알 수 있다. 따라서 이 트랜시버 아키텍처를 위상 잡음에 대한 기여도 관점에서 살펴볼 수 있다. 일련의 측정을 통해서 DAC 출력 주파수 설정에 따른 잔류 및 추가 위상 잡음을 도출할 수 있다. 이 잡음과 함께 입력 주파수(LO 및 레퍼런스) 위상 잡음을 분석함으로써, 송신 출력에서 총 위상 잡음을 예측할 수 있다. 이러한 예측 값을 실제 측정 결과와 비교한다.

머리말

위상 잡음은 무선 설계에서 신호 품질을 나타내는 중요한 지표 중의 하나이다. 아키텍처 개발 단계에서는 위상 잡음 요구 사항을 가능한 가장 경제적인 방법으로 충족하기 위해 많은 공을 쏟는다.

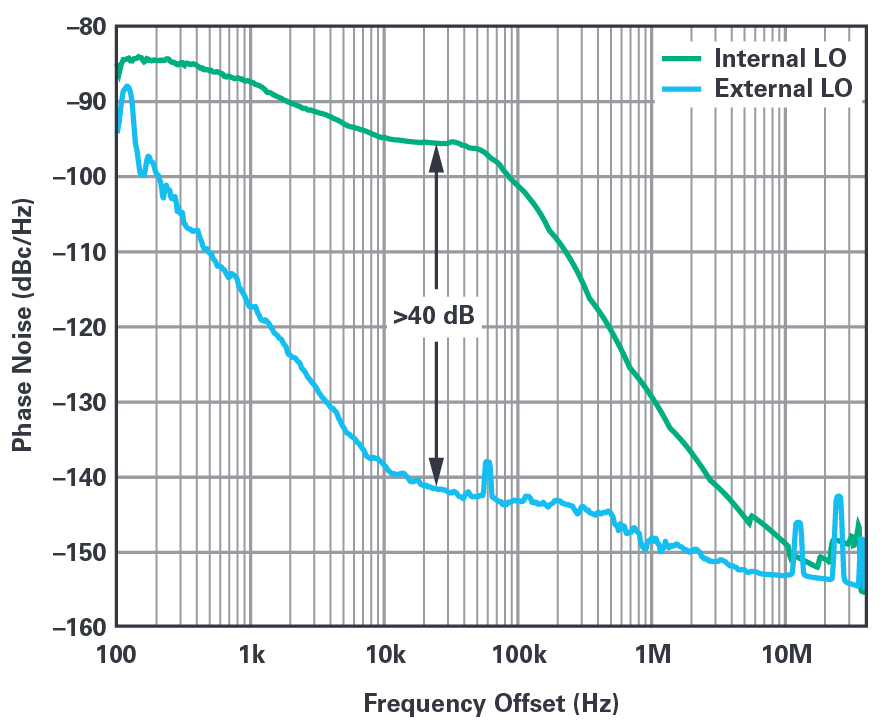

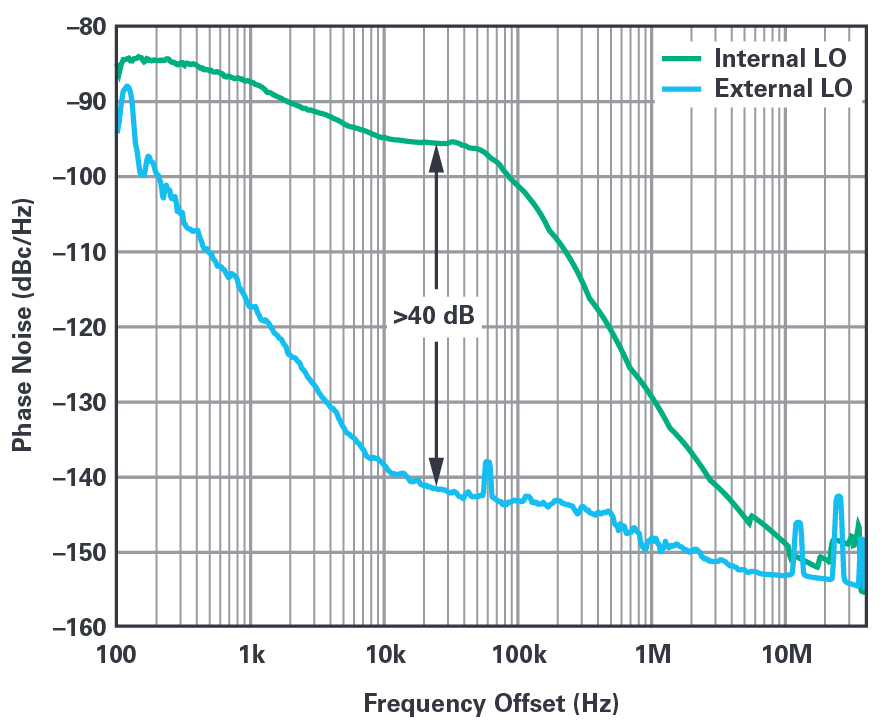

ADRV9009 트랜시버에 대한 측정 결과를 보면, 어떤 구현 방법을 선택했는가에 따라서 잡음 성능을 개선할 수 있는 여지가 크다는 것을 알 수 있다. 내부 LO 기능을 사용하면 IC 기반의 내부 위상 동기 루프(PLL)와 전압 제어 오실레이터(VCO)에 따라서 위상 잡음이 결정된다. 내부 LO는 최대한 다양한 통신 애플리케이션을 충족하도록 설계된다. 따라서 향상된 위상 잡음 성능을 요구하는 애플리케이션에서는, 위상 잡음이 낮은 외부 LO를 사용함으로써 위상 잡음 특성을 크게 향상시킬 수 있다.

그림 1: ADRV9009 트랜시버의 위상 잡음 측정 결과. 내부 LO 기능을 사용하면 PLL/VCO에 의해서 위상 잡음이 결정된다. 위상 잡음이 낮은 외부 LO를 사용함으로써 위상 잡음을 크게 향상시킬 수 있다.

그림 1은 ADRV9009 트랜시버로 10kHz ~ 100kHz 오프셋에 걸쳐서 위상 잡음을 40dB 이상 향상시킬 수 있다는 것을 보여준다. 이 측정을 할 때의 조건은 다음과 같다. 내부 LO 측정을 위해서는 LO 주파수를 2.6GHz로 설정했으며 DAC 출력은 8MHz였다. 외부 LO 측정을 위해서는 LO 소스로서 로데슈바르즈(Rohde & Schwarz)의 SMA100B를 사용했다. LO 경로 상에 내부 주파수 분주기가 존재하기 때문에, 2.6GHz의 LO 주파수를 위해 생성기를 5.2GHz로 설정했다. 측정은 홀츠워스(Holzworth)의 HA7402 위상 잡음 분석기로 수행했다.

ADRV9009 트랜시버

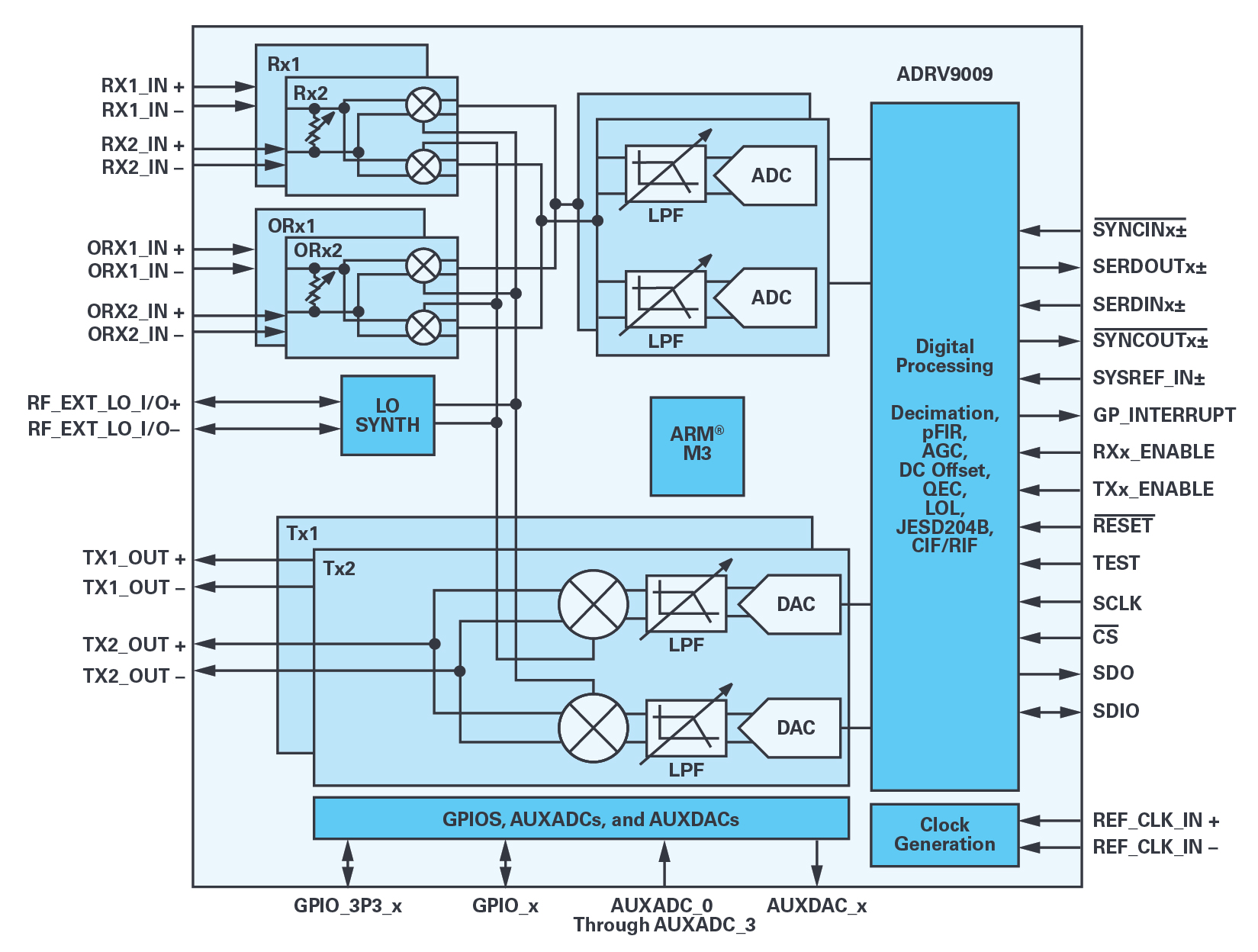

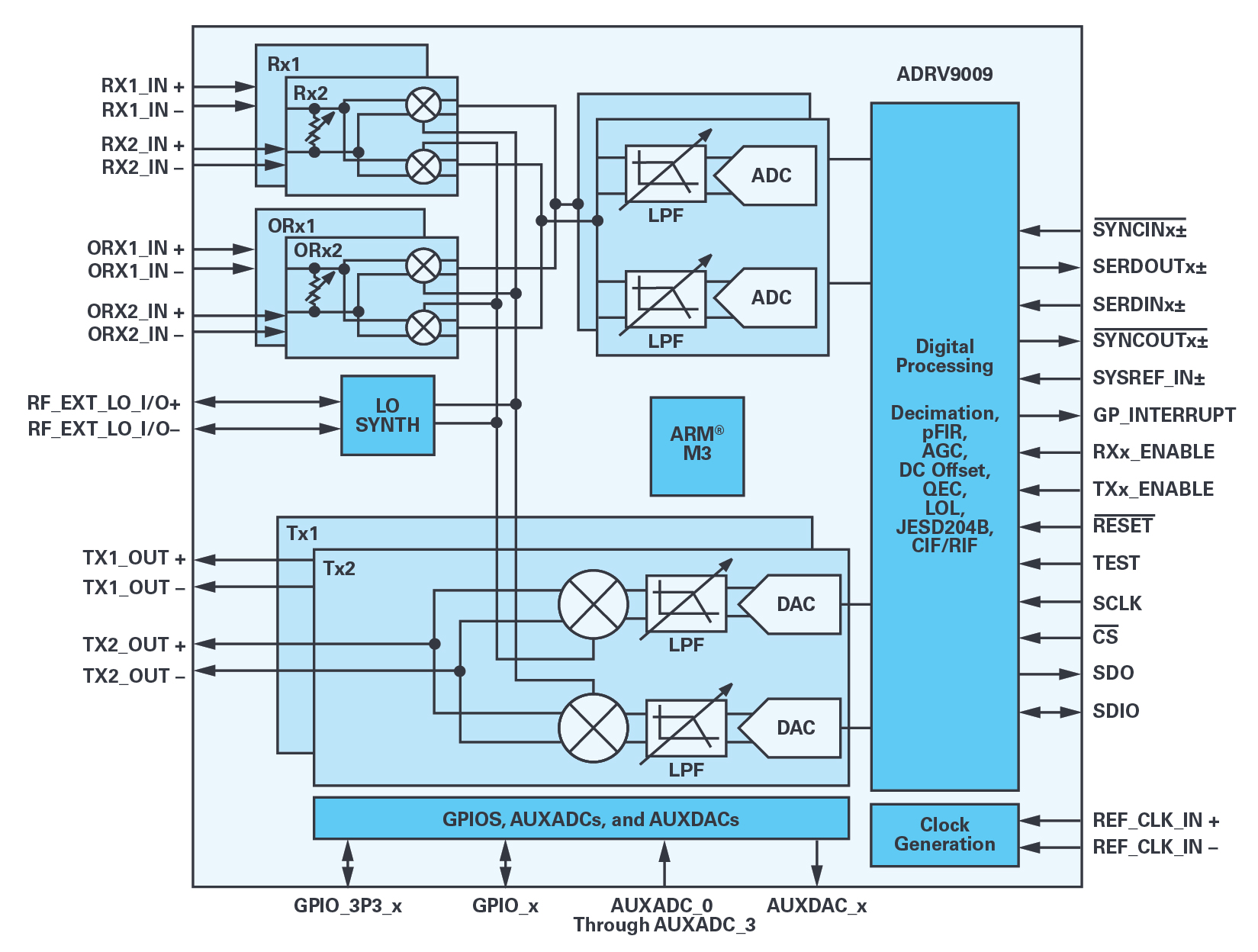

ADRV9009는 아나로그디바이스의 트랜시버 제품군에 가장 최근에 추가된 제품이다. 그림 2는 이 트랜시버 아키텍처를 나타낸 것이다. 이 트랜시버 제품은 송신과 수신 기능을 모두 지원하는 듀얼 채널 무선 기능의 모놀리식 IC로서, 직접 변환 아키텍처로 구현되었다. 이 디지털 프로세싱은 직교 위상 오류 교정, dc 오프셋, LO 누설 알고리즘을 포함함으로써, 기존에는 직접 변환 아키텍처로 달성해왔던 성능들을 구현할 수 있게 해준다. 또한 이 트랜시버는 완벽한 RF 대 디지털 기능을 제공한다. 6GHz에 이르는 RF 주파수를 지원하며, JESD204B 인터페이스는 ASIC 또는 FPGA 기반 프로세서에 대한 고속 데이터 인터페이스를 제공한다.

그림 2: ADRV9009 트랜시버의 기능 블록 다이어그램

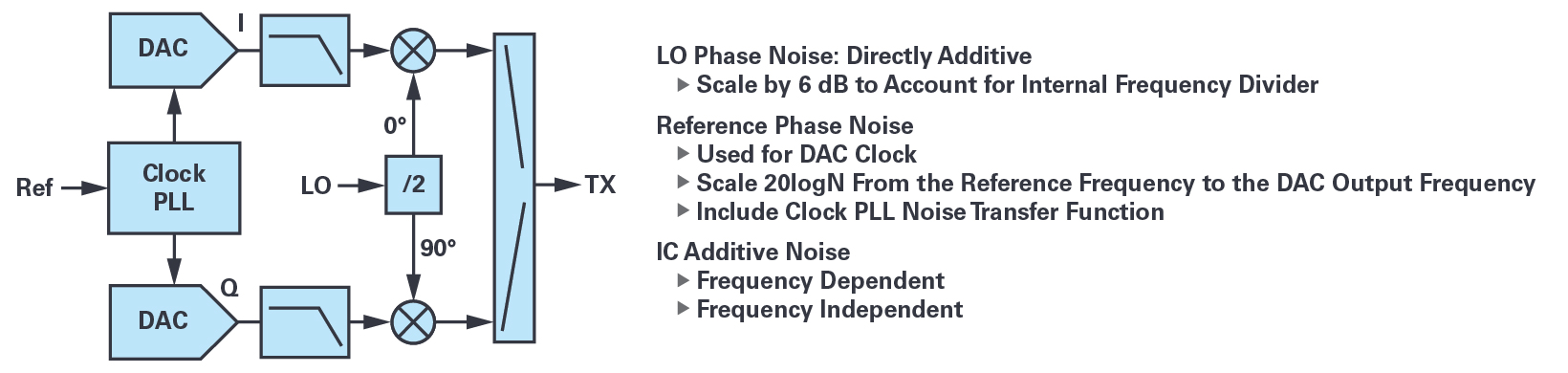

그림 3: 직접 상향변환 블록 다이어그램과 위상 잡음 요인들

이 무선 디바이스는 레퍼런스 주파수 입력에 동기화된다. 다수의 PLL 위상을 컨버터 클럭, LO, 디지털 클럭 등의 레퍼런스에 동기화한다. 외부 LO를 사용하면 내부 LO PLL을 바이패스 할 수 있다. LO 경로 상에는 PLL 또는 외부 LO 입력과 믹서 포트 사이에 주파수 분주기가 존재한다. 이 분주기를 사용해서 직접 변환 아키텍처에 필요한 직교 위상 LO 신호를 생성한다. 컨버터 클럭과 LO가 위상 잡음에 직접적인 영향을 미치는데, 이에 대해서는 뒤에서 위상 잡음 요인에 대해서 다루면서 더 알아보기로 한다.

위상 잡음 요인

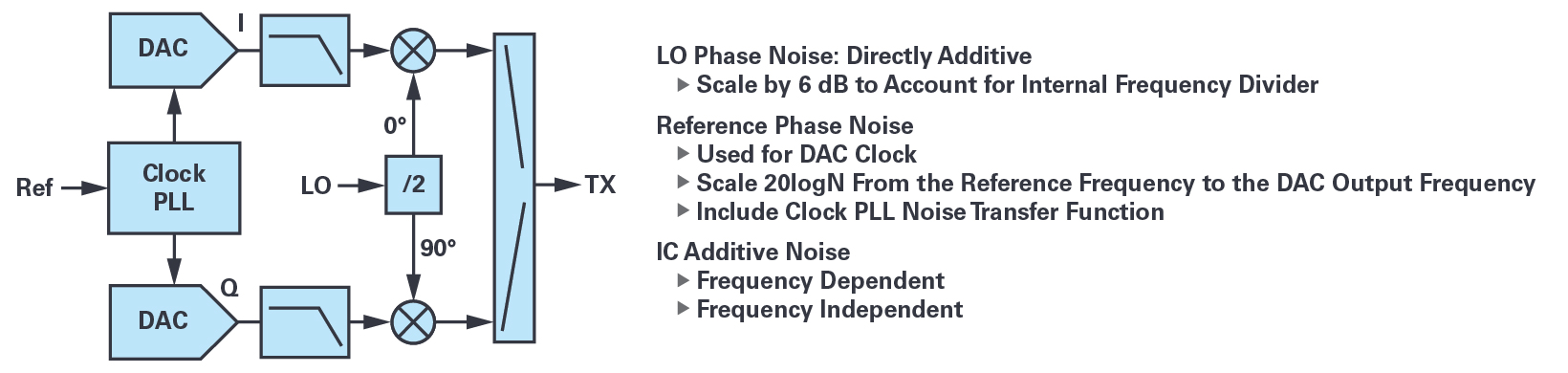

송신 출력에서 위상 잡음은 여러 요인들로 이루어진다. 그림 3은 직접 변환 파형 생성기 아키텍처의 블록 다이어그램과 주요 위상 잡음 요인들을 보여준다.

트랜시버 위상 잡음 분석에 앞서 몇 가지 기초적인 원리들을 살펴보자. 주파수 체배기나 분주기에서 위상 잡음은 20logN으로 변화한다. 여기서 N은 입력 대 출력 주파수의 비율이다. 이것은 직접 디지털 합성기(DDS)도 마찬가지다. 이 경우에는 클럭 잡음이 DDS 출력 주파수에 따라서 20logN으로 변화한다. 두 번째로 고려해야 할 것은 PLL의 위상 잡음 전달 함수이다. PLL로 주입된 레퍼런스 주파수는 (체배기와 마찬가지로) 출력으로 주파수 비의 함수로서 변화할 뿐만 아니라, 루프 대역폭(BW)과 선택한 루프 필터 타입에 따라서 저역통과 필터의 효과를 나타낸다.

이러한 점들을 감안했을 때 트랜시버로 다양한 요인들이 작용한다는 것을 알 수 있다. 트랜시버로 LO 주파수와 레퍼런스 주파수의 두 가지 주파수가 주입된다. LO 주파수는 위상 잡음 출력에 직접적으로 영향을 미치는데, 직교 위상 LO 신호를 생성하는데 사용되는 내부 주파수 분주기에서 6dB 감소한다. 레퍼런스 주파수로 인한 잡음은 다양한 요인들로 인해 결정된다. 이는 클럭 PLL에서 DAC 클럭을 생성하는 데 사용된다. 레퍼런스 주파수로 인한 클럭 출력 상의 잡음은 PLL의 잡음 전달 함수에 따라서 변화한다. 그런 다음 이 잡음은 다시 DAC 클럭 대 DAC 출력 주파수 비에 따라서 변화한다. 이 같은 효과는 PLL 대역폭에 따른 저역통과 전달 함수를 사용해서 레퍼런스 주파수에서 DAC 출력 주파수로 스케일링하는 것으로 단순화할 수 있다.

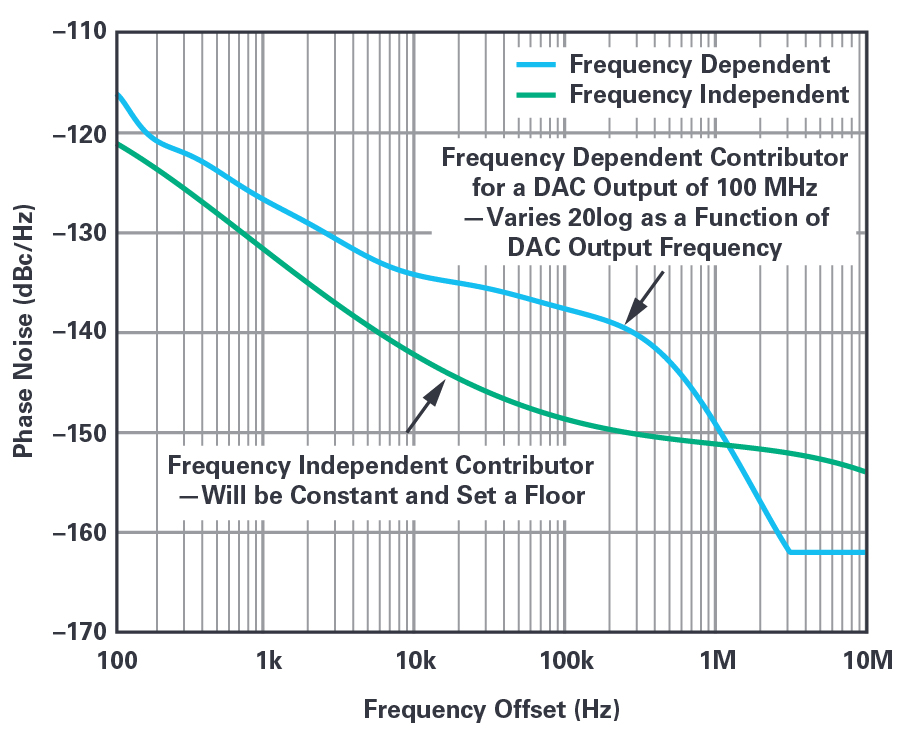

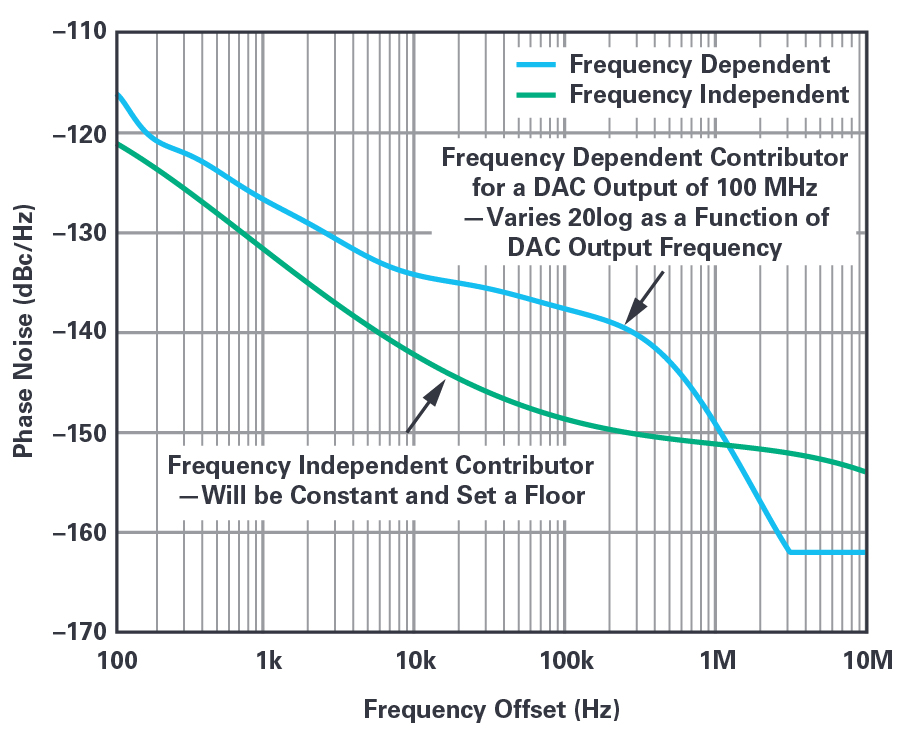

다음으로, 트랜시버 IC 위상 잡음을 살펴보자. 송신 경로 상의 모든 회로 소자들로부터 더해지는 잔류 잡음이 존재한다. IC 잡음 요인 중의 하나는 DAC 출력에서 첨가되는 잡음인데, 이것은 DAC 출력 주파수에 따라서 달라진다. 이 잡음은 다시 두 가지 잔류 위상 잡음으로 요약할 수 있다. 주파수 종속적 잡음과 주파수 독립적 잡음이 그것이다. 주파수 종속적 잡음은 DAC 출력 주파수에 따라서 20logN으로 변화한다. 주파수 독립적 잡음은 고정적이며, 트랜시버 IC의 위상 잡음 플로어를 결정한다.

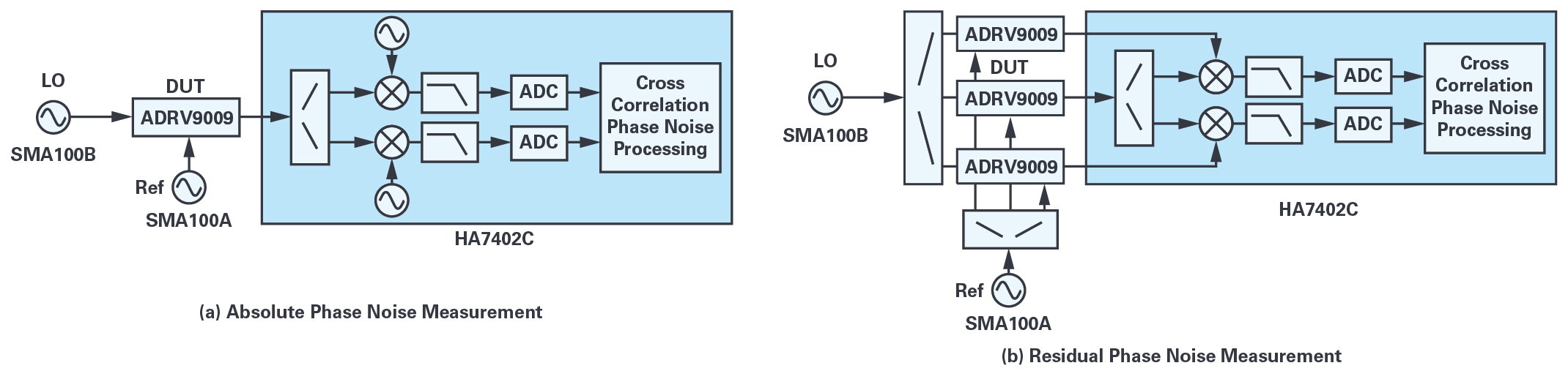

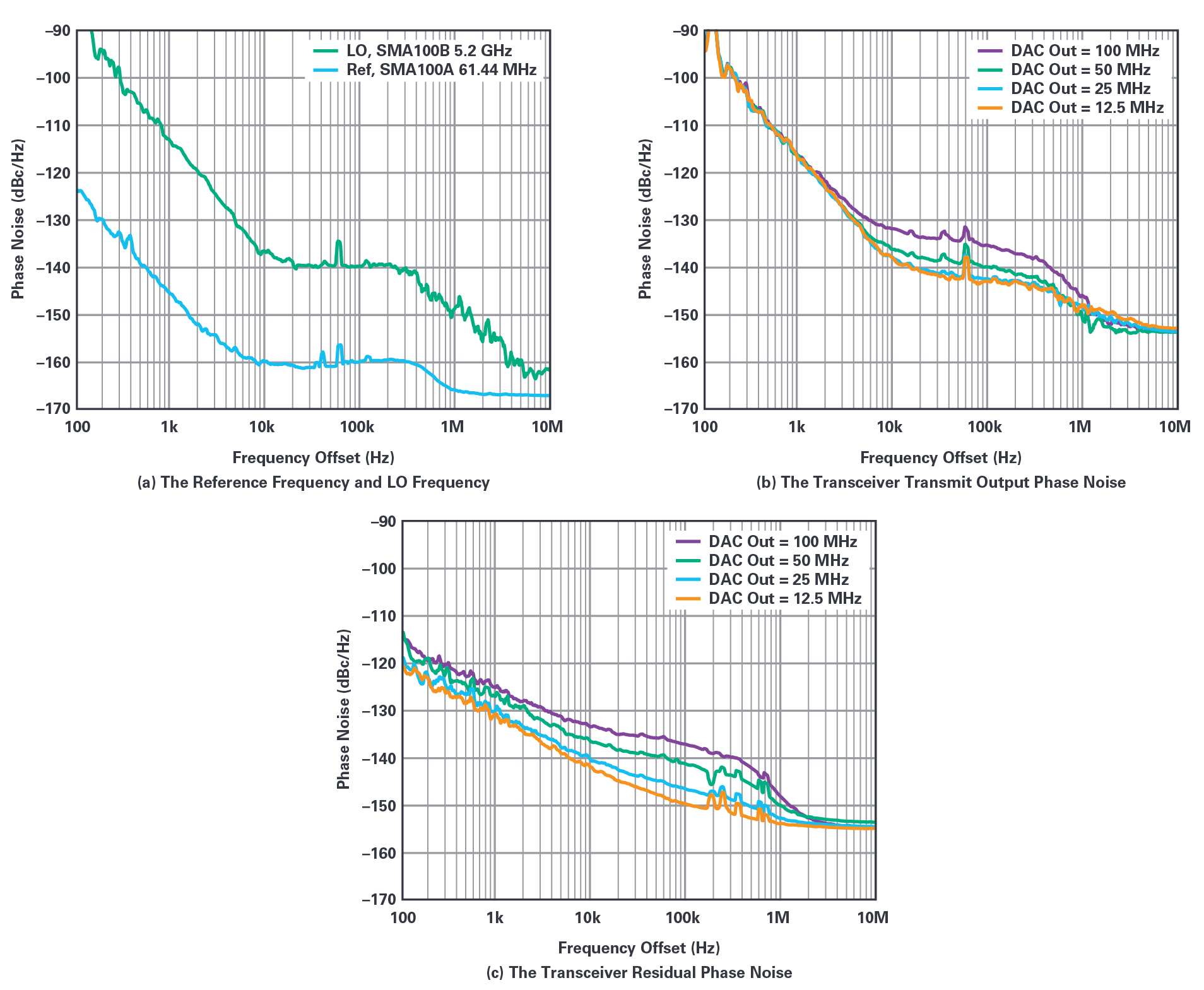

그림 4: 다양한 위상 잡음 요인들을 추출하기 위해서 사용된 위상 잡음 측정

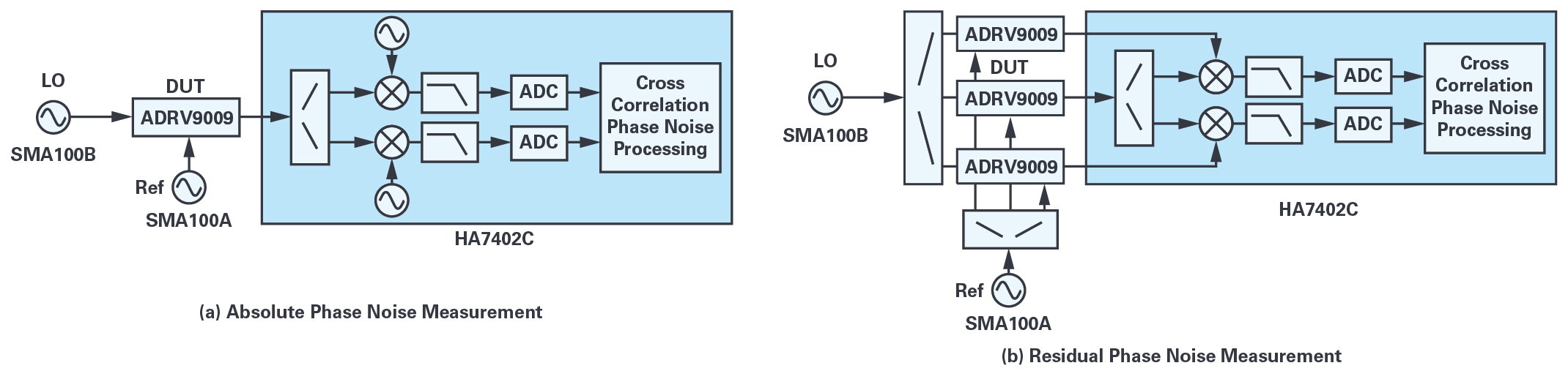

그림 5: 위상 잡음 측정에 사용된 테스트 셋업

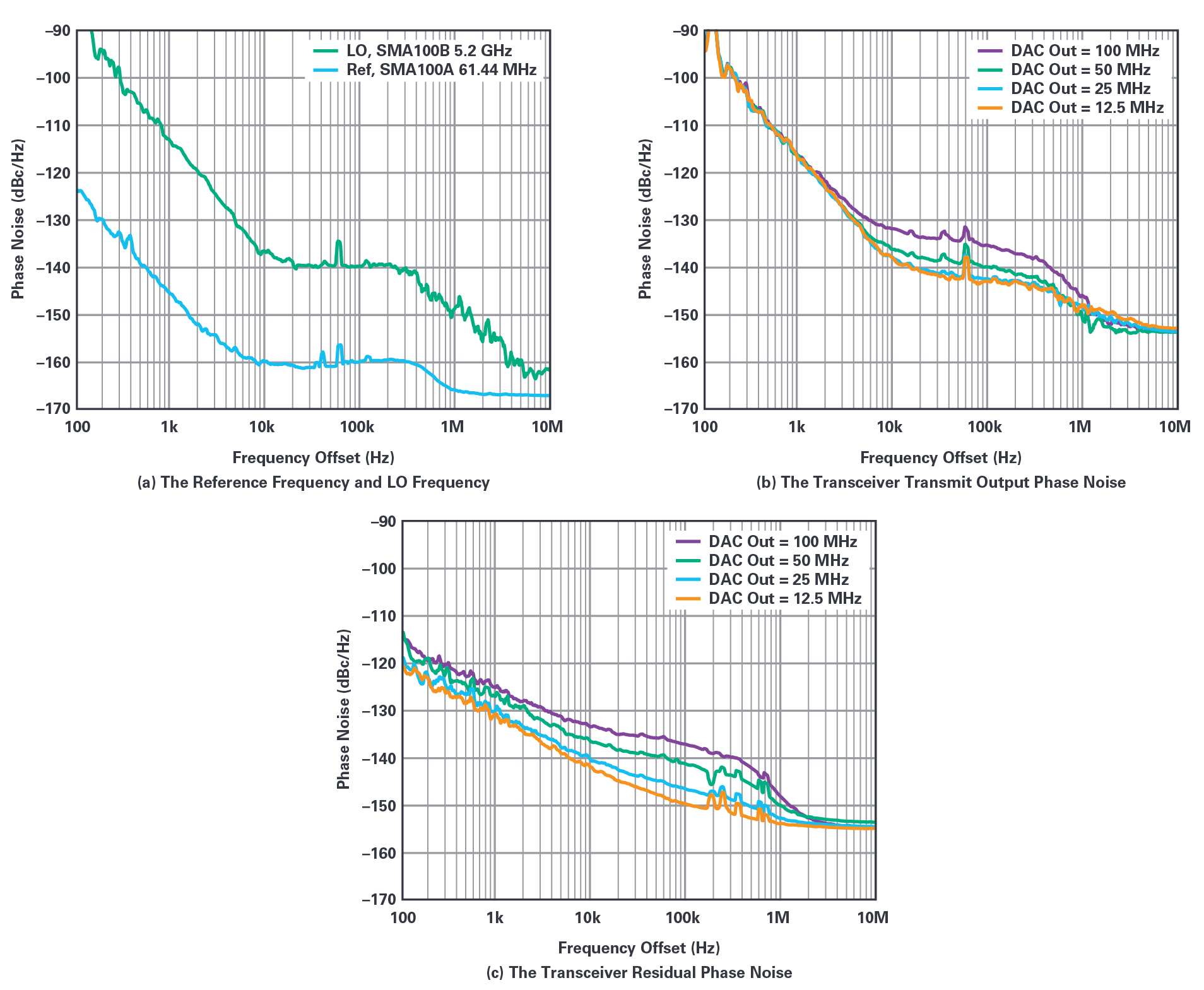

주파수 종속적 및 주파수 독립적 잡음의 함수로서 IC 잔류 잡음을 추출하기 위해, 그림 4에서 보는 것과 같이 일련의 위상 잡음 측정을 실시했다.

그림 5는 위상 잡음 측정에 사용된 테스트 셋업을 보여준다. 트랜시버 LO 및 레퍼런스 주파수 입력으로는 각각 로데슈바르즈의 SMA100B와 100A를 사용했으며, 위상 잡음 테스트 세트로는 홀츠워스의 HA7402C를 사용했다. 절대 위상 잡음 측정을 위해서 테스트 세트에 트랜시버의 송신 출력을 주입한다. 잔류 위상 잡음 측정을 위해서는 3개의 트랜시버가 필요하다. 추가적인 트랜시버들을 테스트 세트 믹서의 LO 포트로서 사용하면 측정으로부터 레퍼런스 주파수와 LO 주파수로 인한 잡음을 제거할 수 있다.

그림 4의 측정 데이터로부터 트랜시버 IC로 인한 주파수 종속적 및 주파수 독립적 위상 잡음을 추출했다. 그림 6은 이렇게 해서 계산된 것을 보여준다. 측정 데이터로 대입하고 1MHz 이상의 오프셋 주파수로 위상 잡음 플로어에 대해서 임계 설정을 적용해서 계산을 도출했다.

그림 7: 외부 LO를 사용할 때의 위상 잡음 측정 결과와 예측 결과 비교. 트랜시버 중심 주파수가 2.6GHz이기 때문에 LO를 5.2GHz로 설정했다. DAC 출력 주파수는 12.5MHz에서부터 100MHz까지 다양하게 변화시켰다. 예측 결과가 측정 결과와 일치하므로, 이 분석 기법을 다른 주파수로도 확장할 수 있다는 것을 알 수 있다.

동작 대역이 트랜시버의 순시 대역폭 이내인 위상 배열 시스템은 외부 LO가 단일 주파수일 수 있으며, 이 경우에는 위상 배열로 트랜시버에 외부 LO를 사용하는 것이 실용적인 방법일 수 있다. 시스템 위상 잡음을 평가할때 레퍼런스 주파수 잡음원이 LO 잡음원보다 훨씬 낮은 영향을 갖을 경우, 레퍼런스 주파수 소스 오실레이터를 선택할 수 있다. 공통 LO를 배열된 트랜시버들로 분배할 때는, 시스템에 코히어런트 하게 결합되는 트랜시버 수가 많아질수록 IC로 인한 잡음이 감소하고 외부 LO가 지배적이게 된다. 그러면 시스템 엔지니어링 잡음 분석을 간소화할 수 있다. 공통 LO가 대부분을 차지하는 잡음의 경우, 엔지니어링 시에 LO 설계의 가격대 성능비를 최적화하는 것에 초점을 맞출 수 있다.

맺음말

이 글에서는 외부 LO를 사용하고자 할 때 ADRV9009 트랜시버의 위상 잡음을 예측하기 위한 기법을 설명했다. 이 기법을 사용해서 DAC 출력 주파수에 따라 레퍼런스 오실레이터, LO 소스, 트랜시버로 인한 잡음을 추적할 수 있다. 측정 결과와 예측 결과가 거의 일치하므로, 다른 주파수 소스에 대해서도 이 기법을 적용하여 트랜시버의 성능을 예분석할 수 있다는 것을 알 수 있다. 또한 이 기법은 상당히 일반적으로 어느 파형 생성기 설계에도 똑같이 적용할 수 있다.

외부 LO 사용 시 측정한 위상 잡음 성능을 보면, 위상 잡음이 낮은 LO 소스를 사용해서 상당한 성능 향상을 거둘 수 있다는 것을 알 수 있다. 이 글의 목적은 시스템 설계 엔지니어들이 아키텍처를 검토하는 단계에서 다양한 선택을 할 수 있도록 돕기 위한 것이다. 낮은 위상 잡음을 요구하는 애플리케이션에서 이 트랜시버를 외부 LO 입력과 함께 사용하고자 하는 경우, 이 글에서 설명한 기법을 사용해서 다양한 조건으로 시스템 차원의 위상 잡음을 평가할 수 있다.

시스템 위상 잡음을 평가하기 위해서, 레퍼런스 주파수 잡음원이 LO 잡음원보다 훨씬 낮을 경우 레퍼런스 주파수 소스 오실레이터를 선택할 수 있다. 공통 LO를 일련의 트랜시버들로 분배할 때는, 시스템에 코히어런트 하게 결합되는 트랜시버 수가 많아질수록 IC로 인한 잡음이 감소하고 외부 LO가 지배적이게 된다. 그러면 시스템 엔지니어링 잡음 분석을 간소화할 수 있다. 공통 LO가 대부분을 차지하는 잡음의 경우, 엔지니어링 시에 LO 설계의 가격대 성능비를 최적화하는 것에 초점을 맞출 수 있다.

저자 소개

피터 딜로스(Peter Delos)는 미국 노스캐롤라이나주 그린즈버로에 위치한 아나로그디바이스(Analog Devices)의 항공 방위 그룹 테크니컬 디렉터이다. 1990년에 버지니아공대에서 BSEE를, 2004년에 NJIT에서 MSEE를 취득했으며, 25년 넘게 이 업계에 종사하고 있다. 아키텍처 레벨, PWB 레벨, IC 레벨의 첨단 RF/아날로그 시스템 설계를 주로 했다. 현재는 위상 배열 애플리케이션을 위한 고성능 리시버, 파형 생성기, 합성기 설계를 소형화하는 업무에 매진하고 있다. 문의: peter.delos@analog.com

요약

소프트웨어 정의 무선(SDR)은 오늘날 업계에서 주목하고 있는 기술 중 하나이다. 소프트웨어 정의 무선 기술은 최근 포괄적인 무선 솔루션을 모놀리식 IC로 제공하는 RF 트랜시버가 출시됨으로써 더욱 활성화할 수 있게 되었다. 아나로그디바이스(Analog Devices)의 트랜시버 제품이 바로 그러한 IC 중 하나인데, 이 제품은 전적으로 소프트웨어에 의해 제어되는 많은 무선 시스템 설계에 채택되고 있다. 이러한 디바이스를 낮은 위상 잡음이 요구되는 애플리케이션에 사용하고자 할 때 주의할 부분이 있다. 이 글에서는 외부 주파수 소스가 제공되는 애플리케이션에 이처럼 높은 통합 수준의 RFIC를 사용할 때의 위상 잡음 성능에 대해서 살펴본다.

외부 로컬 오실레이터(LO)를 사용할 때의 아나로그디바이스 ADRV9009 트랜시버에 대한 측정 결과를 살펴보면, 저잡음 LO를 사용함으로써 위상 잡음 특성을 크게 향상시킬 수 있다는 것을 알 수 있다. 따라서 이 트랜시버 아키텍처를 위상 잡음에 대한 기여도 관점에서 살펴볼 수 있다. 일련의 측정을 통해서 DAC 출력 주파수 설정에 따른 잔류 및 추가 위상 잡음을 도출할 수 있다. 이 잡음과 함께 입력 주파수(LO 및 레퍼런스) 위상 잡음을 분석함으로써, 송신 출력에서 총 위상 잡음을 예측할 수 있다. 이러한 예측 값을 실제 측정 결과와 비교한다.

머리말

위상 잡음은 무선 설계에서 신호 품질을 나타내는 중요한 지표 중의 하나이다. 아키텍처 개발 단계에서는 위상 잡음 요구 사항을 가능한 가장 경제적인 방법으로 충족하기 위해 많은 공을 쏟는다.

ADRV9009 트랜시버에 대한 측정 결과를 보면, 어떤 구현 방법을 선택했는가에 따라서 잡음 성능을 개선할 수 있는 여지가 크다는 것을 알 수 있다. 내부 LO 기능을 사용하면 IC 기반의 내부 위상 동기 루프(PLL)와 전압 제어 오실레이터(VCO)에 따라서 위상 잡음이 결정된다. 내부 LO는 최대한 다양한 통신 애플리케이션을 충족하도록 설계된다. 따라서 향상된 위상 잡음 성능을 요구하는 애플리케이션에서는, 위상 잡음이 낮은 외부 LO를 사용함으로써 위상 잡음 특성을 크게 향상시킬 수 있다.

그림 1: ADRV9009 트랜시버의 위상 잡음 측정 결과. 내부 LO 기능을 사용하면 PLL/VCO에 의해서 위상 잡음이 결정된다. 위상 잡음이 낮은 외부 LO를 사용함으로써 위상 잡음을 크게 향상시킬 수 있다.

그림 1은 ADRV9009 트랜시버로 10kHz ~ 100kHz 오프셋에 걸쳐서 위상 잡음을 40dB 이상 향상시킬 수 있다는 것을 보여준다. 이 측정을 할 때의 조건은 다음과 같다. 내부 LO 측정을 위해서는 LO 주파수를 2.6GHz로 설정했으며 DAC 출력은 8MHz였다. 외부 LO 측정을 위해서는 LO 소스로서 로데슈바르즈(Rohde & Schwarz)의 SMA100B를 사용했다. LO 경로 상에 내부 주파수 분주기가 존재하기 때문에, 2.6GHz의 LO 주파수를 위해 생성기를 5.2GHz로 설정했다. 측정은 홀츠워스(Holzworth)의 HA7402 위상 잡음 분석기로 수행했다.

ADRV9009 트랜시버

ADRV9009는 아나로그디바이스의 트랜시버 제품군에 가장 최근에 추가된 제품이다. 그림 2는 이 트랜시버 아키텍처를 나타낸 것이다. 이 트랜시버 제품은 송신과 수신 기능을 모두 지원하는 듀얼 채널 무선 기능의 모놀리식 IC로서, 직접 변환 아키텍처로 구현되었다. 이 디지털 프로세싱은 직교 위상 오류 교정, dc 오프셋, LO 누설 알고리즘을 포함함으로써, 기존에는 직접 변환 아키텍처로 달성해왔던 성능들을 구현할 수 있게 해준다. 또한 이 트랜시버는 완벽한 RF 대 디지털 기능을 제공한다. 6GHz에 이르는 RF 주파수를 지원하며, JESD204B 인터페이스는 ASIC 또는 FPGA 기반 프로세서에 대한 고속 데이터 인터페이스를 제공한다.

그림 2: ADRV9009 트랜시버의 기능 블록 다이어그램

그림 3: 직접 상향변환 블록 다이어그램과 위상 잡음 요인들

이 무선 디바이스는 레퍼런스 주파수 입력에 동기화된다. 다수의 PLL 위상을 컨버터 클럭, LO, 디지털 클럭 등의 레퍼런스에 동기화한다. 외부 LO를 사용하면 내부 LO PLL을 바이패스 할 수 있다. LO 경로 상에는 PLL 또는 외부 LO 입력과 믹서 포트 사이에 주파수 분주기가 존재한다. 이 분주기를 사용해서 직접 변환 아키텍처에 필요한 직교 위상 LO 신호를 생성한다. 컨버터 클럭과 LO가 위상 잡음에 직접적인 영향을 미치는데, 이에 대해서는 뒤에서 위상 잡음 요인에 대해서 다루면서 더 알아보기로 한다.

위상 잡음 요인

송신 출력에서 위상 잡음은 여러 요인들로 이루어진다. 그림 3은 직접 변환 파형 생성기 아키텍처의 블록 다이어그램과 주요 위상 잡음 요인들을 보여준다.

트랜시버 위상 잡음 분석에 앞서 몇 가지 기초적인 원리들을 살펴보자. 주파수 체배기나 분주기에서 위상 잡음은 20logN으로 변화한다. 여기서 N은 입력 대 출력 주파수의 비율이다. 이것은 직접 디지털 합성기(DDS)도 마찬가지다. 이 경우에는 클럭 잡음이 DDS 출력 주파수에 따라서 20logN으로 변화한다. 두 번째로 고려해야 할 것은 PLL의 위상 잡음 전달 함수이다. PLL로 주입된 레퍼런스 주파수는 (체배기와 마찬가지로) 출력으로 주파수 비의 함수로서 변화할 뿐만 아니라, 루프 대역폭(BW)과 선택한 루프 필터 타입에 따라서 저역통과 필터의 효과를 나타낸다.

이러한 점들을 감안했을 때 트랜시버로 다양한 요인들이 작용한다는 것을 알 수 있다. 트랜시버로 LO 주파수와 레퍼런스 주파수의 두 가지 주파수가 주입된다. LO 주파수는 위상 잡음 출력에 직접적으로 영향을 미치는데, 직교 위상 LO 신호를 생성하는데 사용되는 내부 주파수 분주기에서 6dB 감소한다. 레퍼런스 주파수로 인한 잡음은 다양한 요인들로 인해 결정된다. 이는 클럭 PLL에서 DAC 클럭을 생성하는 데 사용된다. 레퍼런스 주파수로 인한 클럭 출력 상의 잡음은 PLL의 잡음 전달 함수에 따라서 변화한다. 그런 다음 이 잡음은 다시 DAC 클럭 대 DAC 출력 주파수 비에 따라서 변화한다. 이 같은 효과는 PLL 대역폭에 따른 저역통과 전달 함수를 사용해서 레퍼런스 주파수에서 DAC 출력 주파수로 스케일링하는 것으로 단순화할 수 있다.

다음으로, 트랜시버 IC 위상 잡음을 살펴보자. 송신 경로 상의 모든 회로 소자들로부터 더해지는 잔류 잡음이 존재한다. IC 잡음 요인 중의 하나는 DAC 출력에서 첨가되는 잡음인데, 이것은 DAC 출력 주파수에 따라서 달라진다. 이 잡음은 다시 두 가지 잔류 위상 잡음으로 요약할 수 있다. 주파수 종속적 잡음과 주파수 독립적 잡음이 그것이다. 주파수 종속적 잡음은 DAC 출력 주파수에 따라서 20logN으로 변화한다. 주파수 독립적 잡음은 고정적이며, 트랜시버 IC의 위상 잡음 플로어를 결정한다.

그림 4: 다양한 위상 잡음 요인들을 추출하기 위해서 사용된 위상 잡음 측정

그림 5: 위상 잡음 측정에 사용된 테스트 셋업

주파수 종속적 및 주파수 독립적 잡음의 함수로서 IC 잔류 잡음을 추출하기 위해, 그림 4에서 보는 것과 같이 일련의 위상 잡음 측정을 실시했다.

그림 5는 위상 잡음 측정에 사용된 테스트 셋업을 보여준다. 트랜시버 LO 및 레퍼런스 주파수 입력으로는 각각 로데슈바르즈의 SMA100B와 100A를 사용했으며, 위상 잡음 테스트 세트로는 홀츠워스의 HA7402C를 사용했다. 절대 위상 잡음 측정을 위해서 테스트 세트에 트랜시버의 송신 출력을 주입한다. 잔류 위상 잡음 측정을 위해서는 3개의 트랜시버가 필요하다. 추가적인 트랜시버들을 테스트 세트 믹서의 LO 포트로서 사용하면 측정으로부터 레퍼런스 주파수와 LO 주파수로 인한 잡음을 제거할 수 있다.

그림 4의 측정 데이터로부터 트랜시버 IC로 인한 주파수 종속적 및 주파수 독립적 위상 잡음을 추출했다. 그림 6은 이렇게 해서 계산된 것을 보여준다. 측정 데이터로 대입하고 1MHz 이상의 오프셋 주파수로 위상 잡음 플로어에 대해서 임계 설정을 적용해서 계산을 도출했다.

그림 6: 트랜시버 잔류 위상 잡음 요인. 이들 곡선은 그림 4의 측정 데이터로부터 추출했다.

절대 위상 잡음 측정값 대 예측값

위에서 설명한 것과 같은 다양한 위상 잡음 요인들을 분석함으로써 DAC 출력 주파수와 LO 및 레퍼런스에 사용된 오실레이터에 기반해서 예측을 할 수 있다. 그림 7은 측정 결과와 예측 결과를 비교해서 보여준다.

잡음 요인들은 다음과 같이 계산했다:

▶ LO 위상 잡음: 그림 4에서 측정된 LO 위상 잡음을 사용했으며, 트랜시버 IC 내의 주파수 분주기를 반영하기 위해서 6dB 감소시켰다.

▶ 레퍼런스 위상 잡음: 그림 4에서 측정된 레퍼런스 잡음을 시작점으로 사용했다. 트랜시버의 클럭 PLL은 루프 대역폭이 수백 kHz에 이르기 때문에 레퍼런스 잡음에 대해서 비슷한 대역폭의 2차 저역통과 필터를 적용했다. 그런 다음, 잡음을 DAC 출력 주파수 대 레퍼런스 주파수 비의 20log로 변화시켰다.

▶ IC 잡음: 그림 6의 곡선들을 사용했다.

측정 결과가 예측값에 거의 가깝게 일치하며, 그래프를 통해 어떤 요인들이 다양한 오프셋 주파수들에 주로 영향을 미치는지 알 수 있다. 5kHz 이하의 오프셋 주파수에는 1차 LO가 지배적이다. 1MHz 이상의 오프셋에는 IC 잔류 잡음이 지배적이다. 10kHz ~ 500kHz 사이의 중간 오프셋 주파수에서는 DAC 출력 주파수가 중요해진다. 높은 DAC 출력 주파수에서는 IC의 주파수 종속적 잡음이 지배적이다. DAC 출력 주파수가 낮아질수록, IC 잡음이 감소하고 LO 주파수가 다시 지배적이 된다.

외부 LO 사용 시 고려 사항

외부 LO를 사용하고자 할 때 어떤 점들을 고려해야 할지 살펴보자. 특히 다음 두 가지 사항을 유의해야 한다.

▶ 내부 주파수 분주기를 사용하면 스타트업을 할 때나 외부 LO를 스위칭 할 때 위상 모호성이 있을 수 있다. RF 위상 동기 기능은 내부 LO에는 포함되는데, 외부 LO는 아직 이 기능을 지원하지 않는다.

▶ 외부 LO를 호핑 할 때 QEC 알고리즘 안정화 시간이 걸리는데, 이 시간이 주파수 변경 직후에 이미지에 영향을 미칠 수 있다.

이러한 문제들 때문에 트랜시버의 순시 대역폭 이상으로 동작 대역들 간에 동적으로 호핑 하는 다채널 시스템에 복잡성을 야기할 수 있다. 향후 출시될 트랜시버들은 이러한 한계점들을 극복하겠지만 현재로서는 ADRV9009에 외부 LO를 사용하고자 할 때 이러한 복잡성이 존재한다.

그럼에도 불구하고, 외부 LO의 향상된 위상을 활용할 수 있는 다양한 애플리케이션들이 있다. 이러한 애플리케이션으로는 동적 호핑 요구가 덜 엄격한 단일 채널 또는 채널 수가 적은 시스템이나 고정된 LO 주파수를 사용하는 다채널 시스템을 들 수 있다.

외부 LO의 위상 잡음 성능을 활용하기에 특히 적합한 애플리케이션이 상대적으로 협대역인 위상 배열 시스템이다. 이 애플리케이션에서는 범용 파형 생성기와 리시버 설계용으로 이 트랜시버를 사용해서 넓은 동작 주파수를 지원하도록 하고, 실제 동작이나 최종적인 LO 구현 단계에서 특정 대역을 선택할 수 있다.

그림 7: 외부 LO를 사용할 때의 위상 잡음 측정 결과와 예측 결과 비교. 트랜시버 중심 주파수가 2.6GHz이기 때문에 LO를 5.2GHz로 설정했다. DAC 출력 주파수는 12.5MHz에서부터 100MHz까지 다양하게 변화시켰다. 예측 결과가 측정 결과와 일치하므로, 이 분석 기법을 다른 주파수로도 확장할 수 있다는 것을 알 수 있다.

동작 대역이 트랜시버의 순시 대역폭 이내인 위상 배열 시스템은 외부 LO가 단일 주파수일 수 있으며, 이 경우에는 위상 배열로 트랜시버에 외부 LO를 사용하는 것이 실용적인 방법일 수 있다. 시스템 위상 잡음을 평가할때 레퍼런스 주파수 잡음원이 LO 잡음원보다 훨씬 낮은 영향을 갖을 경우, 레퍼런스 주파수 소스 오실레이터를 선택할 수 있다. 공통 LO를 배열된 트랜시버들로 분배할 때는, 시스템에 코히어런트 하게 결합되는 트랜시버 수가 많아질수록 IC로 인한 잡음이 감소하고 외부 LO가 지배적이게 된다. 그러면 시스템 엔지니어링 잡음 분석을 간소화할 수 있다. 공통 LO가 대부분을 차지하는 잡음의 경우, 엔지니어링 시에 LO 설계의 가격대 성능비를 최적화하는 것에 초점을 맞출 수 있다.

맺음말

이 글에서는 외부 LO를 사용하고자 할 때 ADRV9009 트랜시버의 위상 잡음을 예측하기 위한 기법을 설명했다. 이 기법을 사용해서 DAC 출력 주파수에 따라 레퍼런스 오실레이터, LO 소스, 트랜시버로 인한 잡음을 추적할 수 있다. 측정 결과와 예측 결과가 거의 일치하므로, 다른 주파수 소스에 대해서도 이 기법을 적용하여 트랜시버의 성능을 예분석할 수 있다는 것을 알 수 있다. 또한 이 기법은 상당히 일반적으로 어느 파형 생성기 설계에도 똑같이 적용할 수 있다.

외부 LO 사용 시 측정한 위상 잡음 성능을 보면, 위상 잡음이 낮은 LO 소스를 사용해서 상당한 성능 향상을 거둘 수 있다는 것을 알 수 있다. 이 글의 목적은 시스템 설계 엔지니어들이 아키텍처를 검토하는 단계에서 다양한 선택을 할 수 있도록 돕기 위한 것이다. 낮은 위상 잡음을 요구하는 애플리케이션에서 이 트랜시버를 외부 LO 입력과 함께 사용하고자 하는 경우, 이 글에서 설명한 기법을 사용해서 다양한 조건으로 시스템 차원의 위상 잡음을 평가할 수 있다.

시스템 위상 잡음을 평가하기 위해서, 레퍼런스 주파수 잡음원이 LO 잡음원보다 훨씬 낮을 경우 레퍼런스 주파수 소스 오실레이터를 선택할 수 있다. 공통 LO를 일련의 트랜시버들로 분배할 때는, 시스템에 코히어런트 하게 결합되는 트랜시버 수가 많아질수록 IC로 인한 잡음이 감소하고 외부 LO가 지배적이게 된다. 그러면 시스템 엔지니어링 잡음 분석을 간소화할 수 있다. 공통 LO가 대부분을 차지하는 잡음의 경우, 엔지니어링 시에 LO 설계의 가격대 성능비를 최적화하는 것에 초점을 맞출 수 있다.

저자 소개

피터 딜로스(Peter Delos)는 미국 노스캐롤라이나주 그린즈버로에 위치한 아나로그디바이스(Analog Devices)의 항공 방위 그룹 테크니컬 디렉터이다. 1990년에 버지니아공대에서 BSEE를, 2004년에 NJIT에서 MSEE를 취득했으며, 25년 넘게 이 업계에 종사하고 있다. 아키텍처 레벨, PWB 레벨, IC 레벨의 첨단 RF/아날로그 시스템 설계를 주로 했다. 현재는 위상 배열 애플리케이션을 위한 고성능 리시버, 파형 생성기, 합성기 설계를 소형화하는 업무에 매진하고 있다. 문의: peter.delos@analog.com

제품스펙