기술기고문

PSMR과 PSRR 비교: 전원장치가 RF 성능에 미치는 영향 계산법

PSMR과 PSRR 비교: 전원장치가 RF 성능에 미치는 영향 계산법

많은 레이더 시스템이 클러터 제거를 극대화하기 위해서 낮은 위상 잡음을 요구한다. 고성능 레이더일수록 위상 잡음을 더욱 까다롭게 다루기 때문에 합성기 위상 잡음을 낮추고, 합성기 부품의 특성을 분석하는 데 엄청난 시간과 비용을 투입하게 된다.

위상 잡음을 최대한 낮추기 위해서는 잡음이 낮은 전원장치를 사용해야 한다. 하지만 전원장치 잡음 전압이 위상 잡음에 얼마나 영향을 미치는지를 수치적으로 파악할 수 있는 체계적인 접근법은 나와 있지 않다. 이 글에서는 바로 이에 대해서 설명한다.

PSMR(power supply modulation ratio, 전원공급장치 변조 비율)은 전원장치 불완전성이 어떻게 RF 반송파로 변조되는지를 나타내는 기법이다. 이를 통해 RF 증폭기를 특성화 할 수 있으며, 그렇게 측정한 결과는 전원장치 잡음이 위상 잡음에 얼마나 영향을 미치는지를 대한 수치적으로 계산할 수 있으며, 꽤 정확하게 예측이 가능하다는 것을 보여준다. 또한 이러한 계산을 바탕으로, 전원장치 사양에 대한 시스템적인 접근도 가능하다.

아래 ‘이론’ 부분에서는 전원장치 불완전성이 얼마나 반송파로 변조되는지를 수치적으로 나타내는 PSMR과 관련한 전달 함수인 H(s)에 대해서 소개한다. H(s)는 진폭 성분과 위상 성분으로 이루어지며, 주파수와 동작 조건에 따라서 달라진다. 수 많은 변수들이 있지만 일단 특성화 작업을 마치면, PSMR을 활용하여 전원장치로 인해 발생하는 위상 잡음과 스퓨리어스를 데이터 시트의 리플 및 잡음 사양을 토대로 정확하게 예측할 수 있다.

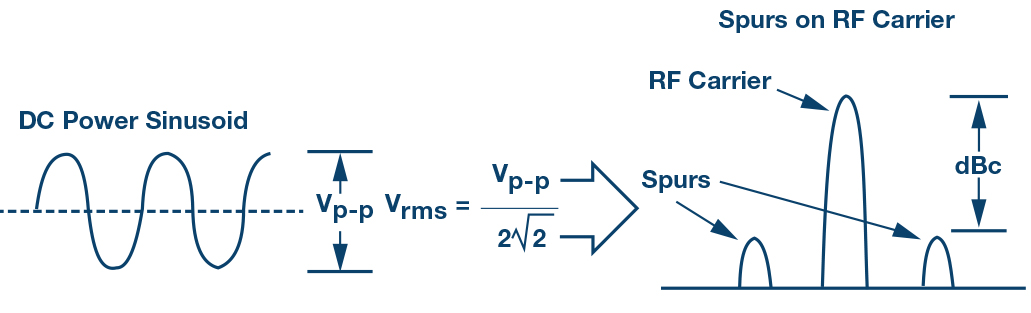

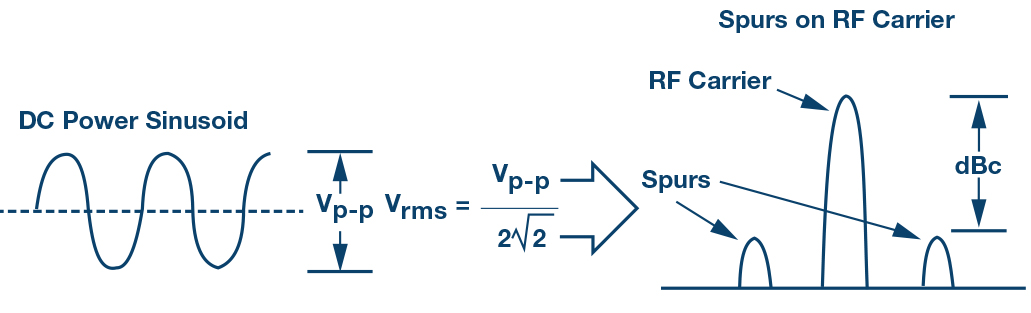

그림 1: 전원장치의 사인파 리플이 RF 반송파로 변조됨으로써 스퓨리어스 신호를 발생시킨다.

스퓨리어스의 크기는 사인파 진폭과 RF 회로 감도에 따른 함수이다. 스퓨리어스 신호는 다시 진폭 변조(AM) 성분과 위상 변조(PM) 성분으로 나눌 수 있다. 총 스퓨리어스 전력 레벨은 진폭 변조 성분으로 인한 스퓨리어스 전력과 위상 변조 성분으로 인한 스퓨리어스 전력을 합친 것이다.

아래에서 H(s)는 전원장치 불완전성이 RF 반송파로 원치 않게 변조되는 것을 나타내는 전달 함수이다. H(s)는 AM 성분과 PM 성분으로 나뉜다. H(s)의 AM 성분은 Hm(s)이고, H(s)의 PM 성분은 H∅(s)이다. 아래의 공식들은 H(s)를 RF 측정에 사용한 것으로, RF 반송파에 대한 전원장치의 영향으로 인해 발생하는 약간의 변조는 허용 가능한 것으로 간주한다.

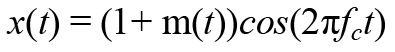

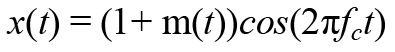

신호의 진폭 변조는 다음과 같이 표현할 수 있다:

(1)

(1)

진폭 변조 성분 m(t)는 다음과 같이 나타낼 수 있다:

(2)

(2)

여기서 fm은 변조 주파수이다.

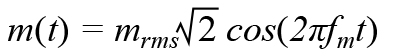

RF 반송파의 AM 변조 레벨은 다음과 같이 전원장치 리플과 직접적인 상관성을 갖는다:

(3)

(3)

vrms는 공급 전압의 AC 성분의 rms 값이다. 공식 3은 전원장치 리플로 인한 RF 반송파의 AM 변조를 계산할 수 있는 중요한 공식이다.

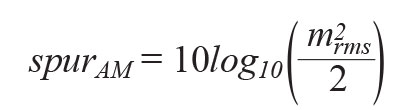

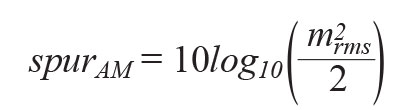

진폭 변조로부터 다음과 같이 스퓨리어스 레벨을 계산할 수 있다:

(4)

(4)

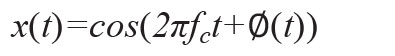

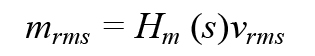

위상 변조에 대한 전원장치의 영향 역시 마찬가지이다. 위상 변조 신호는 다음과 같이 표현할 수 있다:

(5)

(5)

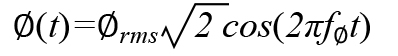

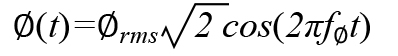

그러면 위상 변조 항은 다음과 같이 나타낼 수 있다:

(6)

(6)

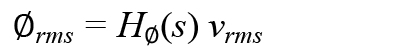

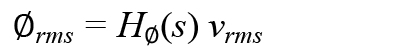

위상 변조 역시 전원장치와 직접적인 상관성을 갖는다는 것을 알 수 있다:

(7)

(7)

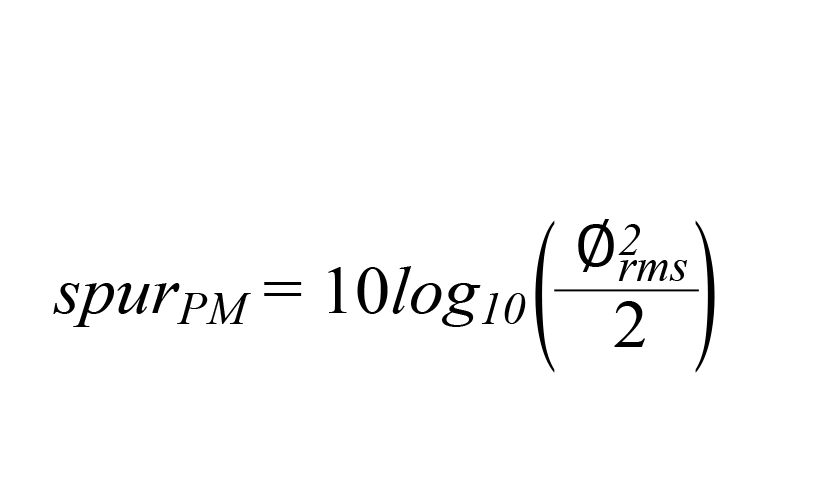

공식 7을 활용하면 전원장치 리플로 인한 RF 반송파의 PM 변조를 계산할 수 있다. 위상 변조로 인한 스퓨리어스 레벨은 다음과 같이 계산할 수 있다:

(8)

(8)

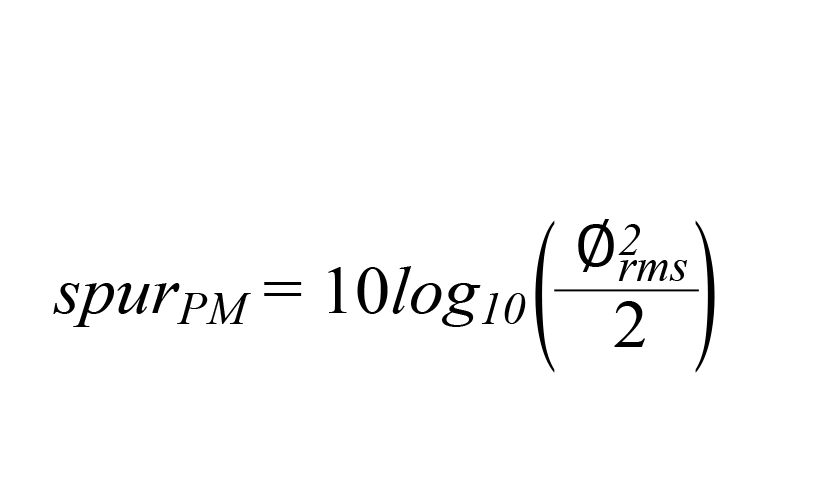

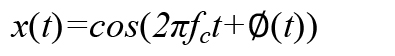

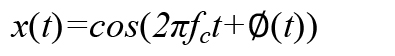

그림 2는 mrms와 ∅rms가 스퓨리어스에 어떻게 영향을 미치는지 알 수 있도록, 스퓨리어스 레벨 대 mrms와 ∅rms의 관계를 보여준다.

그림 2: 스퓨리어스 대 mrms와 ∅rms

정리하면, 전원장치 리플은 전원장치 사인파 rms 전압인 vrms로부터 변조 항인 mrms와 ∅rms로 해석된다. Hm(s)와 H∅(s)는 vrms에서 각각 mrms 및 ∅rms로의 전달 함수이다.

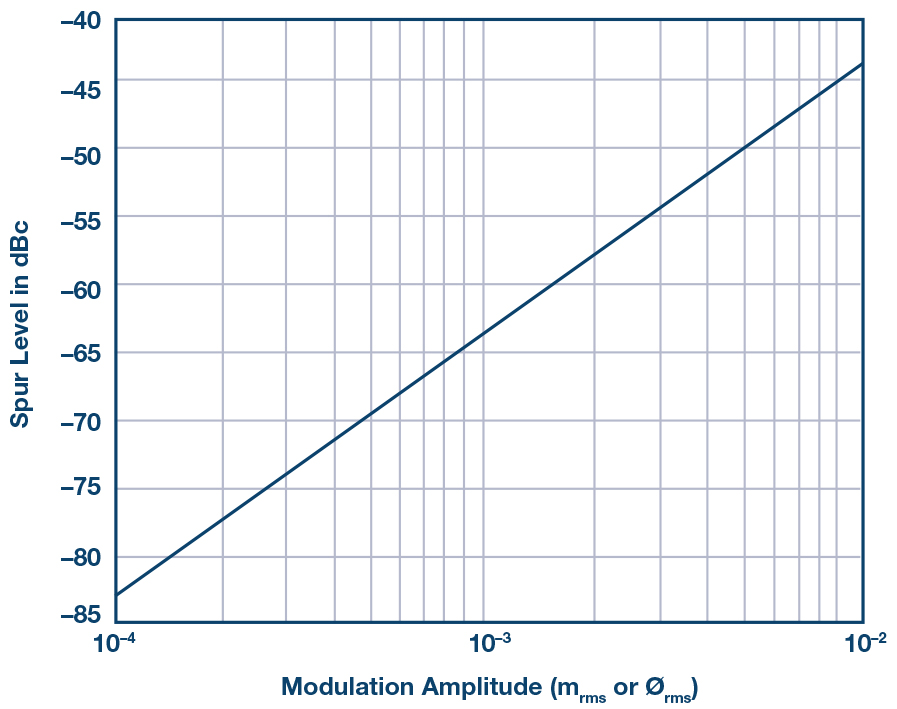

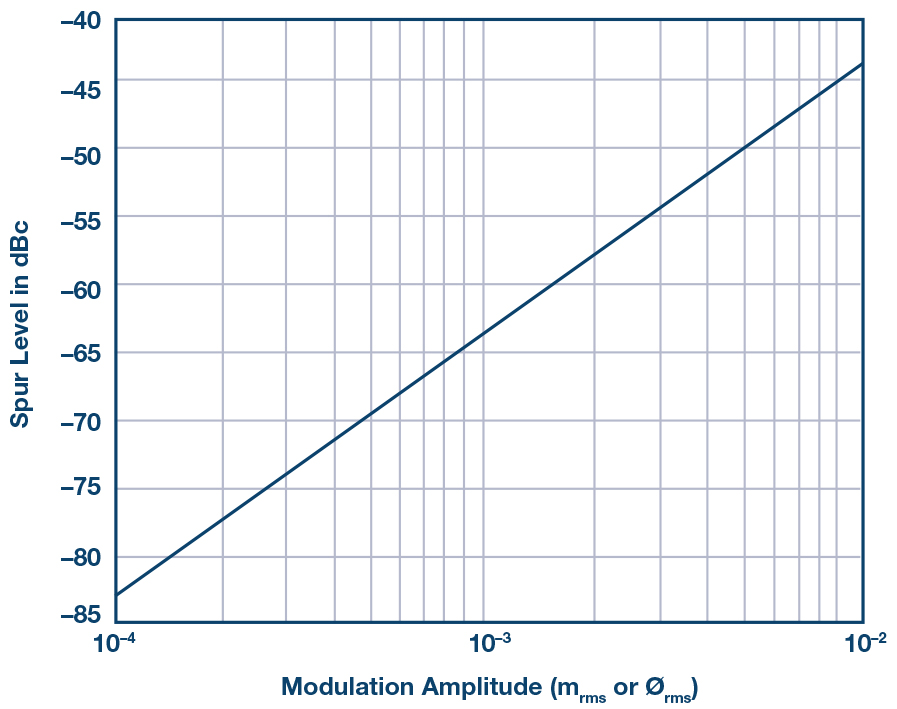

이제, 위상 잡음을 살펴보자. 사인파가 반송파로 변조되어서 스퓨리어스 신호를 발생시키듯이, 1/f 전압 잡음 밀도가 반송파로 변조되어서 위상 잡음을 일으킨다.

그림 3: 전원장치의 1/f 잡음이 RF 반송파로 변조되어서 위상 잡음을 일으킨다.

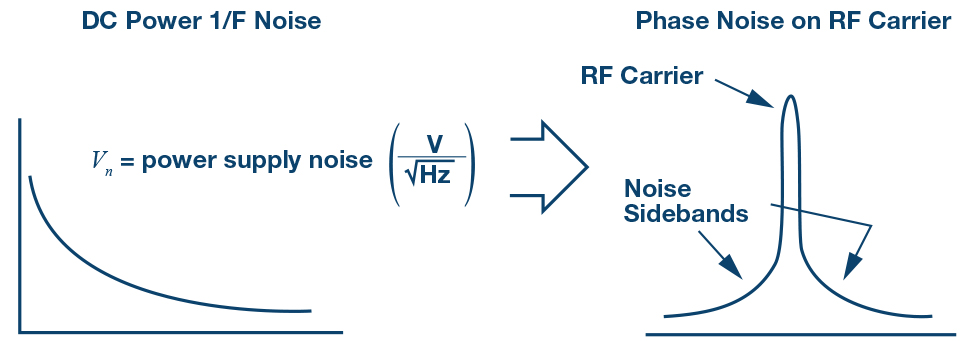

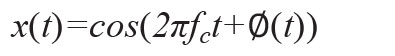

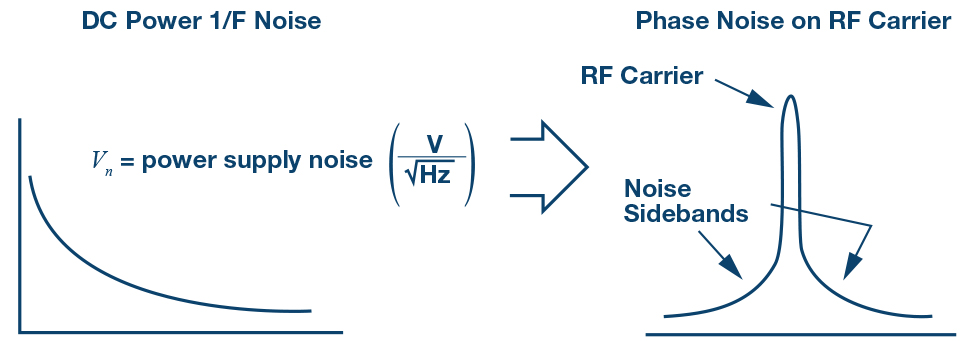

신호 x(t)의 위상 변조는 다음과 같이 나타낼 수 있다:

(9)

(9)

여기서 ∅(t)는 잡음 항이다.

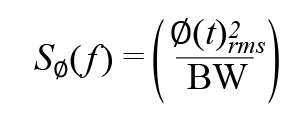

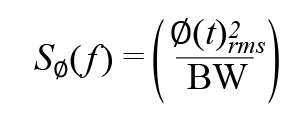

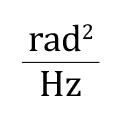

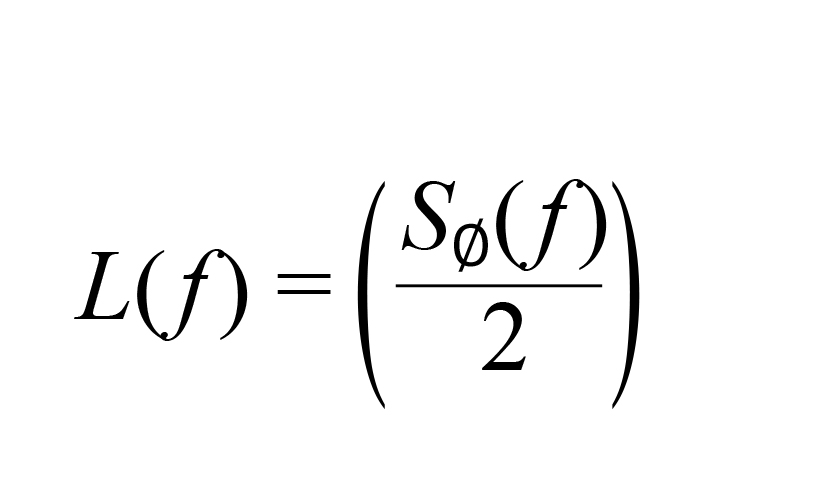

전력 스펙트럼 밀도는 다음과 같이 정의된다:

, 단위는

, 단위는  (10)

(10)

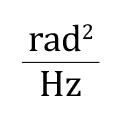

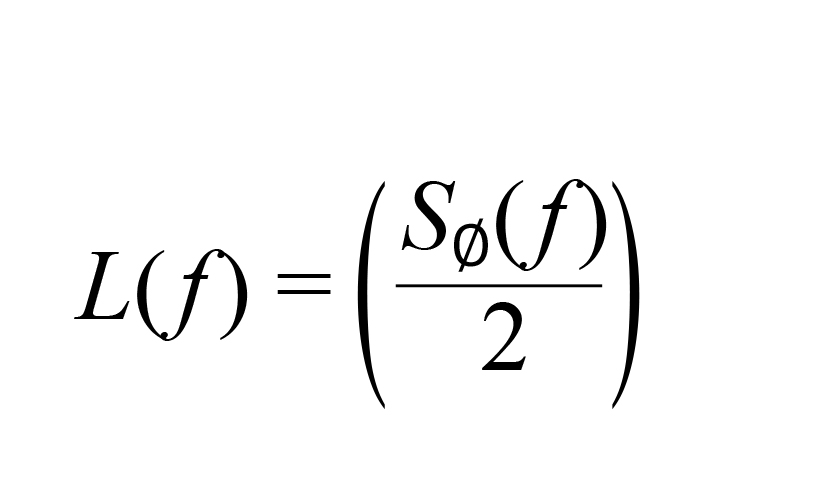

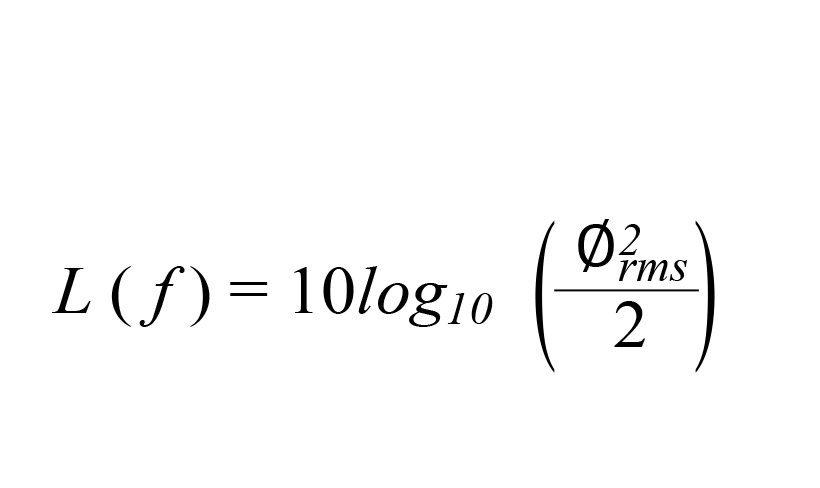

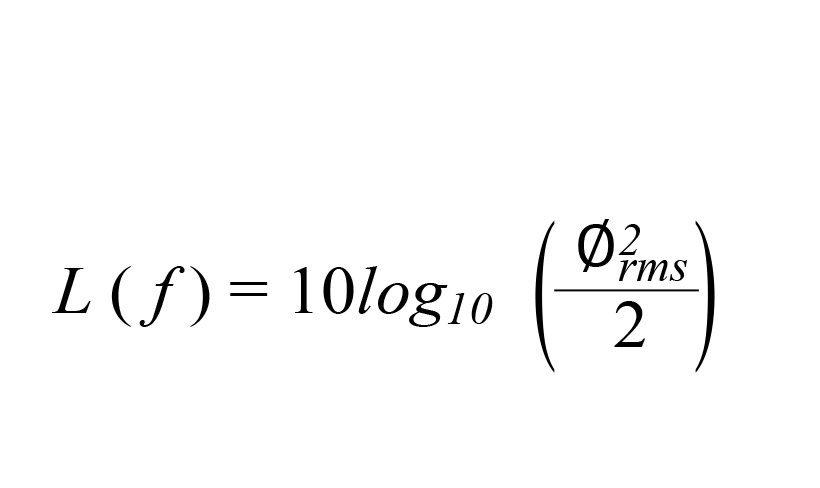

전력 스펙트럼 밀도로 인한 위상 잡음은 다음과 같다:

(11)

(11)

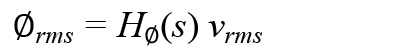

다음으로, 전원장치 리플로 인한 위상 변조로부터 발생한 스퓨리어스 계산에 사용한 H∅(s)를 위상 잡음에도 똑같이 적용할 수 있다. 이 경우에는 H∅(s)를 사용해서 전원장치의 1/f 잡음으로 인한 위상 잡음을 계산한다.

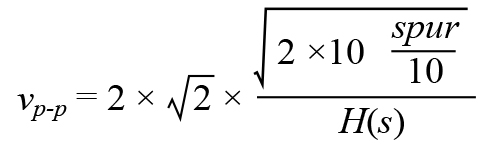

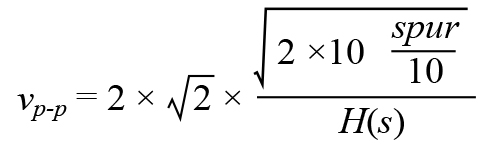

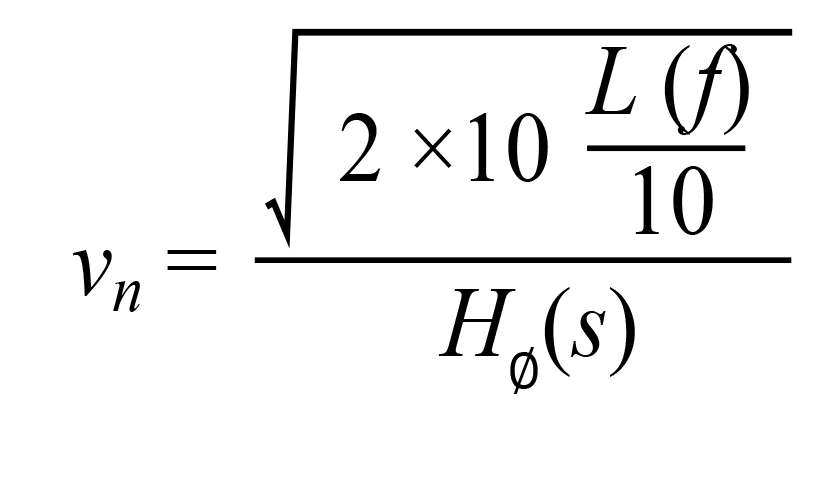

(12)

(12)

(13)

(13)

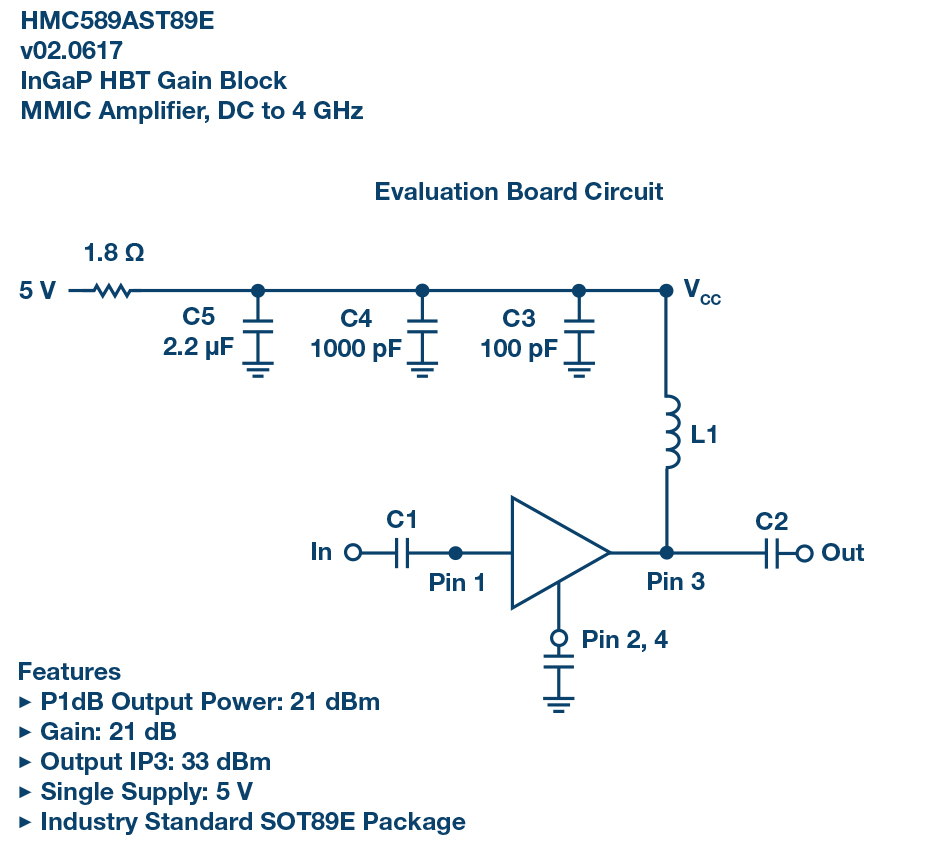

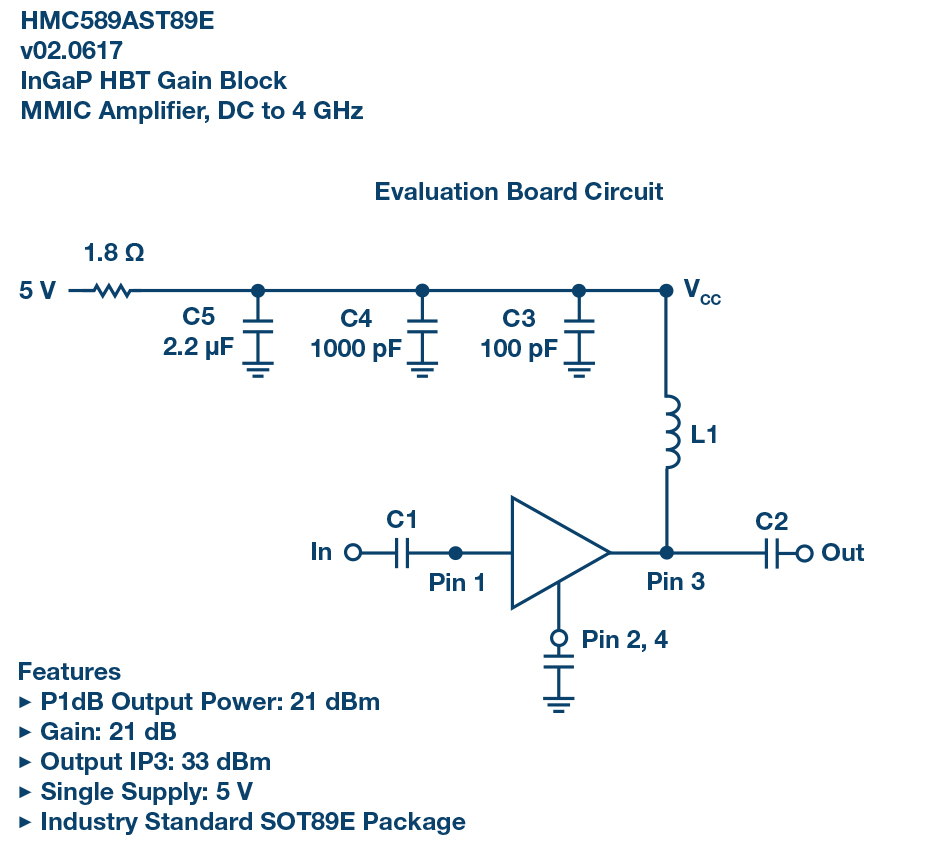

그림 4: PSMR 원리를 증명하기 위해 HMC589A 증폭기를 사용했다.

먼저 전원장치 감도를 측정하기 위해, 5V 전원에 사인파를 인가했다. 이 사인파가 RF와 스퓨리어스 신호에 발생시킨 스퓨리어스를 dBc 단위로 측정했다. 스퓨리어스 성분을 다시 AM 성분과 PM 성분으로 나누었다. 계측장비로는 로데 슈바르츠(Rohde & Schwarz)의 FSWP26 위상 잡음 분석기와 스펙트럼 분석기를 사용했다. AM 및 PM 스퓨리어스 레벨은 각각 스퓨리어스 측정이 가능한 AM 및 PM 잡음 측정을 통해 측정했다. 표 1은 3.2GHz에 0dBm RF 입력을 사용한 테스트 결과를 나타낸 것이다.

이 테스트 데이터를 보면, 사인파 변조를 통해서 RF 증폭기 전원장치 감도를 경험적으로 측정할 수 있으며, 이 테스트 결과를 토대로 전원장치 잡음이 위상 잡음에 어떻게 기여할지 예측할 수 있다는 것을 알 수 있다. 여기서는 RF 증폭기를 가지고 살펴보고 있지만, 어떤 RF 부품이든 이런 식으로 계산하고 예측할 수 있다.

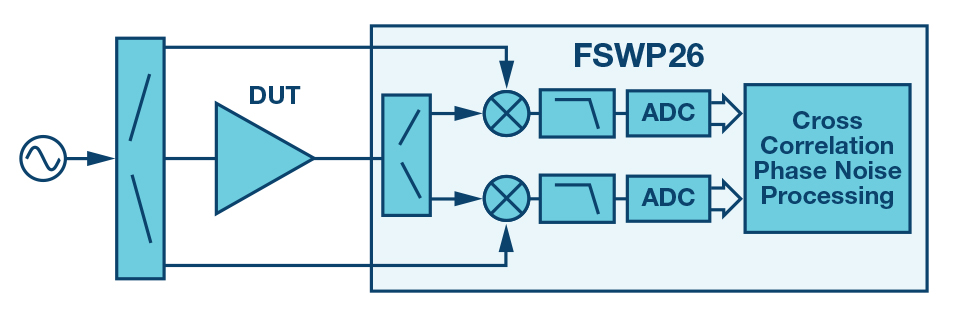

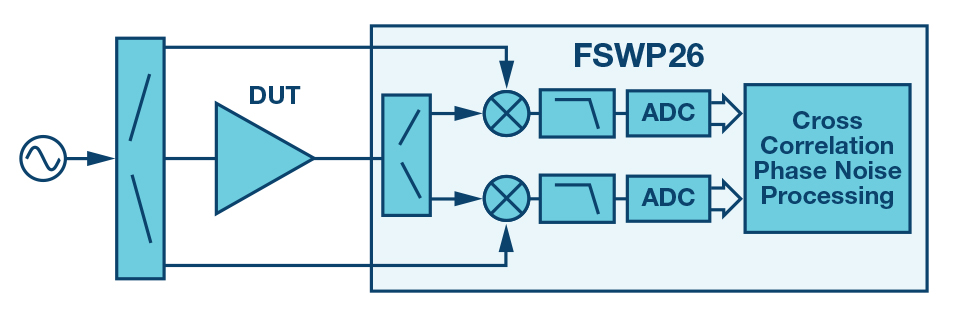

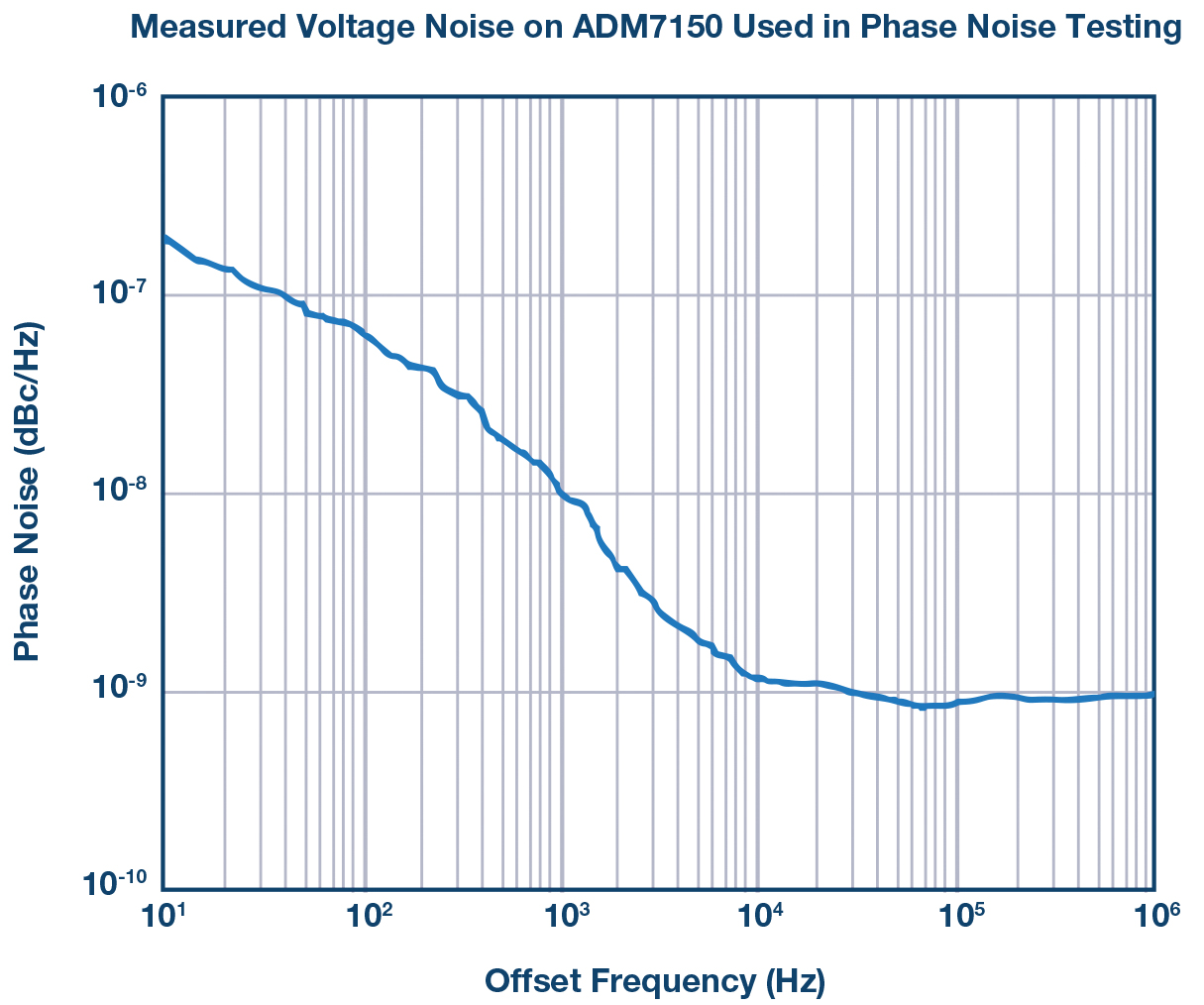

먼저, 비교적 잡음이 심한 전원장치부터 측정에 사용했다. 잡음 밀도를 측정했다. 전원장치가 위상 잡음에 미치는 영향을 H∅(s)를 바탕으로 계산하고, 이것을 실제 위상 잡음 측정과 비교했다. 측정을 위해서 로데 슈바르츠의 FSWP26 테스트 장비를 사용했다. 잡음 전압은 베이스밴드 잡음 측정을 이용해 측정했다. 증폭기 잔류 위상 잡음은 테스트 장비 내부의 오실레이터를 사용한 추가적인 위상 잡음 측정을 통해서 측정했다. 그림 5는 테스트 설정을 보여준다. 믹서에서 오실레이터 잡음을 제거하고, 교차 상관화 알고리즘을 사용해서 공통적이지 않은 잡음을 제거한다. 이렇게 함으로써 극히 낮은 수준의 잔류 잡음까지 측정할 수 있다.

그림 5: 교차 상관화 기법을 사용한 증폭기 잔류 위상 잡음 테스트 설정

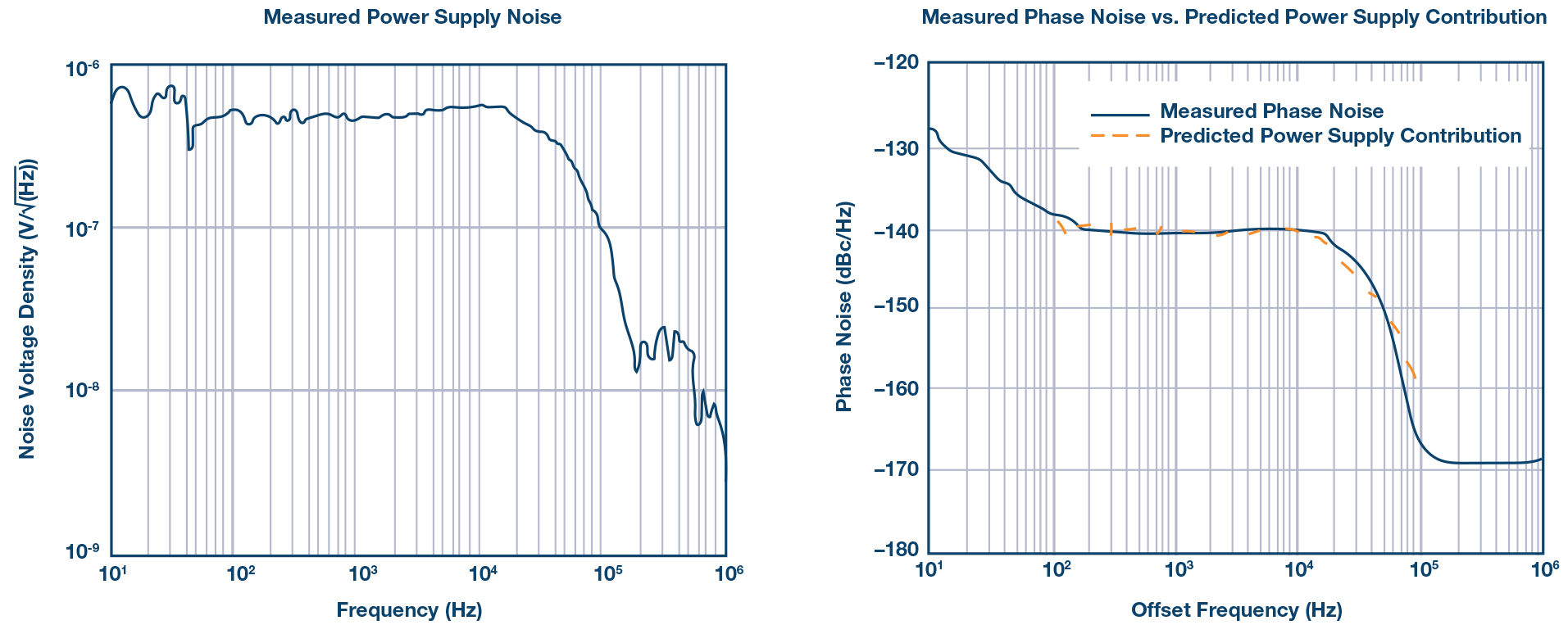

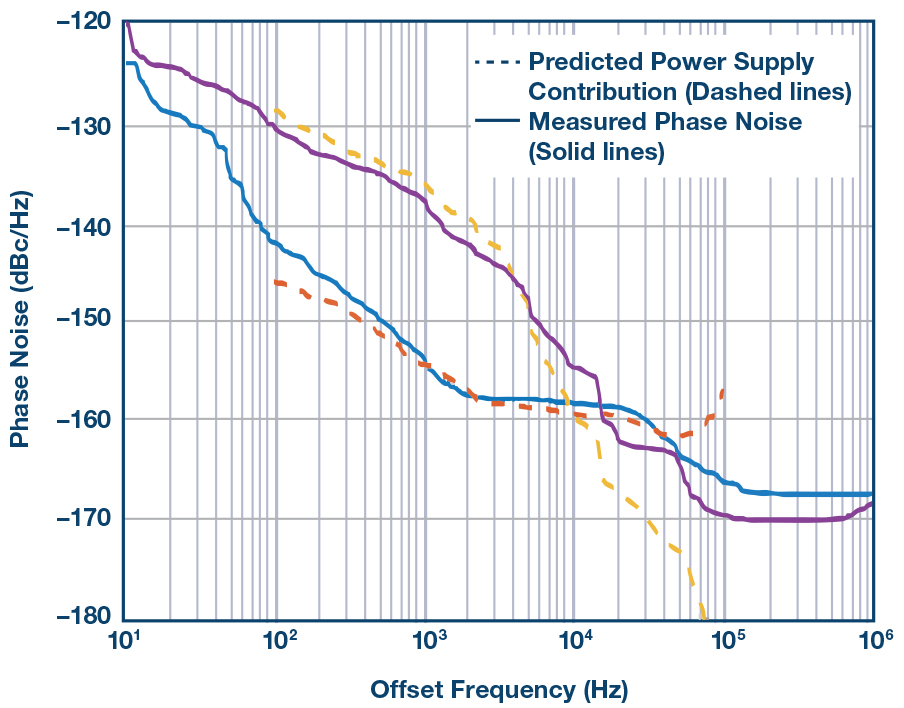

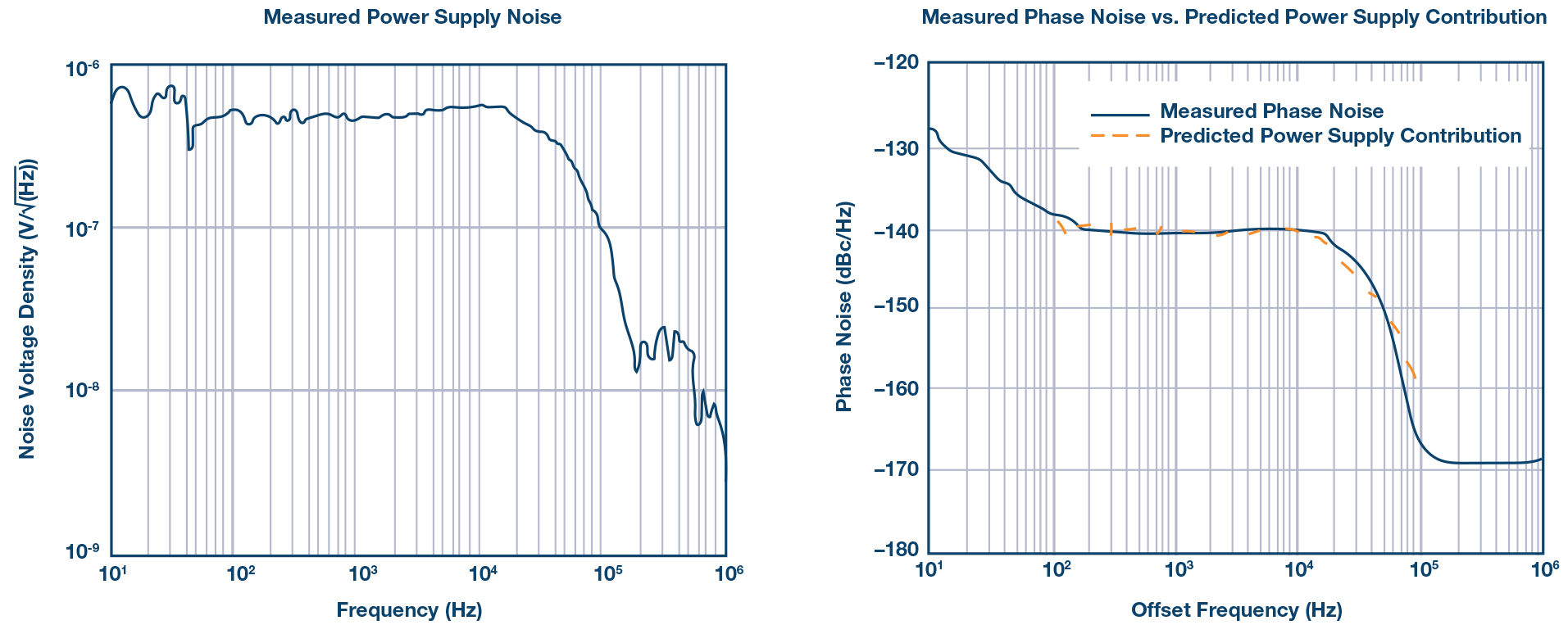

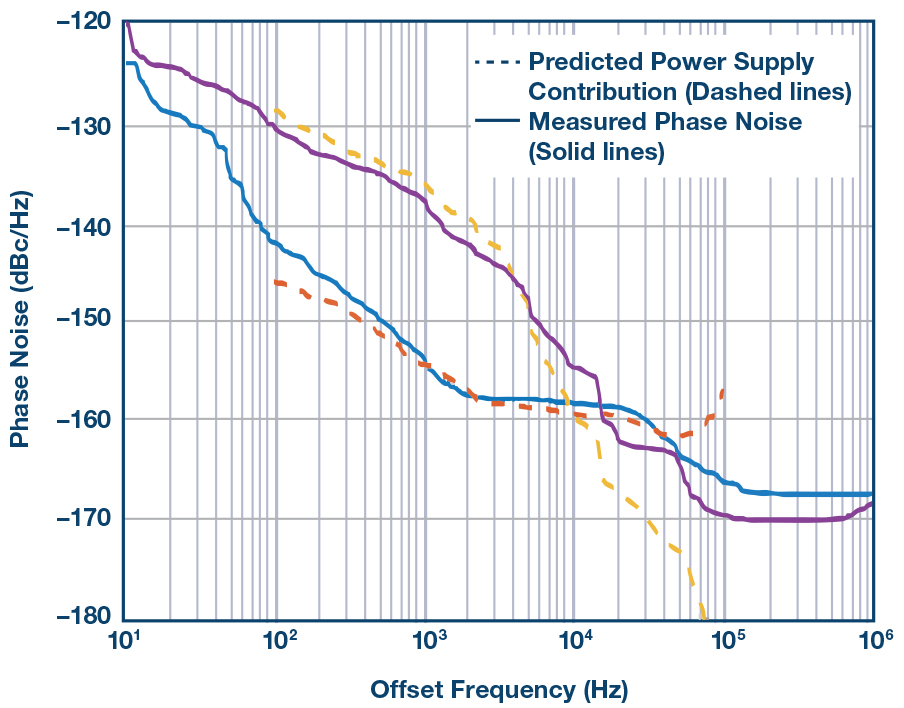

그림 6은 전원장치 잡음, 실제로 측정된 위상 잡음, 전원장치로 인한 위상 잡음 기여분 예측을 보여준다. 그림을 보면 100Hz ~ 100kHz 오프셋 지점까지의 위상 잡음에 있어서 전원장치에 의한 것이 지배적임을 알 수 있다. 따라서 전원장치로 인해 발생한 위상 잡음 기여분 예측이 정확하게 이루어졌다는 것을 확인할 수 있다.

그림 6: 잡음이 심한 전원장치를 사용한 측정

추가적으로 두 개의 전원장치에 대해서도 동일한 방식으로 측정했다. 그림 7은 테스트 결과를 나타낸다. 여기서도 역시 전원장치로 인한 위상 잡음 기여분 예측이 거의 정확하게 이루어졌다는 것을 알 수 있다.

그림 7: 추가로 두 개의 전원장치를 사용한 측정 결과

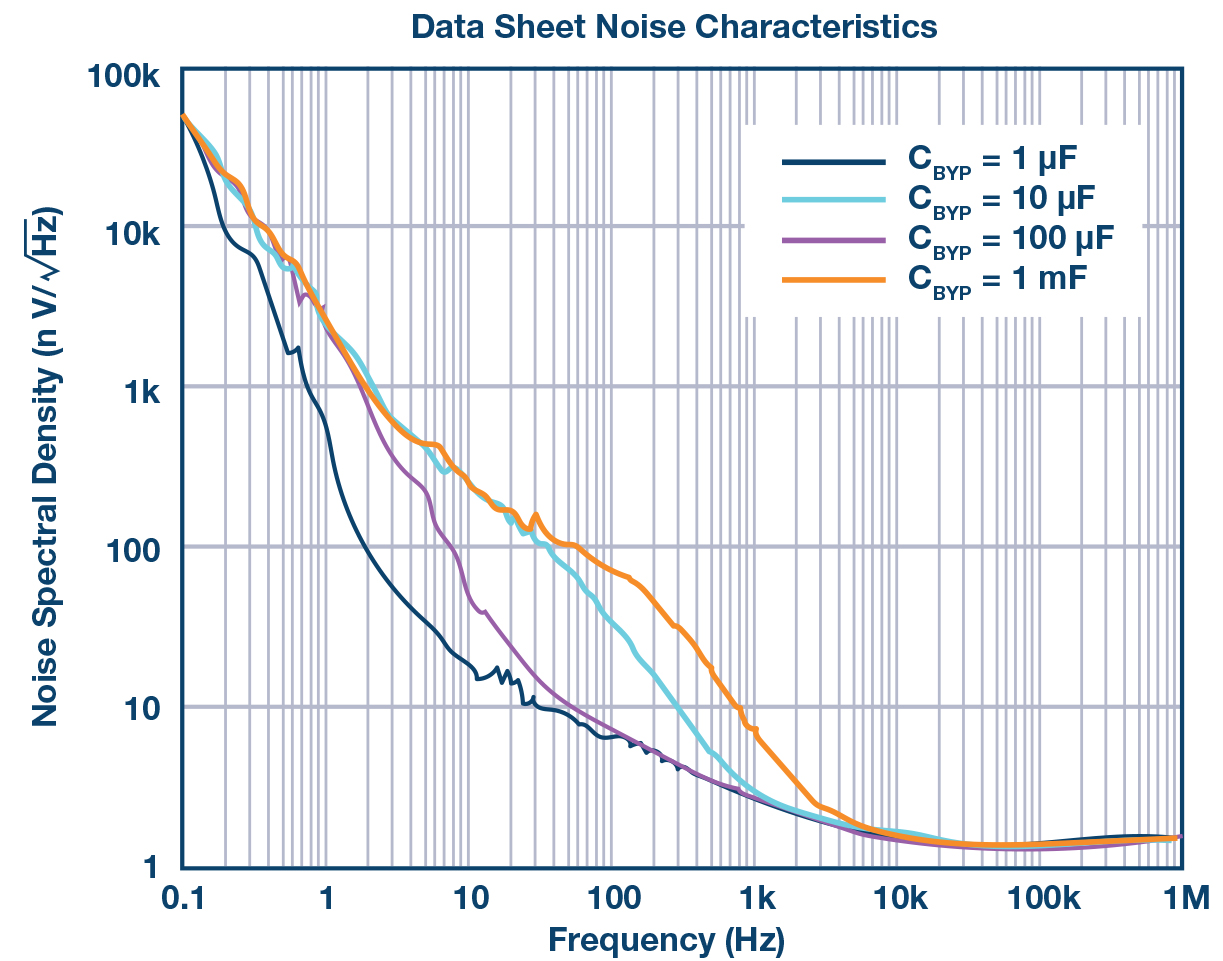

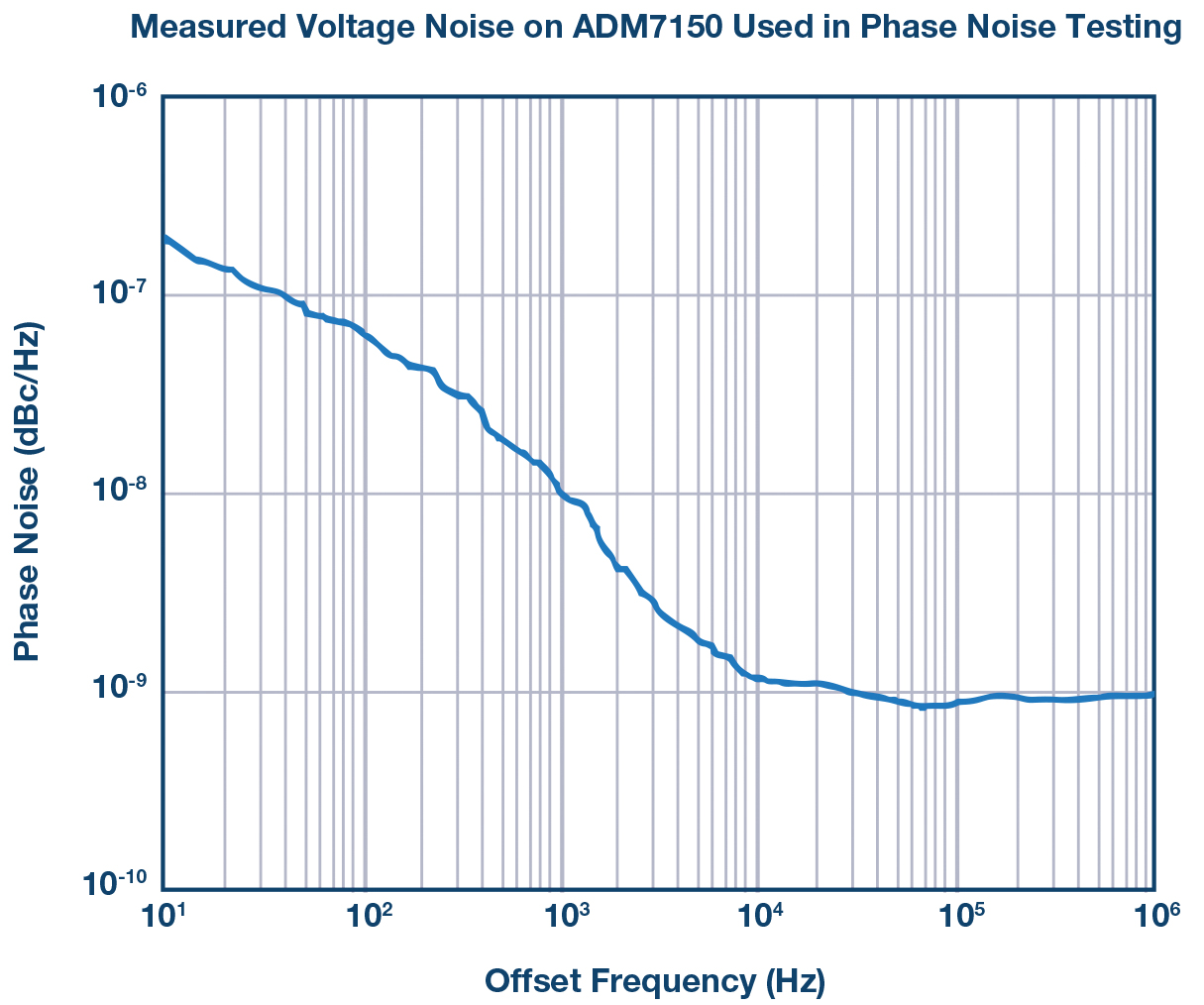

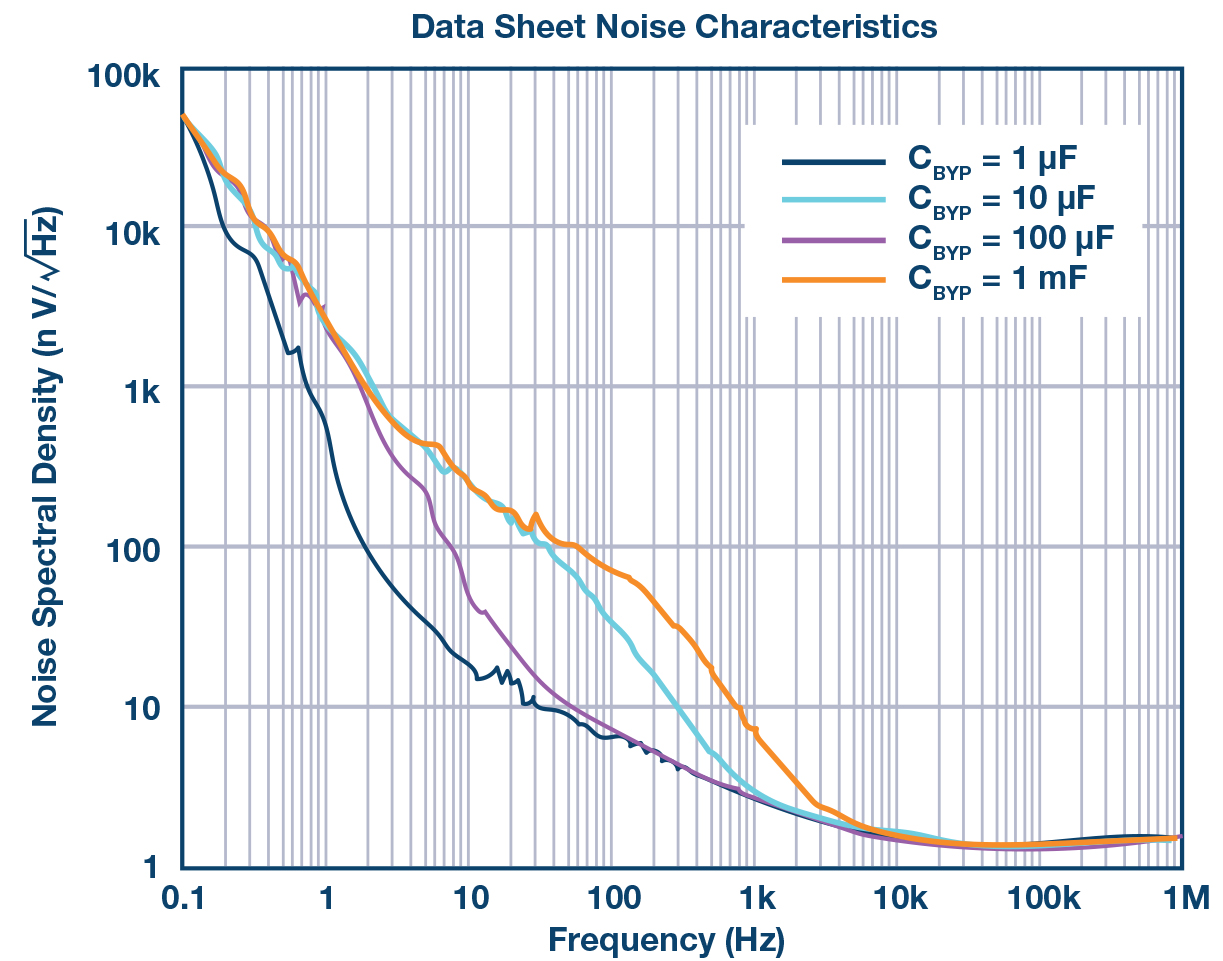

위상 잡음이 낮은 부품에 대해서 측정할 때 중요한 것은, 측정이 주변 환경이 아니라 대상 디바이스에 대해서 이루어지도록 하는 것이다. 이 측정 실험에서 전원장치 기여분을 제거하기 위해서 ADM7150 저잡음 레귤레이터를 사용했다. 그림 8은 위상 잡음 테스트에 사용된 이 디바이스의 실제 잡음 전압 측정 결과와 데이트 시트에 표기된 잡음 밀도를 나타낸다.

그림 8: 저잡음 레귤레이터 ADM7150의 잡음 전압 밀도

표 2는 주요 저잡음 레귤레이터 제품들과 각각의 주요 파라미터를 정리한 것이다. 이들 제품은 모두 낮은 위상 잡음을 요구하는 RF 설계용으로 적합하다(구체적인 테스트 조건과 특성분석 곡선은 데이터시트 참조). 데이터 시트는 다양한 오프셋 주파수에 대한 잡음 밀도와 PSRR 곡선을 포함하고 있다. 이 표에서 잡음 밀도는 10kHz 오프셋에 대한 것이다. 많은 레귤레이터 제품이 이 구간이 한계이기 때문이다. PSRR은 1MHz 오프셋에 대한 것이다. 많은 선형 레귤레이터가 이 오프셋 지점에서 제거 능력을 상실하고 추가적인 필터링을 필요로 하기 때문이다.

표 2: 낮은 위상 잡음을 요구하는 RF 설계용으로 적합한 저잡음 레귤레이터 제품

표 2: 낮은 위상 잡음을 요구하는 RF 설계용으로 적합한 저잡음 레귤레이터 제품

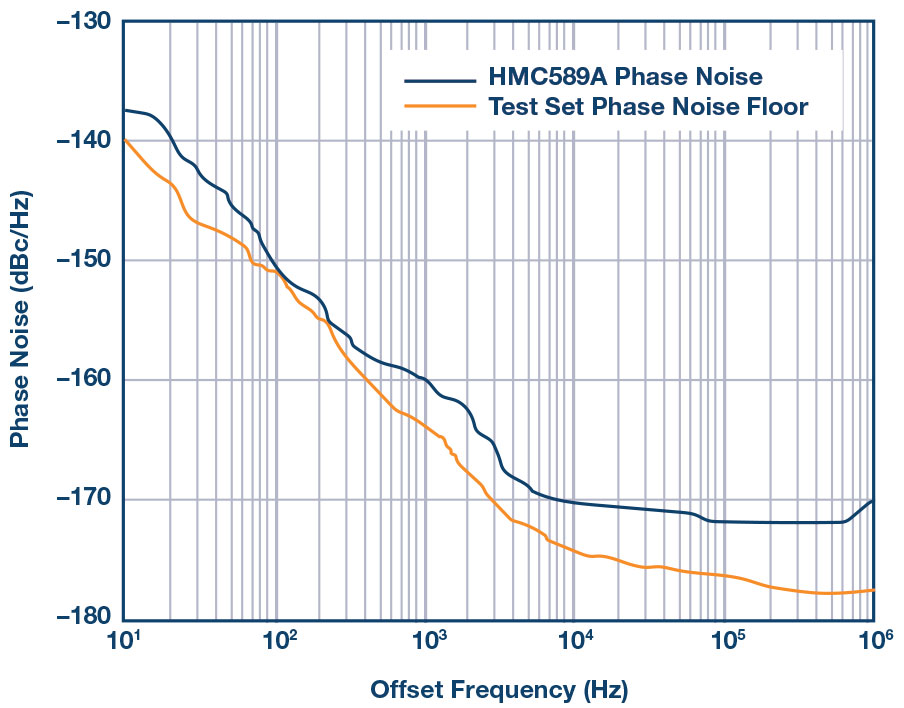

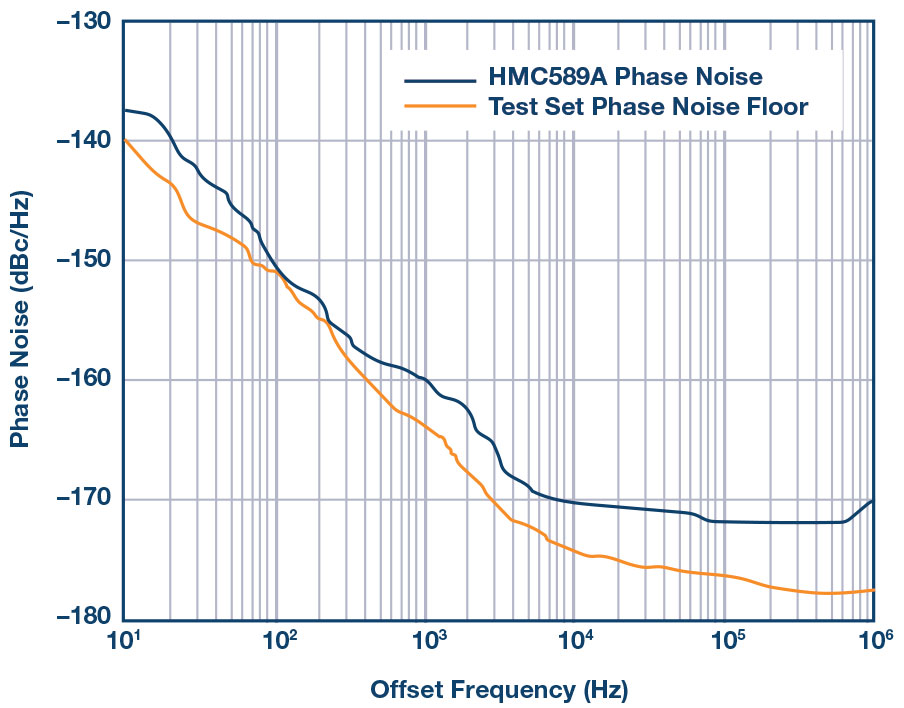

그림 9는 ADM7150을 사용했을 때 HMC589A의 잔류 위상 잡음 테스트 결과를 보여준다. 이것은 순수한 증폭기 성능을 보여주는 것으로서, 10kHz 오프셋에 이르기까지 잡음 플로어가 -170dBc/Hz 이하를 유지한다는 것을 알 수 있다.

그림 9: ADM7150 레귤레이터의 DC 전력을 사용했을 때 HMC589A의 잔류 위상 잡음 (3.2GHz 및 0dBm 입력 RF 전력 사용)

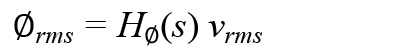

이를 방지하기 위해서는 다음과 같이 체계적이면서 수치적인 접근법으로 전원장치 사양을 도출해야 한다:

(14)

(14)

(15)

(15)

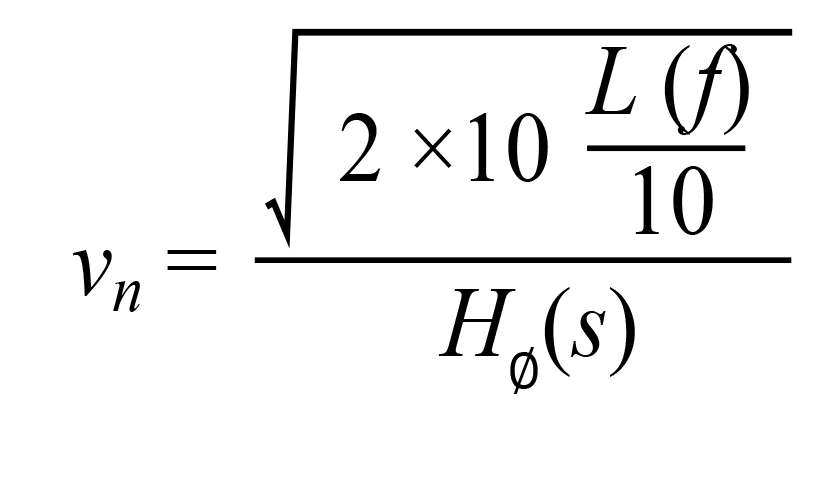

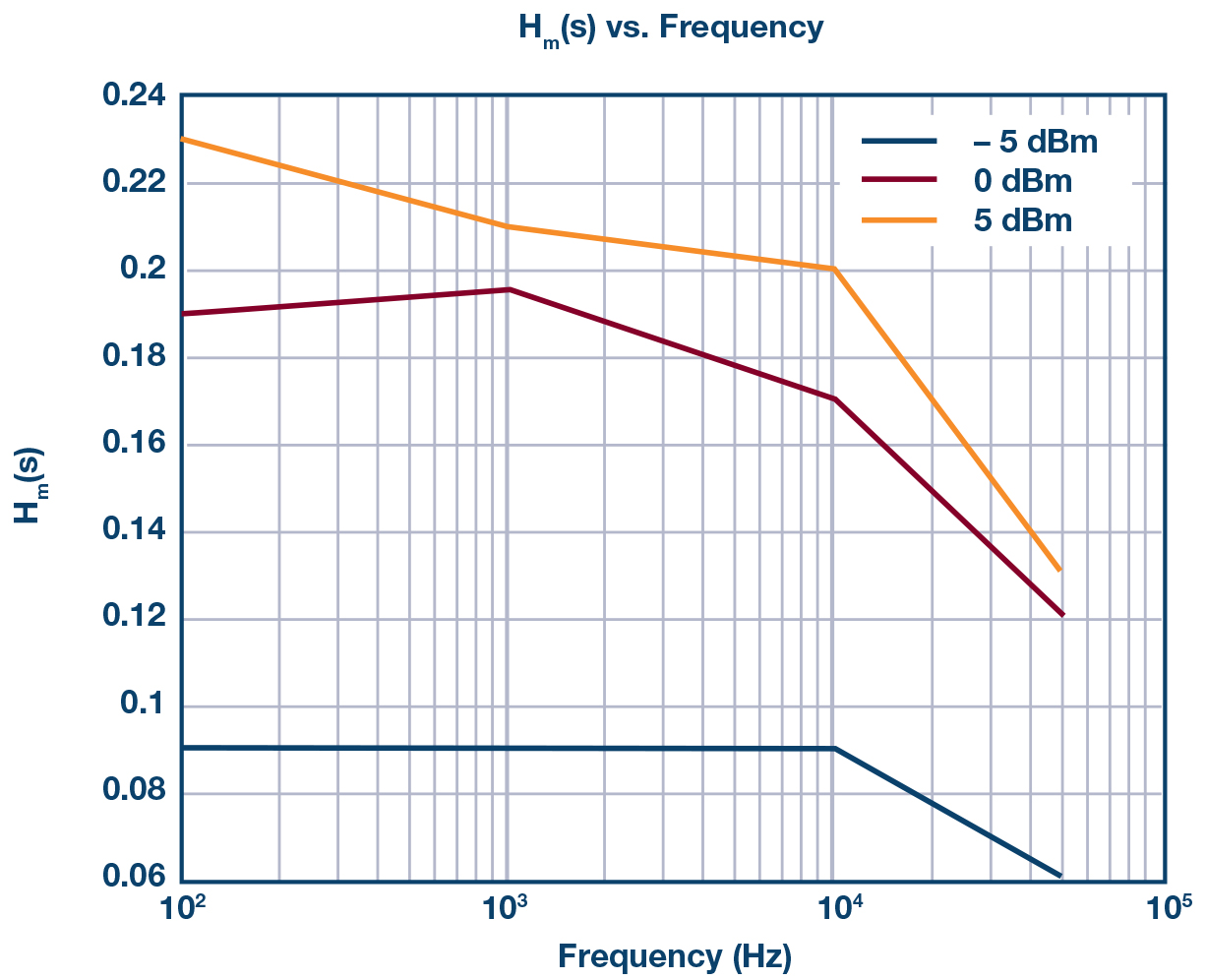

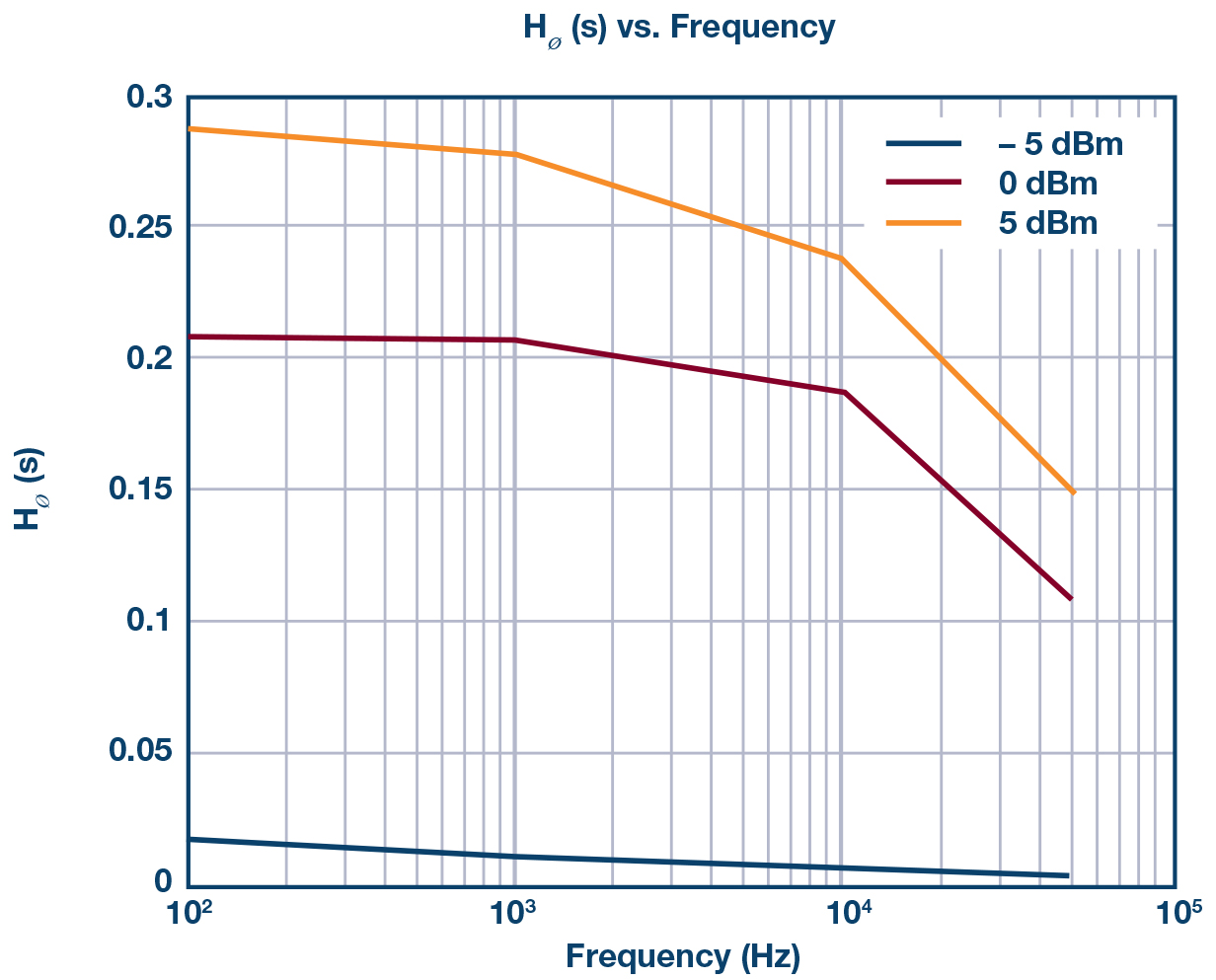

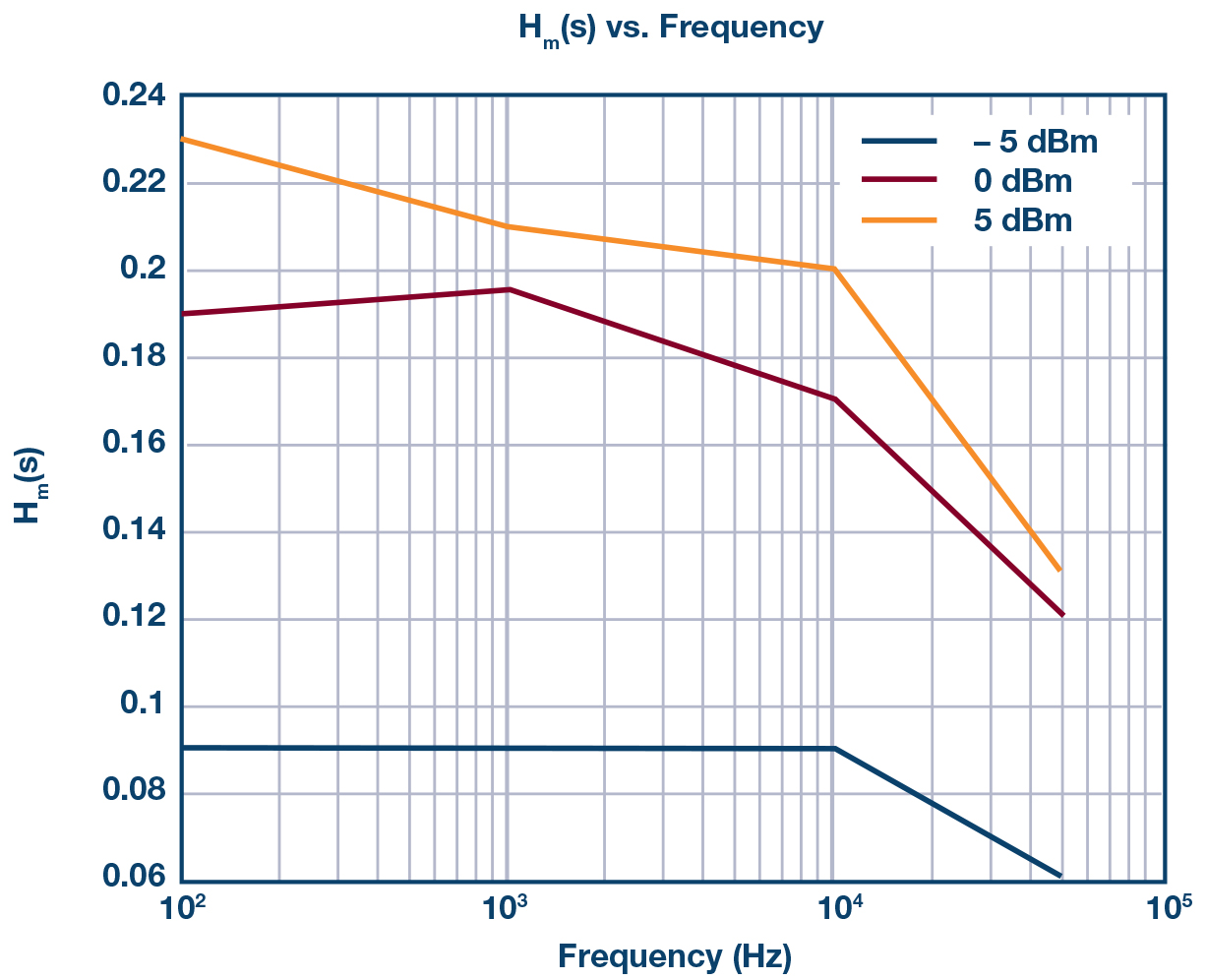

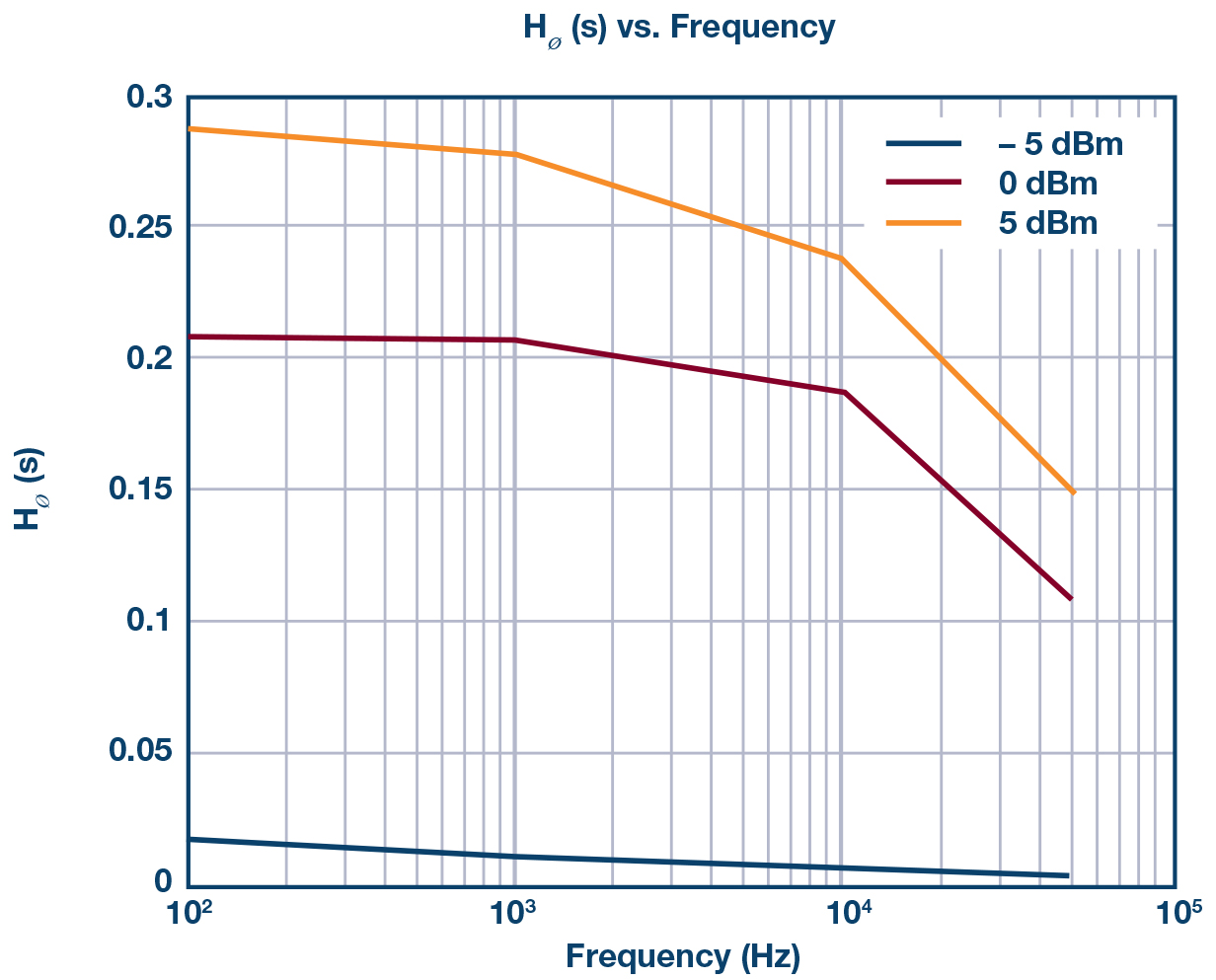

위의 1단계에서는 해당 설계에 예상되는 동작 조건으로 Hm(s)와 H∅(s)가 어떻게 변화할지 이해해야 한다. 그림 10은 다양한 전력 레벨에 따른 HMC589A에 대한 측정 결과를 보여준다.

그림 10: 3.2GHz에서 HMC589A 평가 회로를 활용한 Hm(s) 및 H∅(s)대 오프셋 주파수 및 전력 레벨 측정

글: 피터 델로스(Peter Delos) 항공우주 및 방위 그룹 기술 리더 / 아나로그디바이스

많은 레이더 시스템이 클러터 제거를 극대화하기 위해서 낮은 위상 잡음을 요구한다. 고성능 레이더일수록 위상 잡음을 더욱 까다롭게 다루기 때문에 합성기 위상 잡음을 낮추고, 합성기 부품의 특성을 분석하는 데 엄청난 시간과 비용을 투입하게 된다.

위상 잡음을 최대한 낮추기 위해서는 잡음이 낮은 전원장치를 사용해야 한다. 하지만 전원장치 잡음 전압이 위상 잡음에 얼마나 영향을 미치는지를 수치적으로 파악할 수 있는 체계적인 접근법은 나와 있지 않다. 이 글에서는 바로 이에 대해서 설명한다.

PSMR(power supply modulation ratio, 전원공급장치 변조 비율)은 전원장치 불완전성이 어떻게 RF 반송파로 변조되는지를 나타내는 기법이다. 이를 통해 RF 증폭기를 특성화 할 수 있으며, 그렇게 측정한 결과는 전원장치 잡음이 위상 잡음에 얼마나 영향을 미치는지를 대한 수치적으로 계산할 수 있으며, 꽤 정확하게 예측이 가능하다는 것을 보여준다. 또한 이러한 계산을 바탕으로, 전원장치 사양에 대한 시스템적인 접근도 가능하다.

머리말

PSMR은 잘 알려진 PSRR(power supply rejection ratio)과 비슷하게 들리기는 하지만 전혀 다르다. PSRR은 전원장치 불완전성이 출력에 얼마나 직접적으로 영향을 미치는지 나타낸다. 이에 반해 PSMR은 전원장치 리플과 잡음이 어떻게 RF 반송파로 변조되는지를 나타낸다.아래 ‘이론’ 부분에서는 전원장치 불완전성이 얼마나 반송파로 변조되는지를 수치적으로 나타내는 PSMR과 관련한 전달 함수인 H(s)에 대해서 소개한다. H(s)는 진폭 성분과 위상 성분으로 이루어지며, 주파수와 동작 조건에 따라서 달라진다. 수 많은 변수들이 있지만 일단 특성화 작업을 마치면, PSMR을 활용하여 전원장치로 인해 발생하는 위상 잡음과 스퓨리어스를 데이터 시트의 리플 및 잡음 사양을 토대로 정확하게 예측할 수 있다.

이론

RF 부품의 경우, DC 전원장치 리플이 어떻게 영향을 미치는지 살펴보자. 전원 리플은 피크-대-피크 전압이 DC 출력 즈음에서 중심을 이루는 사인파 신호로서 모델링할 수 있다. 이 사인파가 RF 반송파로 변조되는데, 사인파 주파수와 동일한 주파수 오프셋 지점에서 스퓨리어스 신호를 발생시킨다.

그림 1: 전원장치의 사인파 리플이 RF 반송파로 변조됨으로써 스퓨리어스 신호를 발생시킨다.

스퓨리어스의 크기는 사인파 진폭과 RF 회로 감도에 따른 함수이다. 스퓨리어스 신호는 다시 진폭 변조(AM) 성분과 위상 변조(PM) 성분으로 나눌 수 있다. 총 스퓨리어스 전력 레벨은 진폭 변조 성분으로 인한 스퓨리어스 전력과 위상 변조 성분으로 인한 스퓨리어스 전력을 합친 것이다.

아래에서 H(s)는 전원장치 불완전성이 RF 반송파로 원치 않게 변조되는 것을 나타내는 전달 함수이다. H(s)는 AM 성분과 PM 성분으로 나뉜다. H(s)의 AM 성분은 Hm(s)이고, H(s)의 PM 성분은 H∅(s)이다. 아래의 공식들은 H(s)를 RF 측정에 사용한 것으로, RF 반송파에 대한 전원장치의 영향으로 인해 발생하는 약간의 변조는 허용 가능한 것으로 간주한다.

신호의 진폭 변조는 다음과 같이 표현할 수 있다:

(1)

(1)진폭 변조 성분 m(t)는 다음과 같이 나타낼 수 있다:

(2)

(2)여기서 fm은 변조 주파수이다.

RF 반송파의 AM 변조 레벨은 다음과 같이 전원장치 리플과 직접적인 상관성을 갖는다:

(3)

(3)vrms는 공급 전압의 AC 성분의 rms 값이다. 공식 3은 전원장치 리플로 인한 RF 반송파의 AM 변조를 계산할 수 있는 중요한 공식이다.

진폭 변조로부터 다음과 같이 스퓨리어스 레벨을 계산할 수 있다:

(4)

(4)위상 변조에 대한 전원장치의 영향 역시 마찬가지이다. 위상 변조 신호는 다음과 같이 표현할 수 있다:

(5)

(5)그러면 위상 변조 항은 다음과 같이 나타낼 수 있다:

(6)

(6)위상 변조 역시 전원장치와 직접적인 상관성을 갖는다는 것을 알 수 있다:

(7)

(7)공식 7을 활용하면 전원장치 리플로 인한 RF 반송파의 PM 변조를 계산할 수 있다. 위상 변조로 인한 스퓨리어스 레벨은 다음과 같이 계산할 수 있다:

(8)

(8)그림 2는 mrms와 ∅rms가 스퓨리어스에 어떻게 영향을 미치는지 알 수 있도록, 스퓨리어스 레벨 대 mrms와 ∅rms의 관계를 보여준다.

그림 2: 스퓨리어스 대 mrms와 ∅rms

정리하면, 전원장치 리플은 전원장치 사인파 rms 전압인 vrms로부터 변조 항인 mrms와 ∅rms로 해석된다. Hm(s)와 H∅(s)는 vrms에서 각각 mrms 및 ∅rms로의 전달 함수이다.

이제, 위상 잡음을 살펴보자. 사인파가 반송파로 변조되어서 스퓨리어스 신호를 발생시키듯이, 1/f 전압 잡음 밀도가 반송파로 변조되어서 위상 잡음을 일으킨다.

그림 3: 전원장치의 1/f 잡음이 RF 반송파로 변조되어서 위상 잡음을 일으킨다.

신호 x(t)의 위상 변조는 다음과 같이 나타낼 수 있다:

(9)

(9)여기서 ∅(t)는 잡음 항이다.

전력 스펙트럼 밀도는 다음과 같이 정의된다:

, 단위는

, 단위는  (10)

(10)전력 스펙트럼 밀도로 인한 위상 잡음은 다음과 같다:

(11)

(11)다음으로, 전원장치 리플로 인한 위상 변조로부터 발생한 스퓨리어스 계산에 사용한 H∅(s)를 위상 잡음에도 똑같이 적용할 수 있다. 이 경우에는 H∅(s)를 사용해서 전원장치의 1/f 잡음으로 인한 위상 잡음을 계산한다.

(12)

(12) (13)

(13)

측정 사례

이러한 원리를 증명하기 위해, HMC589A RF 증폭기에 대해 여러 전원장치를 사용해서 전원장치 감도와 위상 잡음을 측정했다. 그림 4는 이 측정에 사용된 HMC589A 평가 회로를 보여준다.

그림 4: PSMR 원리를 증명하기 위해 HMC589A 증폭기를 사용했다.

먼저 전원장치 감도를 측정하기 위해, 5V 전원에 사인파를 인가했다. 이 사인파가 RF와 스퓨리어스 신호에 발생시킨 스퓨리어스를 dBc 단위로 측정했다. 스퓨리어스 성분을 다시 AM 성분과 PM 성분으로 나누었다. 계측장비로는 로데 슈바르츠(Rohde & Schwarz)의 FSWP26 위상 잡음 분석기와 스펙트럼 분석기를 사용했다. AM 및 PM 스퓨리어스 레벨은 각각 스퓨리어스 측정이 가능한 AM 및 PM 잡음 측정을 통해 측정했다. 표 1은 3.2GHz에 0dBm RF 입력을 사용한 테스트 결과를 나타낸 것이다.

표 1: HMC589A를 사용한 스퓨리어스 대 전원장치 사인파 리플 분석(3.2GHz 및 0dBm 입력 전력 사용)

| 입력 사인파 | 측정한 스퓨리어스 | 계산 결과 H(s) | ||||||

| 주파수 | V (rms) | 스퓨리어스 (dBc) | 스퓨리어스(dBc) AM | 스퓨리어스(dBc) PM | H (s) | H (s) AM | H (s) PM | |

| 100 | 0.01 | –52.2 | –57.3 | –53.7 | 0.35 | 0.19 | 0.29 | |

| 1000 | 0.01 | –52.4 | –57.2 | –54 | 0.34 | 0.20 | 0.28 | |

| 10000 | 0.01 | –53.5 | –58.3 | –55.3 | 0.30 | 0.17 | 0.24 | |

| 50000 | 0.0066 | –61 | –65 | –62.9 | 0.19 | 0.12 | 0.15 | |

이 테스트 데이터를 보면, 사인파 변조를 통해서 RF 증폭기 전원장치 감도를 경험적으로 측정할 수 있으며, 이 테스트 결과를 토대로 전원장치 잡음이 위상 잡음에 어떻게 기여할지 예측할 수 있다는 것을 알 수 있다. 여기서는 RF 증폭기를 가지고 살펴보고 있지만, 어떤 RF 부품이든 이런 식으로 계산하고 예측할 수 있다.

먼저, 비교적 잡음이 심한 전원장치부터 측정에 사용했다. 잡음 밀도를 측정했다. 전원장치가 위상 잡음에 미치는 영향을 H∅(s)를 바탕으로 계산하고, 이것을 실제 위상 잡음 측정과 비교했다. 측정을 위해서 로데 슈바르츠의 FSWP26 테스트 장비를 사용했다. 잡음 전압은 베이스밴드 잡음 측정을 이용해 측정했다. 증폭기 잔류 위상 잡음은 테스트 장비 내부의 오실레이터를 사용한 추가적인 위상 잡음 측정을 통해서 측정했다. 그림 5는 테스트 설정을 보여준다. 믹서에서 오실레이터 잡음을 제거하고, 교차 상관화 알고리즘을 사용해서 공통적이지 않은 잡음을 제거한다. 이렇게 함으로써 극히 낮은 수준의 잔류 잡음까지 측정할 수 있다.

그림 5: 교차 상관화 기법을 사용한 증폭기 잔류 위상 잡음 테스트 설정

그림 6은 전원장치 잡음, 실제로 측정된 위상 잡음, 전원장치로 인한 위상 잡음 기여분 예측을 보여준다. 그림을 보면 100Hz ~ 100kHz 오프셋 지점까지의 위상 잡음에 있어서 전원장치에 의한 것이 지배적임을 알 수 있다. 따라서 전원장치로 인해 발생한 위상 잡음 기여분 예측이 정확하게 이루어졌다는 것을 확인할 수 있다.

그림 6: 잡음이 심한 전원장치를 사용한 측정

추가적으로 두 개의 전원장치에 대해서도 동일한 방식으로 측정했다. 그림 7은 테스트 결과를 나타낸다. 여기서도 역시 전원장치로 인한 위상 잡음 기여분 예측이 거의 정확하게 이루어졌다는 것을 알 수 있다.

그림 7: 추가로 두 개의 전원장치를 사용한 측정 결과

위상 잡음이 낮은 부품에 대해서 측정할 때 중요한 것은, 측정이 주변 환경이 아니라 대상 디바이스에 대해서 이루어지도록 하는 것이다. 이 측정 실험에서 전원장치 기여분을 제거하기 위해서 ADM7150 저잡음 레귤레이터를 사용했다. 그림 8은 위상 잡음 테스트에 사용된 이 디바이스의 실제 잡음 전압 측정 결과와 데이트 시트에 표기된 잡음 밀도를 나타낸다.

그림 8: 저잡음 레귤레이터 ADM7150의 잡음 전압 밀도

표 2는 주요 저잡음 레귤레이터 제품들과 각각의 주요 파라미터를 정리한 것이다. 이들 제품은 모두 낮은 위상 잡음을 요구하는 RF 설계용으로 적합하다(구체적인 테스트 조건과 특성분석 곡선은 데이터시트 참조). 데이터 시트는 다양한 오프셋 주파수에 대한 잡음 밀도와 PSRR 곡선을 포함하고 있다. 이 표에서 잡음 밀도는 10kHz 오프셋에 대한 것이다. 많은 레귤레이터 제품이 이 구간이 한계이기 때문이다. PSRR은 1MHz 오프셋에 대한 것이다. 많은 선형 레귤레이터가 이 오프셋 지점에서 제거 능력을 상실하고 추가적인 필터링을 필요로 하기 때문이다.

| 부품 번호 | VIN 범위 | VOUT 범위 | IOUT | 고정/가변 | 잡음 밀도 @ 10 kHz | PSSR @ 1 MHz |

| LT3042 | 1.8 V ~ 20 V | 0 V ~ 15 V | 200 mA | 가변 | 2 nV/√Hz | 79 dB |

| LT3045, LT3045-1 | 1.8 V ~ 20 V | 0 V ~ 15 V | 500 mA | 가변 | 2 nV/√Hz | 76 dB |

| ADM7154 | 2.3 V ~ 5.5 V | 1.2 V ~ 3.3 V | 600 mA | 고정 | 1.5 nV/√Hz | 58 dB |

| ADM7155 | 2.3 V ~ 5.5 V | 1.2 V ~ 3.4 V | 600 mA | 가변 | 1.5 nV/√Hz | 57 dB |

| ADM7150 | 4.5 V ~ 16 V | 1.8 V ~ 5 V | 800 mA | 고정 | 1.7 nV/√Hz | >60 dB |

| ADP7156 | 2.3 V ~ 5.5 V | 1.2 V ~ 3.3 V | 1.2 A | 고정 | 1.7 nV/√Hz | 60 dB |

| ADP7157 | 2.3 V ~ 5.5 V | 1.2 V ~ 3.3 V | 1.2 A | 가변 | 1.7 nV/√Hz | 55 dB |

| ADP7158 | 2.3 V ~ 5.5 V | 1.2 V ~ 3.3 V | 2 A | 고정 | 1.7 nV/√Hz | 50 dB |

| ADP7159 | 2.3 V ~ 5.5 V | 1.2 V ~ 3.3 V | 2 A | 가변 | 1.7 nV/√Hz | 45 dB |

그림 9는 ADM7150을 사용했을 때 HMC589A의 잔류 위상 잡음 테스트 결과를 보여준다. 이것은 순수한 증폭기 성능을 보여주는 것으로서, 10kHz 오프셋에 이르기까지 잡음 플로어가 -170dBc/Hz 이하를 유지한다는 것을 알 수 있다.

그림 9: ADM7150 레귤레이터의 DC 전력을 사용했을 때 HMC589A의 잔류 위상 잡음 (3.2GHz 및 0dBm 입력 RF 전력 사용)

전원장치 사양을 도출하기 위한 체계적 방법

낮은 위상 잡음을 요구하는 애플리케이션을 위한 전원장치 설계는 통상적으로 실제적인 최소 사양과 관계없이, 활용가능한 최고의 레귤레이션 옵션을 선택하곤 한다. 수량이 적은 경우라면 이렇게 해도 무방하겠지만, 대량생산해야 하는 경우라면 성능, 비용, 복잡성을 모두 다 고려해야 하며 과도한 설계는 원치 않는 낭비가 될 수 있다.이를 방지하기 위해서는 다음과 같이 체계적이면서 수치적인 접근법으로 전원장치 사양을 도출해야 한다:

- 전원장치로부터의 사인파 변조를 활용해 H(s)를 분석한다. H(s)는 주파수의 함수이며, 모든 10Hz 단위로 테스트한다.

- RF 사양 내에서 약간의 마진을 갖고, 스퓨리어스 및 위상 잡음에 대한 전원장치 기여분을 감안한다.

- 전원장치 리플 사양을 계산한다:

(14)

(14)- 전원장치 잡음 사양을 계산한다:

(15)

(15)위의 1단계에서는 해당 설계에 예상되는 동작 조건으로 Hm(s)와 H∅(s)가 어떻게 변화할지 이해해야 한다. 그림 10은 다양한 전력 레벨에 따른 HMC589A에 대한 측정 결과를 보여준다.

그림 10: 3.2GHz에서 HMC589A 평가 회로를 활용한 Hm(s) 및 H∅(s)대 오프셋 주파수 및 전력 레벨 측정

제품스펙