기술기고문

28nm ADC를 활용한 차세대 전자전 리시버 시스템 설계의 이점

28nm ADC를 활용한 차세대 전자전 리시버 시스템 설계의 이점

글: 데이빗 브라운(David Brown), 피터 델로스(Peter Delos) / 아나로그디바이스

머리말

전자전(electronic warfare, EW) 리시버 시스템, 특히 신호 정보(signal intelligence, SIGINT) 애플리케이션에서는 갈수록 더 높은 대역폭과 더 작은 크기, 경량, 저전력(SWaP) 특성이 요구됨에 따라, EW 시스템 설계자들은 계속해서 보다 향상된 고속 아날로그-디지털 컨버터(ADC) 기술을 찾아왔다. 65nm ADC는 성능과 대역폭이 공정 자체의 한계에 도달했는데, 새로운 28nm RF ADC가 이러한 한계를 극복하고 차세대 광대역 리시버 시스템을 설계할 수 있는 새로운 토대를 제공하고 있다. 28nm 공정 노드는 트랜지스터 폭이 축소되고 기생성분이 줄어들기 때문에 더 빠른 샘플링 속도와 더 넓은 아날로그 입력 대역폭, 디지털 기능 통합, 새로운 리시버 아키텍처 구현이 가능해 전력 소모와 전반적인 크기를 줄여준다.

28nm ADC의 이점

현대전에서 광대역 EW 시스템 사용이 갈수록 늘어남에 따라서, 차세대 EW 리시버가 필요로 하는 고성능과 더 낮은 SWaP 요건을 충족하는 것이 시스템 설계자들의 과제가 되었다. 고속 ADC는 모든 광대역 EW 리시버 설계에서 중요한 고려사항 중의 하나로서, 시스템 아키텍처와 전반적인 감지 및 관측 능력에 중대한 영향을 미친다. 고속 ADC의 샘플링 속도, 대역폭, 분해능 같은 성능 특성에 따라서, 아날로그 RF 영역에서부터 DSP 요구 조건에 이르기까지 리시버의 나머지 부분이 결정된다. EW 시스템 설계자들은 차세대 EW 리시버 개발을 위해 끊임없이 보다 높은 ADC 대역폭과 분해능을 요구해 왔다. 샘플링 속도와 대역폭이 높을수록 한번에 더 넓은 스펙트럼을 디지털화할 수 있으므로 RF 영역의 어려움을 완화하고 스위핑 시간을 단축할 수 있으며, 비트 깊이가 클수록 성능을 높이고 잘못된 경보 및 감지를 줄일 수 있다. 이처럼 더 높은 샘플링 속도와 분해능에 대한 요구를 충족하기 위해 고속 ADC 제조회사들은 디바이스 전력 소모를 늘리지 않으면서도 이러한 성능 향상 목표를 달성할 수 있게 해주는 보다 미세화 한 트랜지스터 리소그래피 노드로 꾸준히 이전해 왔다(현재는 28nm와 16nm까지 와 있는 상태이다).

28nm ADC는 차세대 광대역 EW 리시버를 구현하는 데 있어 꼭 필요한 근본적인 이점들을 제공한다. 28nm 트랜지스터는 기생 게이트 커패시턴스가 줄어들기 때문에, 스위칭에 필요한 에너지가 적어 더 빠른 스위칭이 가능하다. 또한 물리적 트랜지스터 크기가 더 작기 때문에 ADC가 더 빠른 샘플링 속도를 달성할 수 있을 뿐 아니라 평방 mm당 더 많은 수의 트랜지스터를 집적할 수 있다. 그 결과, 더 높은 디지털 프로세싱 성능을 구현할 수 있다. 또한 근본적으로 전력 소모가 더 낮기 때문에, 28nm 공정을 적용한 ADC는 이전에 65nm 이상의 공정으로는 기대할 수 없던 성능과 기능들을 차세대 EW 시스템에서 달성할 수 있다. 대부분의 EW 시스템 설계자들, 특히 SIGINT, 전자 보호(electronic protect, EP), 전자 지원(electronic support, ES) 애플리케이션 분야의 설계자들이 보기에 28nm ADC의 가장 매력적인 특성은 더 높은 샘플링 속도(수 GSPS 이상)를 달성할 수 있다는 점일 것이다. 대역폭과 마찬가지로 분해능 역시 중요하다. 더 높은 분해능은 더 우수한 SNR/SFDR을 뜻하며, 그러면 목표한 신호를 감지 및 관측, 처리하는 능력 또한 우수해진다. 또한 아날로그 입력 대역폭이 넓어 1차 나이퀴스트 이상으로 언더샘플링이 가능해진다.

28nm 공정으로의 전환은 혼성신호 반도체 회사들이 시스템 SWaP를 늘리지 않고서, 심지어는 이를 줄이기까지 하면서 자신들의 고속 ADC에 더 많은 양의 디지털 신호 프로세싱과 기능을 집적할 수 있게 해주었다. NCO(numerically controlled oscillator)나 DDC(digital downconverter) 같은 디지털 기능을 통합함으로써 컨버터 성능의 한계를 끌어올릴 뿐 아니라, 높은 데이터 변환 속도와 높은 디지털 인터페이스 전력 소모와 관련된 시스템 설계 상의 어려움을 완화할 수 있게 되었다. 또한 축소된 28nm 공정을 활용해서 ADC의 온칩 DSP 성능을 높임으로써 프로세서의 처리 부담과 전력 소모를 훨씬 낮출 수 있다. 이로써 시스템 SWaP를 더 줄일 수 있다.

더 빠른 28nm ADC는 RF 스펙트럼 상의 더 넓은 범위를 포착할 수 있지만, ADC 나이퀴스트 대역폭과 비교하면 해당 신호는 여전히 비교적 작은 대역폭일 수 있다. 또한 GSPS ADC로부터 대량의 데이터 쓰루풋이 발생하기 때문에 적합한 프로세서를 찾아서 이를 ADC에 물리적으로 인터페이싱하기가 어려울 수 있다. 현재 출시되어 있는 많은 28nm 컨버터는 레인 속도가 10Gbps 이상인 JESD204B 인터페이스 표준을 사용한다. 그러면 Gbps SERDES(serializer/deserializer) JESD 레인을 배선할 때 보드 레이아웃과 신호 무결성이 문제가 될 수 있다. 하지만 다행히도 통합 NCO/DDC와 온칩 DSP를 활용함으로써, ADC가 해당 신호를 더 낮은 주파수 대역이나 기저 대역으로 변환하고, 디지털 필터링을 적용하여, 디지털 데이터 출력 속도를 데시메이션(decimation)할 수 있다. 그러면 포착한 스펙트럼을 분할하여 좀더 집중적인 프로세싱 수행이 가능하다. 튜닝이 가능한 NCO를 사용하면 디지털화 한 스펙트럼을 DDC가 스윕하면서 전체 스펙트럼 분석이 가능할 뿐 아니라, 이 외에도 프로세싱 이득을 높이고 디지털 데이터 출력 레이트를 더 낮출 수 있는 추가적인 이점도 누릴 수 있다. 여러 개의 NCO와 DDC를 병렬로 추가하면 NCO 튜닝이 불필요하며 사용자가 사전 설정을 해서 DDC 간에 빠른 스위칭과 호핑이 가능하여 스위핑 시간을 추가적으로 더 단축할 수 있다. 또한 DDC를 통합함으로써 디지털 JESD204B 인터페이스에서 상당한 전력 절감을 할 수 있다. 이렇게 높은 속도로 실행되는 JESD SERDES는 시스템 전력 소모를 1W 이상 늘릴 수 있다. 그러므로 데이터 속도를 더 낮게 데시메이션 하는 것은 이런 관점에서 매우 유익하다. 고속 ADC가 계속해서 더 높은 샘플링 속도, 비트 깊이, 대역폭을 추구함에 따라서, DDC와 ADC를 통합하는 것이 광대역 EW 리시버 시스템 설계자들에게는 상당한 매력을 제공한다. SWaP가 낮은 프로세서를 사용해서는 ADC로부터 들어오는 방대한 양의 디지털 데이터를 처리하기가 어려울 수 있기 때문이다. DDC와 실제 사례에 대한 자세한 정보는 조나단 해리스(Jonathan Harris)의 “디지털 다운컨버터에 무슨 일이 일어나고 있는가?” 1부와 2부를 참고하기 바란다.

새로운 리시버 아키텍처 실현

헤테로다인 리시버 아키텍처는 잘 알려져 있으며 지난 수년 동안 검증되어 왔다. 지금까지 많은 마이크로파 리시버들이 듀얼 하향변환 아키텍처를 사용해서 구현되어 왔다. 이전 세대의 ADC들은 ADC 입력 주파수에 대한 동작 대역 주파수의 비율이 높아서 단일 하향변환 리시버 아키텍처로는 이미지 필터링을 하기가 현실적으로 어려웠다. 새로운 ADC들은 샘플링 속도와 아날로그 입력 대역폭이 둘 다 높아짐으로써, 고성능 광대역 단일 하향변환 아키텍처가 현실적으로 가능하고 구현하기도 쉬워졌다.

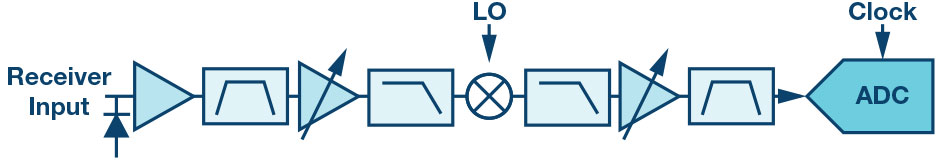

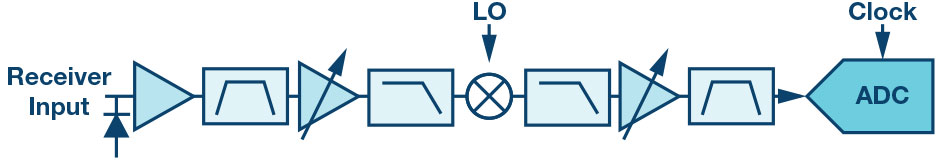

그림 1은 단일 하향변환 리시버 아키텍처를 나타낸 것이다. 잡음 수치 성능을 위해 프런트엔드에 LNA를 사용하였다. 필요하다면 LNA 앞에 리미터를 추가함으로써 프런트엔드가 견딜 수 있는 전력 능력을 높일 수 있다. 그 다음에는 동작 대역 필터를 사용해서 대역외 간섭을 감쇠시킨다. 그 다음에는 이득과 이득 제어를 필요한 만큼 추가할 수 있다. 믹서 앞에는 저역통과 필터를 사용해서 스퓨리어스 출력으로 추가되는 RF 고조파를 낮출 수 있다. 믹서는 매우 핵심적인 빌딩 블록으로서 해당 주파수 변환 대역에서 성능을 극대화하도록 선택해야 한다. 믹서 다음에 오는 또 다른 저역통과 필터는 증폭하기 전에 상단 측대역을 필터링한다. 그리고 필요에 따라서 IF 이득을 추가한다. 앨리어싱 방지 필터는 ADC 바로 앞에 위치하는 최종 소자로서, 샘플링 과정에서 대역 내로 폴딩되어 들어올 수 있는 주파수를 제거한다. 그 다음은 ADC이다. ADC는 이 체인 상에서 맨 뒤에 있으나, 설계를 할 때는 ADC를 가장 먼저 선택하고 ADC를 중심으로 리시버의 나머지 부분을 설계하는 것이 일반적이다.

그림 1: 단일 하향변환 리시버 아키텍처의 예

다음은 주파수 플랜을 선택할 때 고려사항이다. 주파수 플랜이란, 구할 수 있는 소자들로 설계를 구현할 때, 적정한 필터 제품을 가지고 스퓨리어스 발생을 최소화 할 수 있는 주파수 변환 방법을 선택하는 것을 말한다. RF 엔지니어들이 처음에 이 결정을 내려야 할 때, 다양한 선택지가 있고 적절한 주파수 플랜을 달성하기 위해서는 여러 번의 반복이 필요할 수 있기 때문에 결정하기가 쉽지는 않다. 다행히도, 향상된 최신 CAD 툴과 다양한 소자 제품들을 활용할 수 있게 되면서 이러한 주파수 플랜 작업이 많이 수월해졌다.

일반적으로 스퓨리어스 관점에서 보면, 2차 또는 3차 나이퀴스트 영역의 높은 IF 주파수가 선호된다. 하나의 예로서, 10GHz 동작 대역을 3GHz ADC의 1차 나이퀴스트 영역으로 변환하는 주파수 플랜의 이점과, 2차 나이퀴스트 영역에서 동작하는 주파수 플랜의 이점을 살펴보자.

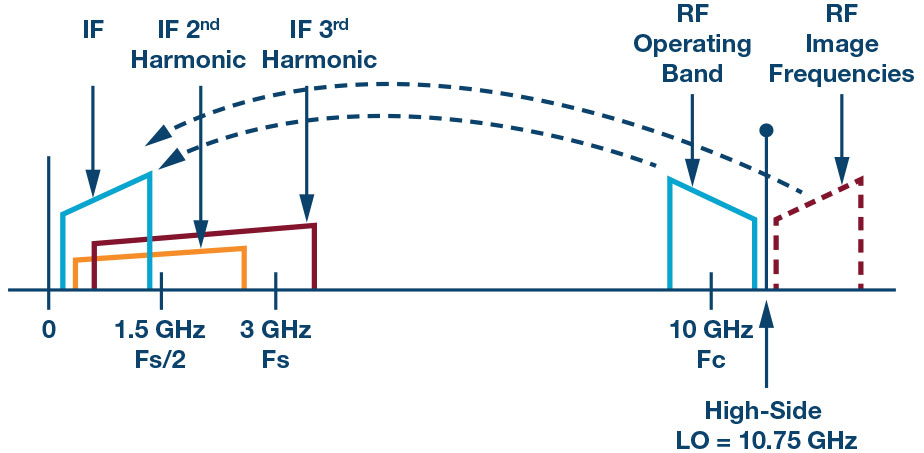

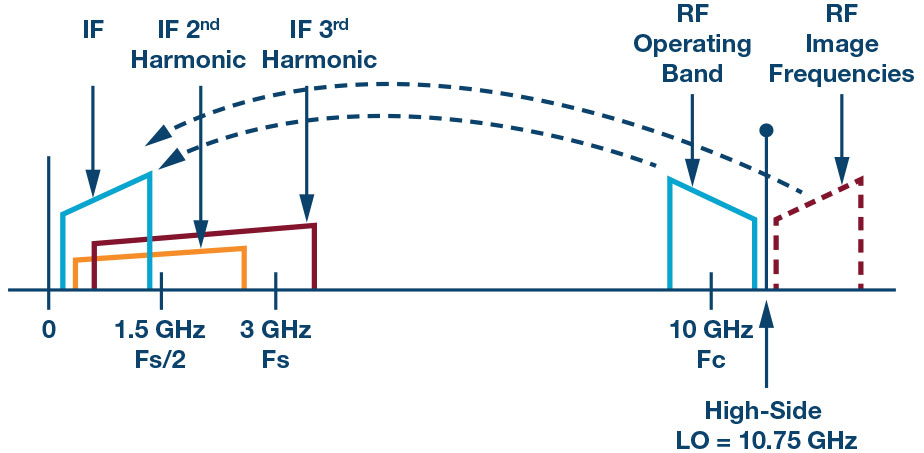

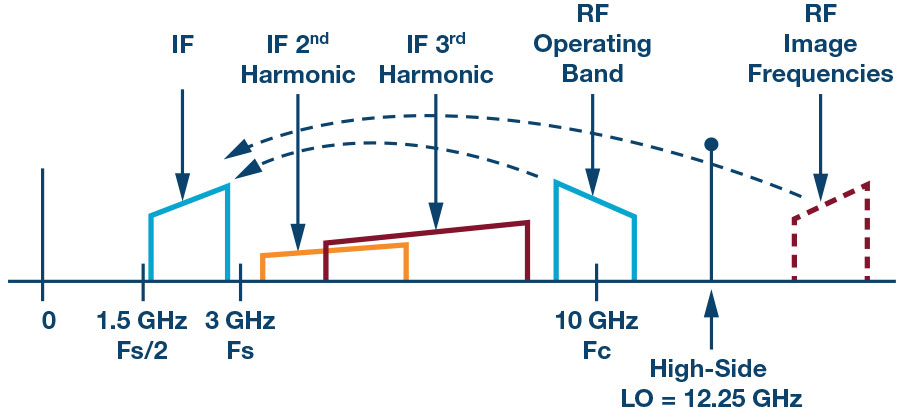

그림 2는 10GHz에서 1GHz 동작 대역을 3GSPS ADC의 1차 나이퀴스트 영역으로 변환하는 것을 보여준다. 두 가지 문제를 알 수 있다. 첫째, RF 이미지 주파수가 동작 대역과 간격이 아주 가깝기 때문에 이미지 억제를 위해서 매우 까다로운 필터 설계가 필요하다. 둘째, IF 증폭 스테이지에서 발생하는 IF가 대역내에 들어오기 때문에 앨리어싱 방지 필터를 사용해서 필터링하는 것이 불가능하다.

그림 2: 문제가 있는 주파수 플랜. IF 고조파가 IF 대역 내로 들어오므로 이미지 필터링이 어렵다.

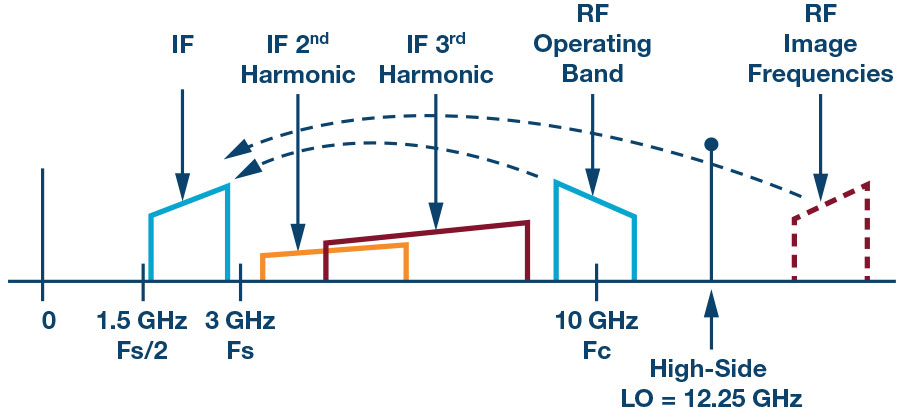

이와 달리, 그림 3은 동일한 RF 동작 대역을 2차 나이퀴스트 영역으로 샘플링하는 것을 보여준다. IF 주파수가 더 높기 때문에 이미지 주파수가 동작 대역으로부터 훨씬 멀리 떨어진다. 따라서 RF 이미지 필터를 구현하기가 훨씬 쉽다. 또 IF 증폭기에서 발생하는 어떤 고조파이든 앨리어싱 방지 필터를 사용해서 필터링할 수 있으며, 유일하게 발생하는 IF 고조파는 ADC 자체 내에서 발생하는 것뿐이다.

그림 3: 개선된 주파수 플랜. IF 고조파가 IF 대역 바깥에 있다. 따라서 이미지 필터링이 가능하다.

키사이트 제네시스(Keysight Genesys) 툴의 스퍼 분석을 통해서도 같은 결과가 나온다는 것을 알 수 있다. 그림 4는 WhatIF 주파수 플랜 툴을 사용한 결과이다. 10GHz 동작 주파수 대역, 1GHz 순간 대역폭, 하이사이드 LO 선택, 5차 스퓨리어스 탐색으로 설정되었다. 스퓨리어스가 발생하지 않는 영역은 녹색으로 표시되었다. 이 경우에서는 3GSPS ADC의 2차 나이퀴스트 영역에 해당된다.

그림 4: 키사이트 제네시스 WhatIF 주파수 플랜 툴을 사용한 스퍼 분석

새로운 솔루션

주파수 플랜 분석을 한 다음에는 믹서와 ADC를 해당 동작 조건으로 평가해서 스퓨리어스와 잡음 성능을 확인해야 한다.

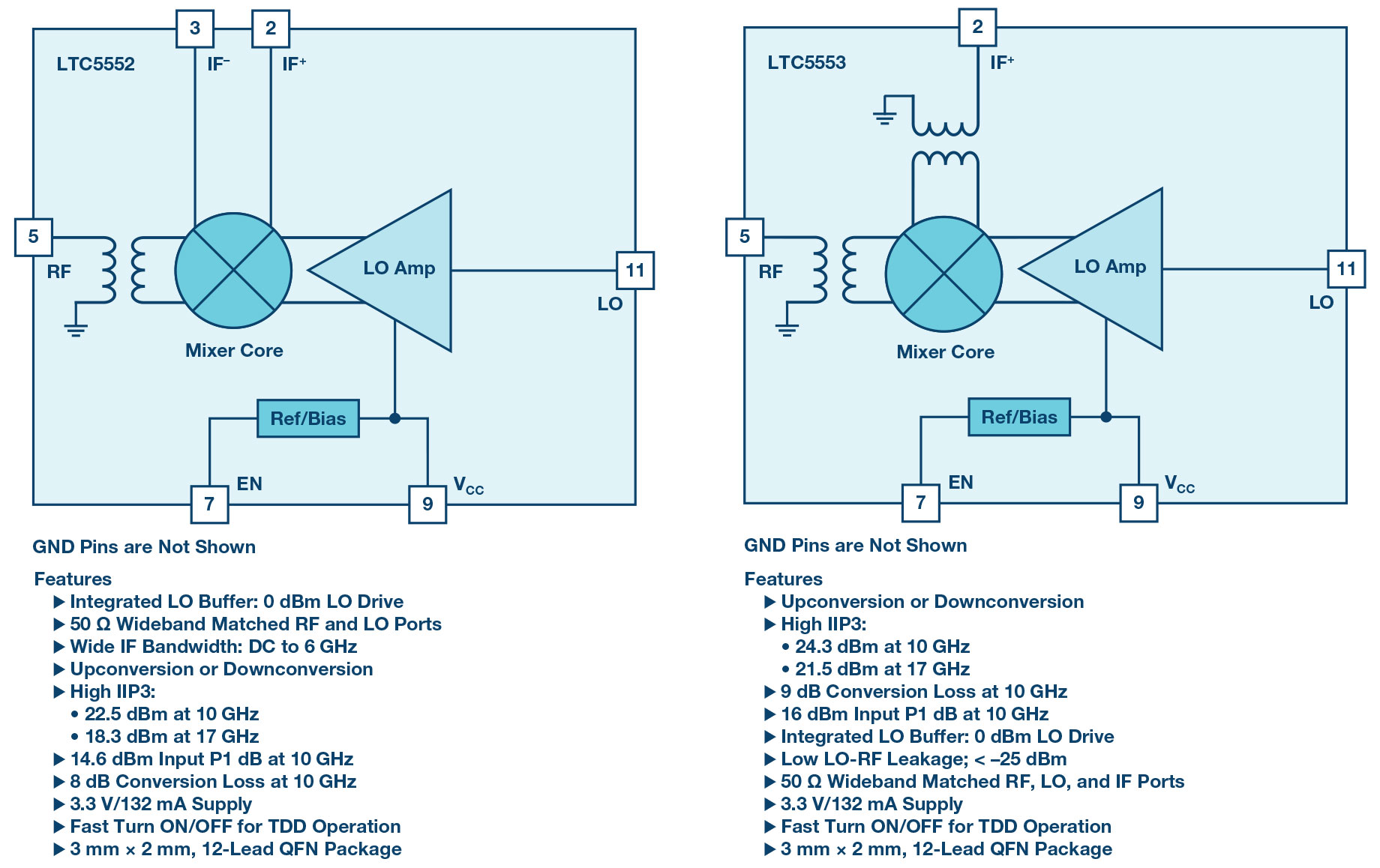

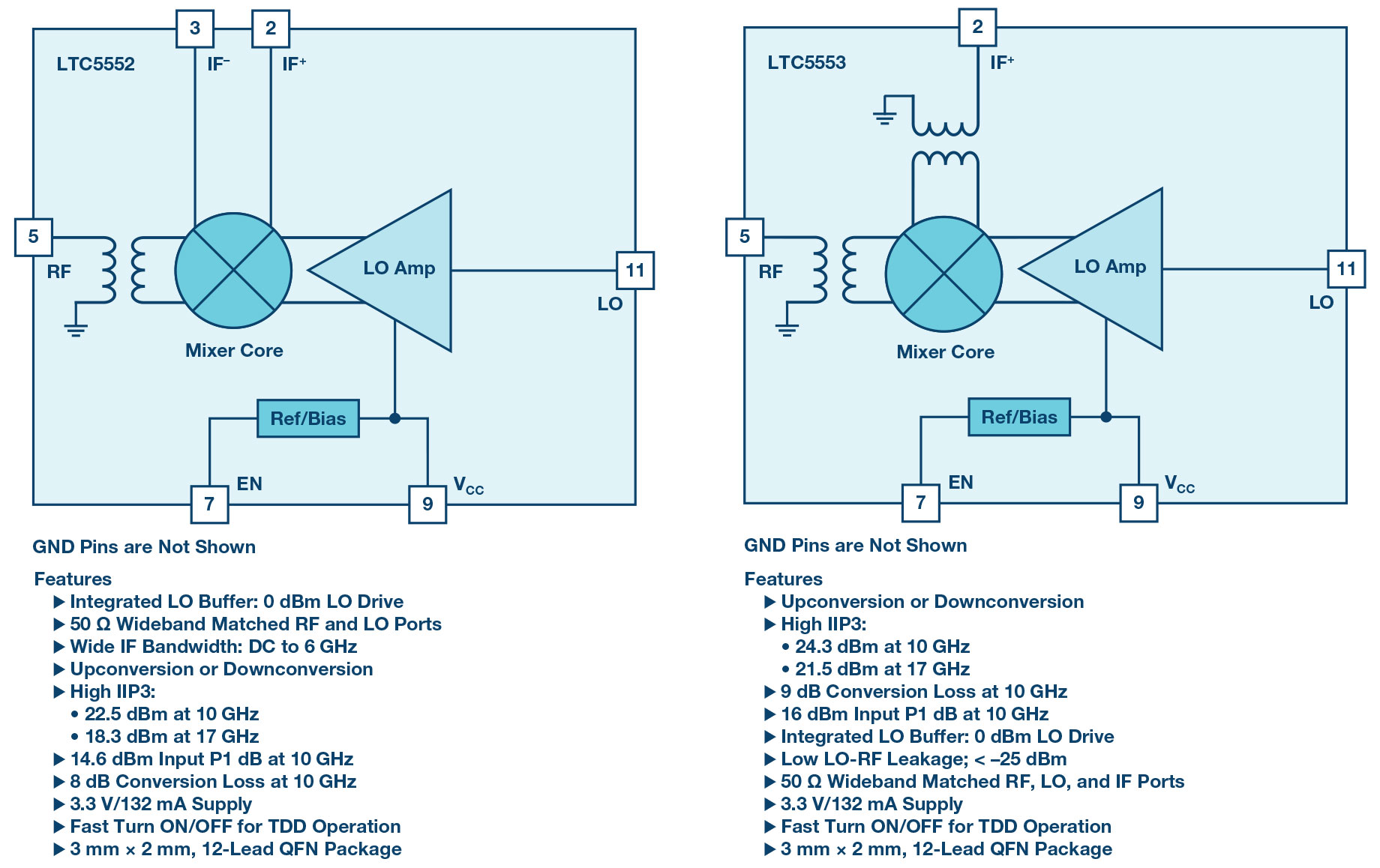

LTC5552와 LTC5553은 최근에 출시된 고성능 3GHz~20GHz 믹서 제품이다. 그림 5는 이들 제품의 주요 특징을 보여준다. 이들 제품은 동급 최고 성능의 고 선형성 광대역 믹서 제품으로서, 광대역 리시버 아키텍처에 곧바로 사용하기에 적합하다. 두 제품의 차이점은, LTC5552는 차동 IF 출력이고, LTC5553은 모든 포트가 싱글 엔디드(singled ended)라는 것이다. 차동 IF 출력이면 전체적인 IF 사슬이 차동을 유지할 수 있으므로, ADC 입력에 통상적으로 추가되는 밸런(balun)을 제거할 수 있다. 완전 차동 IF 섹션을 실제 구현할 수 있으므로 차동 IF 증폭기를 즉시 사용할 수 있으며, 이를 위한 설계 수정 사항은 IF 신호 체인으로 차동 필터를 도입하는 것뿐이다.

그림 5: 광대역, 고성능, 고 선형성 믹서

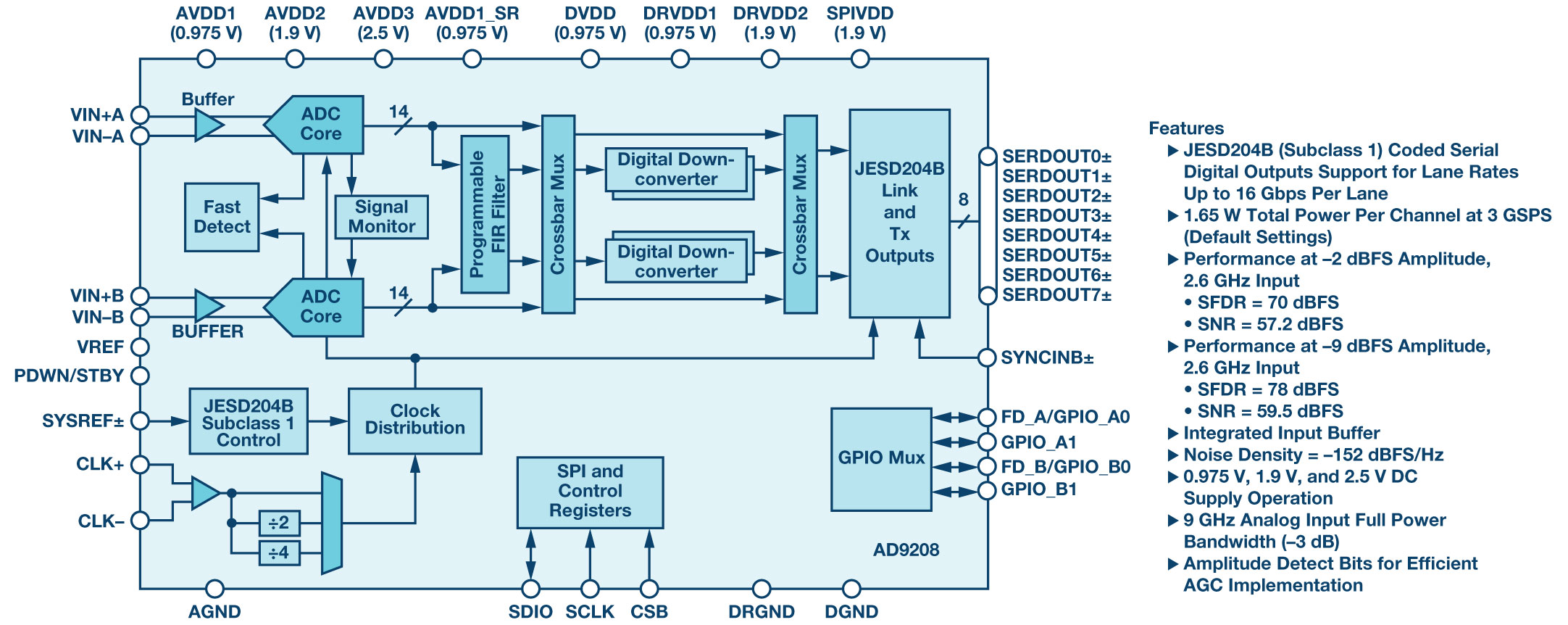

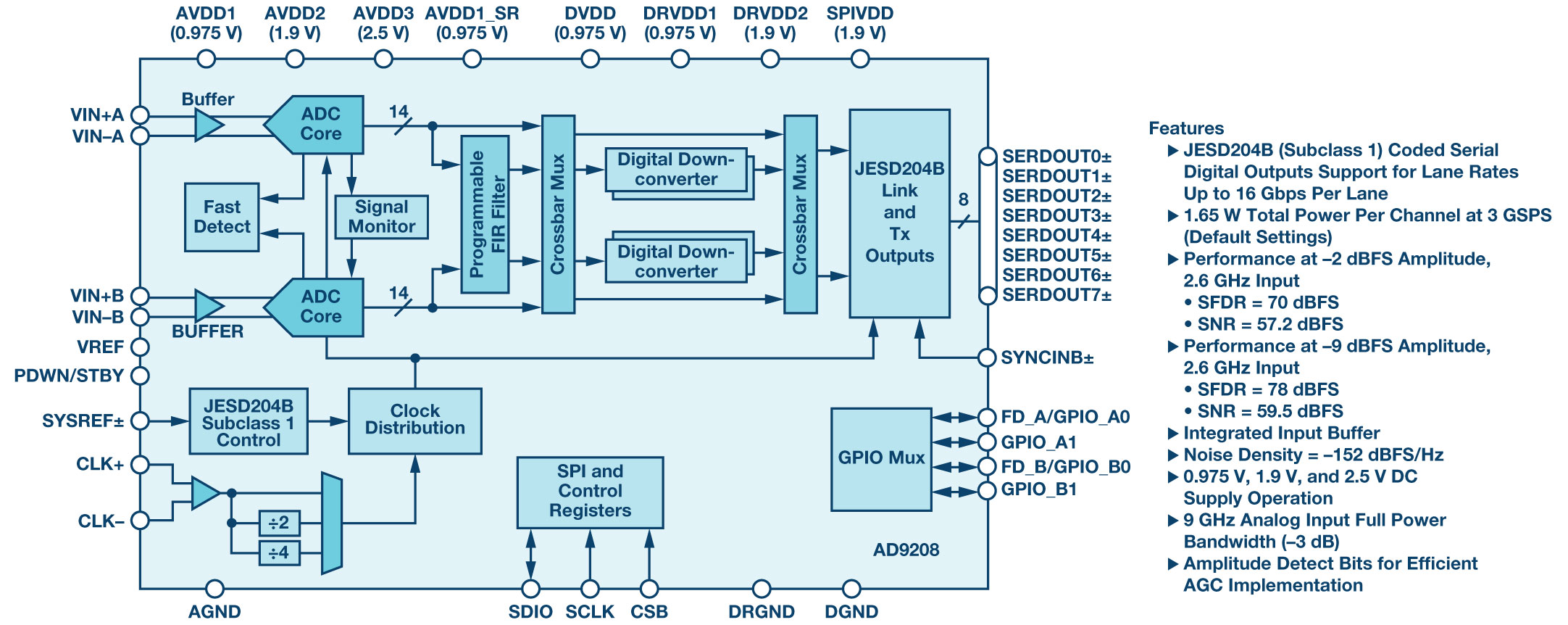

그림 6: AD9208. 28nm를 적용한 3GSPS, 고성능, 넓은 입력 대역폭의 ADC

AD9208은 28nm를 적용한 14bit 3GSPS 듀얼 ADC 제품이다. 높은 입력 대역폭과 샘플링 분해능을 제공하며, 디지털 기능으로 4개의 DDC와 NCO를 통합하고 있어 다양한 EW 리시버 시스템 및 애플리케이션에 적합하다. 또한 아날로그 입력 대역폭이 9GHz로 높아 곧바로 2차 및 3차 나이퀴스트 주파수로 샘플링 할 수 있다. 깨끗하고 지터가 낮은 레퍼런스 클록을 사용하면 4차 나이퀴스트 샘플링도 가능하다. 그러면 높은 입력 주파수에서도 SNR 저하를 최소화할 수 있다.

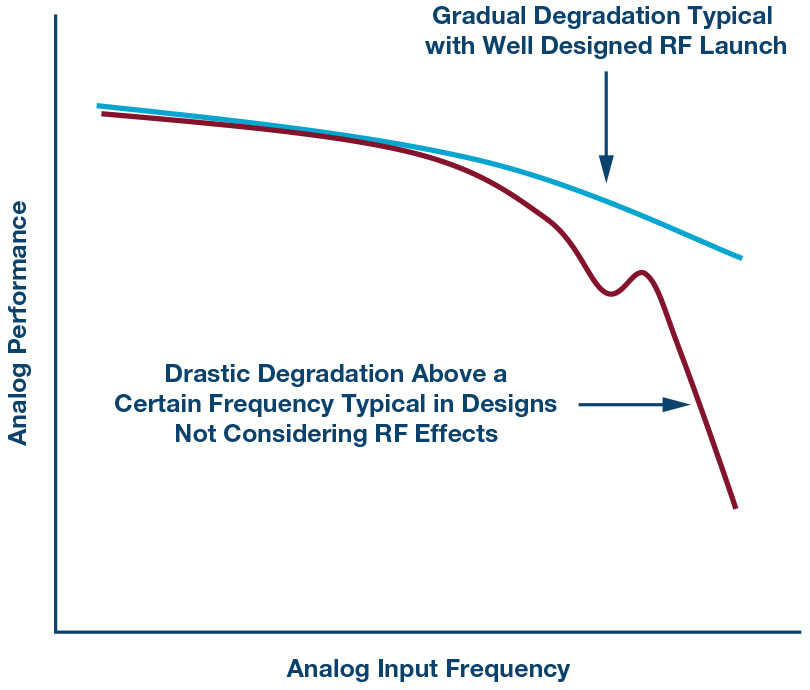

RF 리시버 설계자에게 항상 문제가 되는 것은, 입력 주파수가 높아지면 ADC의 모든 중요한 특성들이 저하된다는 것이다. 이것은 잡음과 스퓨리어스가 둘 다 없는 동적 범위도 마찬가지다. 실리콘의 한계 외에도, GHz 컨버터로 입력 대역폭을 유지하기 위해서는 실리콘에서부터 패키지 라미네이트에 이르기까지, 또한 패키지에서부터 PWB에 이르기까지 신중한 설계가 요구된다.

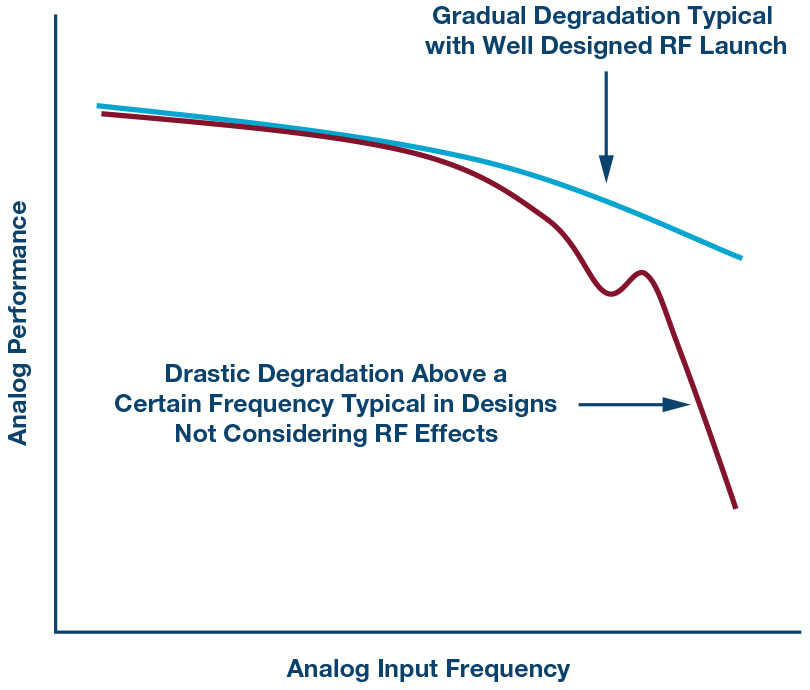

그림 7: 아날로그 성능. SNR, SFDR, 신호 전력이 모두 입력 주파수에 따라 저하되는 것을 알 수 있다.

높은 IF 샘플링을 필요로 하는 설계는 선택한 ADC가 입력 주파수에 따라서 특성이 심각하게 저하되지 않는지 확인해야 한다. 또한 PWB 설계로 구현할 때에는 신중한 RF 레이아웃이 필요하다.

잘 설계된 RF I/O 구조에서는 입력 주파수에 따른 성능저하가 급격하지 않다. 하지만, 설계가 잘못되면 특정 입력 주파수 지점에서 성능이 갑자기 뚝 떨어질 수 있다. 그림 7은 이것을 보여준다. 애플리케이션에 사용하기 위한 컨버터를 선택하기 위해서는 실제 설계에 앞서서 충분한 시간을 들여서 성능을 잘 확인해야 한다. GHz 대의 주파수로 동작하는 RF 샘플링 ADC는 더욱 그렇다. 특정 애플리케이션에 사용하기 위한 ADC를 선택하기 앞서서 주파수에 따른 성능 특성을 잘 파악할 필요가 있다.

맺음말

이 글에서는 광대역 애플리케이션과 리시버 설계 고려사항을 살펴보았다. EW 애플리케이션은 특히나 요구가 까다롭다. 넓은 동작 대역과 가능한 높은 순간 대역폭을 지원하는 리시버를 요구하기 때문이다. 단일 하향변환 리시버 아키텍처로 높은 차수의 ADC 나이퀴스트 영역으로 동작하면 스퓨리어스 성능을 향상시킬 수 있다. 이를 위해서는 ADC의 입력 대역폭과 믹싱 스테이지의 성능 파라미터가 어려운 과제이다. 다행히 넓은 입력 주파수 범위를 지원하는 고속 28nm ADC와 광대역 고 선형성 믹서 제품들이 출시됨으로써 차세대 리시버 설계의 토대가 마련됐다.

저자 소개

데이빗 브라운(David Brown)은 아나로그디바이스(Analog Devices, 노스캐롤라이나주 그린스버로 소재)의 RF 시스템 애플리케이션 엔지니어이다. 2015년에 ADI에 입사했으며, 항공우주 및 방위산업 애플리케이션을 담당하고 있다. 2014년에 노스캐롤라이나 주립대학에서 전기공학 학사학위를 취득했다. david.brown@analog.com

피터 델로스(Peter Delos)는 아나로그디바이스(Analog Devices, 노스캐롤라이나주 그린스버로 소재)의 항공우주 및 방위산업 그룹 기술 책임자이다. 1990년에 버지니아 공대에서 전기공학 학사학위를, 2004년에 뉴저지 공대에서 전기공학 석사학위를 취득했다. 25년 넘게 이 분야에 종사해 오면서 아키텍처, PWB, IC 차원에서 첨단 RF/아날로그 시스템 설계를 주로 해왔다. 현재 위상 어레이 애플리케이션용 고성능 리시버, 파형 발생기, 합성기 설계 소형화에 매진하고 있다. peter.delos@analog.com

글: 데이빗 브라운(David Brown), 피터 델로스(Peter Delos) / 아나로그디바이스

머리말

전자전(electronic warfare, EW) 리시버 시스템, 특히 신호 정보(signal intelligence, SIGINT) 애플리케이션에서는 갈수록 더 높은 대역폭과 더 작은 크기, 경량, 저전력(SWaP) 특성이 요구됨에 따라, EW 시스템 설계자들은 계속해서 보다 향상된 고속 아날로그-디지털 컨버터(ADC) 기술을 찾아왔다. 65nm ADC는 성능과 대역폭이 공정 자체의 한계에 도달했는데, 새로운 28nm RF ADC가 이러한 한계를 극복하고 차세대 광대역 리시버 시스템을 설계할 수 있는 새로운 토대를 제공하고 있다. 28nm 공정 노드는 트랜지스터 폭이 축소되고 기생성분이 줄어들기 때문에 더 빠른 샘플링 속도와 더 넓은 아날로그 입력 대역폭, 디지털 기능 통합, 새로운 리시버 아키텍처 구현이 가능해 전력 소모와 전반적인 크기를 줄여준다.

28nm ADC의 이점

현대전에서 광대역 EW 시스템 사용이 갈수록 늘어남에 따라서, 차세대 EW 리시버가 필요로 하는 고성능과 더 낮은 SWaP 요건을 충족하는 것이 시스템 설계자들의 과제가 되었다. 고속 ADC는 모든 광대역 EW 리시버 설계에서 중요한 고려사항 중의 하나로서, 시스템 아키텍처와 전반적인 감지 및 관측 능력에 중대한 영향을 미친다. 고속 ADC의 샘플링 속도, 대역폭, 분해능 같은 성능 특성에 따라서, 아날로그 RF 영역에서부터 DSP 요구 조건에 이르기까지 리시버의 나머지 부분이 결정된다. EW 시스템 설계자들은 차세대 EW 리시버 개발을 위해 끊임없이 보다 높은 ADC 대역폭과 분해능을 요구해 왔다. 샘플링 속도와 대역폭이 높을수록 한번에 더 넓은 스펙트럼을 디지털화할 수 있으므로 RF 영역의 어려움을 완화하고 스위핑 시간을 단축할 수 있으며, 비트 깊이가 클수록 성능을 높이고 잘못된 경보 및 감지를 줄일 수 있다. 이처럼 더 높은 샘플링 속도와 분해능에 대한 요구를 충족하기 위해 고속 ADC 제조회사들은 디바이스 전력 소모를 늘리지 않으면서도 이러한 성능 향상 목표를 달성할 수 있게 해주는 보다 미세화 한 트랜지스터 리소그래피 노드로 꾸준히 이전해 왔다(현재는 28nm와 16nm까지 와 있는 상태이다).

28nm ADC는 차세대 광대역 EW 리시버를 구현하는 데 있어 꼭 필요한 근본적인 이점들을 제공한다. 28nm 트랜지스터는 기생 게이트 커패시턴스가 줄어들기 때문에, 스위칭에 필요한 에너지가 적어 더 빠른 스위칭이 가능하다. 또한 물리적 트랜지스터 크기가 더 작기 때문에 ADC가 더 빠른 샘플링 속도를 달성할 수 있을 뿐 아니라 평방 mm당 더 많은 수의 트랜지스터를 집적할 수 있다. 그 결과, 더 높은 디지털 프로세싱 성능을 구현할 수 있다. 또한 근본적으로 전력 소모가 더 낮기 때문에, 28nm 공정을 적용한 ADC는 이전에 65nm 이상의 공정으로는 기대할 수 없던 성능과 기능들을 차세대 EW 시스템에서 달성할 수 있다. 대부분의 EW 시스템 설계자들, 특히 SIGINT, 전자 보호(electronic protect, EP), 전자 지원(electronic support, ES) 애플리케이션 분야의 설계자들이 보기에 28nm ADC의 가장 매력적인 특성은 더 높은 샘플링 속도(수 GSPS 이상)를 달성할 수 있다는 점일 것이다. 대역폭과 마찬가지로 분해능 역시 중요하다. 더 높은 분해능은 더 우수한 SNR/SFDR을 뜻하며, 그러면 목표한 신호를 감지 및 관측, 처리하는 능력 또한 우수해진다. 또한 아날로그 입력 대역폭이 넓어 1차 나이퀴스트 이상으로 언더샘플링이 가능해진다.

28nm 공정으로의 전환은 혼성신호 반도체 회사들이 시스템 SWaP를 늘리지 않고서, 심지어는 이를 줄이기까지 하면서 자신들의 고속 ADC에 더 많은 양의 디지털 신호 프로세싱과 기능을 집적할 수 있게 해주었다. NCO(numerically controlled oscillator)나 DDC(digital downconverter) 같은 디지털 기능을 통합함으로써 컨버터 성능의 한계를 끌어올릴 뿐 아니라, 높은 데이터 변환 속도와 높은 디지털 인터페이스 전력 소모와 관련된 시스템 설계 상의 어려움을 완화할 수 있게 되었다. 또한 축소된 28nm 공정을 활용해서 ADC의 온칩 DSP 성능을 높임으로써 프로세서의 처리 부담과 전력 소모를 훨씬 낮출 수 있다. 이로써 시스템 SWaP를 더 줄일 수 있다.

더 빠른 28nm ADC는 RF 스펙트럼 상의 더 넓은 범위를 포착할 수 있지만, ADC 나이퀴스트 대역폭과 비교하면 해당 신호는 여전히 비교적 작은 대역폭일 수 있다. 또한 GSPS ADC로부터 대량의 데이터 쓰루풋이 발생하기 때문에 적합한 프로세서를 찾아서 이를 ADC에 물리적으로 인터페이싱하기가 어려울 수 있다. 현재 출시되어 있는 많은 28nm 컨버터는 레인 속도가 10Gbps 이상인 JESD204B 인터페이스 표준을 사용한다. 그러면 Gbps SERDES(serializer/deserializer) JESD 레인을 배선할 때 보드 레이아웃과 신호 무결성이 문제가 될 수 있다. 하지만 다행히도 통합 NCO/DDC와 온칩 DSP를 활용함으로써, ADC가 해당 신호를 더 낮은 주파수 대역이나 기저 대역으로 변환하고, 디지털 필터링을 적용하여, 디지털 데이터 출력 속도를 데시메이션(decimation)할 수 있다. 그러면 포착한 스펙트럼을 분할하여 좀더 집중적인 프로세싱 수행이 가능하다. 튜닝이 가능한 NCO를 사용하면 디지털화 한 스펙트럼을 DDC가 스윕하면서 전체 스펙트럼 분석이 가능할 뿐 아니라, 이 외에도 프로세싱 이득을 높이고 디지털 데이터 출력 레이트를 더 낮출 수 있는 추가적인 이점도 누릴 수 있다. 여러 개의 NCO와 DDC를 병렬로 추가하면 NCO 튜닝이 불필요하며 사용자가 사전 설정을 해서 DDC 간에 빠른 스위칭과 호핑이 가능하여 스위핑 시간을 추가적으로 더 단축할 수 있다. 또한 DDC를 통합함으로써 디지털 JESD204B 인터페이스에서 상당한 전력 절감을 할 수 있다. 이렇게 높은 속도로 실행되는 JESD SERDES는 시스템 전력 소모를 1W 이상 늘릴 수 있다. 그러므로 데이터 속도를 더 낮게 데시메이션 하는 것은 이런 관점에서 매우 유익하다. 고속 ADC가 계속해서 더 높은 샘플링 속도, 비트 깊이, 대역폭을 추구함에 따라서, DDC와 ADC를 통합하는 것이 광대역 EW 리시버 시스템 설계자들에게는 상당한 매력을 제공한다. SWaP가 낮은 프로세서를 사용해서는 ADC로부터 들어오는 방대한 양의 디지털 데이터를 처리하기가 어려울 수 있기 때문이다. DDC와 실제 사례에 대한 자세한 정보는 조나단 해리스(Jonathan Harris)의 “디지털 다운컨버터에 무슨 일이 일어나고 있는가?” 1부와 2부를 참고하기 바란다.

새로운 리시버 아키텍처 실현

헤테로다인 리시버 아키텍처는 잘 알려져 있으며 지난 수년 동안 검증되어 왔다. 지금까지 많은 마이크로파 리시버들이 듀얼 하향변환 아키텍처를 사용해서 구현되어 왔다. 이전 세대의 ADC들은 ADC 입력 주파수에 대한 동작 대역 주파수의 비율이 높아서 단일 하향변환 리시버 아키텍처로는 이미지 필터링을 하기가 현실적으로 어려웠다. 새로운 ADC들은 샘플링 속도와 아날로그 입력 대역폭이 둘 다 높아짐으로써, 고성능 광대역 단일 하향변환 아키텍처가 현실적으로 가능하고 구현하기도 쉬워졌다.

그림 1은 단일 하향변환 리시버 아키텍처를 나타낸 것이다. 잡음 수치 성능을 위해 프런트엔드에 LNA를 사용하였다. 필요하다면 LNA 앞에 리미터를 추가함으로써 프런트엔드가 견딜 수 있는 전력 능력을 높일 수 있다. 그 다음에는 동작 대역 필터를 사용해서 대역외 간섭을 감쇠시킨다. 그 다음에는 이득과 이득 제어를 필요한 만큼 추가할 수 있다. 믹서 앞에는 저역통과 필터를 사용해서 스퓨리어스 출력으로 추가되는 RF 고조파를 낮출 수 있다. 믹서는 매우 핵심적인 빌딩 블록으로서 해당 주파수 변환 대역에서 성능을 극대화하도록 선택해야 한다. 믹서 다음에 오는 또 다른 저역통과 필터는 증폭하기 전에 상단 측대역을 필터링한다. 그리고 필요에 따라서 IF 이득을 추가한다. 앨리어싱 방지 필터는 ADC 바로 앞에 위치하는 최종 소자로서, 샘플링 과정에서 대역 내로 폴딩되어 들어올 수 있는 주파수를 제거한다. 그 다음은 ADC이다. ADC는 이 체인 상에서 맨 뒤에 있으나, 설계를 할 때는 ADC를 가장 먼저 선택하고 ADC를 중심으로 리시버의 나머지 부분을 설계하는 것이 일반적이다.

그림 1: 단일 하향변환 리시버 아키텍처의 예

다음은 주파수 플랜을 선택할 때 고려사항이다. 주파수 플랜이란, 구할 수 있는 소자들로 설계를 구현할 때, 적정한 필터 제품을 가지고 스퓨리어스 발생을 최소화 할 수 있는 주파수 변환 방법을 선택하는 것을 말한다. RF 엔지니어들이 처음에 이 결정을 내려야 할 때, 다양한 선택지가 있고 적절한 주파수 플랜을 달성하기 위해서는 여러 번의 반복이 필요할 수 있기 때문에 결정하기가 쉽지는 않다. 다행히도, 향상된 최신 CAD 툴과 다양한 소자 제품들을 활용할 수 있게 되면서 이러한 주파수 플랜 작업이 많이 수월해졌다.

일반적으로 스퓨리어스 관점에서 보면, 2차 또는 3차 나이퀴스트 영역의 높은 IF 주파수가 선호된다. 하나의 예로서, 10GHz 동작 대역을 3GHz ADC의 1차 나이퀴스트 영역으로 변환하는 주파수 플랜의 이점과, 2차 나이퀴스트 영역에서 동작하는 주파수 플랜의 이점을 살펴보자.

그림 2는 10GHz에서 1GHz 동작 대역을 3GSPS ADC의 1차 나이퀴스트 영역으로 변환하는 것을 보여준다. 두 가지 문제를 알 수 있다. 첫째, RF 이미지 주파수가 동작 대역과 간격이 아주 가깝기 때문에 이미지 억제를 위해서 매우 까다로운 필터 설계가 필요하다. 둘째, IF 증폭 스테이지에서 발생하는 IF가 대역내에 들어오기 때문에 앨리어싱 방지 필터를 사용해서 필터링하는 것이 불가능하다.

그림 2: 문제가 있는 주파수 플랜. IF 고조파가 IF 대역 내로 들어오므로 이미지 필터링이 어렵다.

이와 달리, 그림 3은 동일한 RF 동작 대역을 2차 나이퀴스트 영역으로 샘플링하는 것을 보여준다. IF 주파수가 더 높기 때문에 이미지 주파수가 동작 대역으로부터 훨씬 멀리 떨어진다. 따라서 RF 이미지 필터를 구현하기가 훨씬 쉽다. 또 IF 증폭기에서 발생하는 어떤 고조파이든 앨리어싱 방지 필터를 사용해서 필터링할 수 있으며, 유일하게 발생하는 IF 고조파는 ADC 자체 내에서 발생하는 것뿐이다.

그림 3: 개선된 주파수 플랜. IF 고조파가 IF 대역 바깥에 있다. 따라서 이미지 필터링이 가능하다.

키사이트 제네시스(Keysight Genesys) 툴의 스퍼 분석을 통해서도 같은 결과가 나온다는 것을 알 수 있다. 그림 4는 WhatIF 주파수 플랜 툴을 사용한 결과이다. 10GHz 동작 주파수 대역, 1GHz 순간 대역폭, 하이사이드 LO 선택, 5차 스퓨리어스 탐색으로 설정되었다. 스퓨리어스가 발생하지 않는 영역은 녹색으로 표시되었다. 이 경우에서는 3GSPS ADC의 2차 나이퀴스트 영역에 해당된다.

그림 4: 키사이트 제네시스 WhatIF 주파수 플랜 툴을 사용한 스퍼 분석

새로운 솔루션

주파수 플랜 분석을 한 다음에는 믹서와 ADC를 해당 동작 조건으로 평가해서 스퓨리어스와 잡음 성능을 확인해야 한다.

LTC5552와 LTC5553은 최근에 출시된 고성능 3GHz~20GHz 믹서 제품이다. 그림 5는 이들 제품의 주요 특징을 보여준다. 이들 제품은 동급 최고 성능의 고 선형성 광대역 믹서 제품으로서, 광대역 리시버 아키텍처에 곧바로 사용하기에 적합하다. 두 제품의 차이점은, LTC5552는 차동 IF 출력이고, LTC5553은 모든 포트가 싱글 엔디드(singled ended)라는 것이다. 차동 IF 출력이면 전체적인 IF 사슬이 차동을 유지할 수 있으므로, ADC 입력에 통상적으로 추가되는 밸런(balun)을 제거할 수 있다. 완전 차동 IF 섹션을 실제 구현할 수 있으므로 차동 IF 증폭기를 즉시 사용할 수 있으며, 이를 위한 설계 수정 사항은 IF 신호 체인으로 차동 필터를 도입하는 것뿐이다.

그림 5: 광대역, 고성능, 고 선형성 믹서

그림 6: AD9208. 28nm를 적용한 3GSPS, 고성능, 넓은 입력 대역폭의 ADC

AD9208은 28nm를 적용한 14bit 3GSPS 듀얼 ADC 제품이다. 높은 입력 대역폭과 샘플링 분해능을 제공하며, 디지털 기능으로 4개의 DDC와 NCO를 통합하고 있어 다양한 EW 리시버 시스템 및 애플리케이션에 적합하다. 또한 아날로그 입력 대역폭이 9GHz로 높아 곧바로 2차 및 3차 나이퀴스트 주파수로 샘플링 할 수 있다. 깨끗하고 지터가 낮은 레퍼런스 클록을 사용하면 4차 나이퀴스트 샘플링도 가능하다. 그러면 높은 입력 주파수에서도 SNR 저하를 최소화할 수 있다.

RF 리시버 설계자에게 항상 문제가 되는 것은, 입력 주파수가 높아지면 ADC의 모든 중요한 특성들이 저하된다는 것이다. 이것은 잡음과 스퓨리어스가 둘 다 없는 동적 범위도 마찬가지다. 실리콘의 한계 외에도, GHz 컨버터로 입력 대역폭을 유지하기 위해서는 실리콘에서부터 패키지 라미네이트에 이르기까지, 또한 패키지에서부터 PWB에 이르기까지 신중한 설계가 요구된다.

그림 7: 아날로그 성능. SNR, SFDR, 신호 전력이 모두 입력 주파수에 따라 저하되는 것을 알 수 있다.

높은 IF 샘플링을 필요로 하는 설계는 선택한 ADC가 입력 주파수에 따라서 특성이 심각하게 저하되지 않는지 확인해야 한다. 또한 PWB 설계로 구현할 때에는 신중한 RF 레이아웃이 필요하다.

잘 설계된 RF I/O 구조에서는 입력 주파수에 따른 성능저하가 급격하지 않다. 하지만, 설계가 잘못되면 특정 입력 주파수 지점에서 성능이 갑자기 뚝 떨어질 수 있다. 그림 7은 이것을 보여준다. 애플리케이션에 사용하기 위한 컨버터를 선택하기 위해서는 실제 설계에 앞서서 충분한 시간을 들여서 성능을 잘 확인해야 한다. GHz 대의 주파수로 동작하는 RF 샘플링 ADC는 더욱 그렇다. 특정 애플리케이션에 사용하기 위한 ADC를 선택하기 앞서서 주파수에 따른 성능 특성을 잘 파악할 필요가 있다.

맺음말

이 글에서는 광대역 애플리케이션과 리시버 설계 고려사항을 살펴보았다. EW 애플리케이션은 특히나 요구가 까다롭다. 넓은 동작 대역과 가능한 높은 순간 대역폭을 지원하는 리시버를 요구하기 때문이다. 단일 하향변환 리시버 아키텍처로 높은 차수의 ADC 나이퀴스트 영역으로 동작하면 스퓨리어스 성능을 향상시킬 수 있다. 이를 위해서는 ADC의 입력 대역폭과 믹싱 스테이지의 성능 파라미터가 어려운 과제이다. 다행히 넓은 입력 주파수 범위를 지원하는 고속 28nm ADC와 광대역 고 선형성 믹서 제품들이 출시됨으로써 차세대 리시버 설계의 토대가 마련됐다.

저자 소개

데이빗 브라운(David Brown)은 아나로그디바이스(Analog Devices, 노스캐롤라이나주 그린스버로 소재)의 RF 시스템 애플리케이션 엔지니어이다. 2015년에 ADI에 입사했으며, 항공우주 및 방위산업 애플리케이션을 담당하고 있다. 2014년에 노스캐롤라이나 주립대학에서 전기공학 학사학위를 취득했다. david.brown@analog.com

피터 델로스(Peter Delos)는 아나로그디바이스(Analog Devices, 노스캐롤라이나주 그린스버로 소재)의 항공우주 및 방위산업 그룹 기술 책임자이다. 1990년에 버지니아 공대에서 전기공학 학사학위를, 2004년에 뉴저지 공대에서 전기공학 석사학위를 취득했다. 25년 넘게 이 분야에 종사해 오면서 아키텍처, PWB, IC 차원에서 첨단 RF/아날로그 시스템 설계를 주로 해왔다. 현재 위상 어레이 애플리케이션용 고성능 리시버, 파형 발생기, 합성기 설계 소형화에 매진하고 있다. peter.delos@analog.com

제품스펙