기술기고문

회로도에서 삼각형 기호가 나타내는 소자들

글: 해리 홀트(Harry Holt) 스태프 애플리케이션 엔지니어, 마이크 스크로치(Mike Skroch) 애플리케이션 엔지니어 / 아나로그디바이스(Analog Devices, Inc.)

회로도 기호는 설계를 이해하는 데 도움이 될까, 아니면 방해가 될까?

기호가 중요하긴 하지만, 하나의 기호가 여러 가지 의미를 나타낸다면 어떻게 될까?

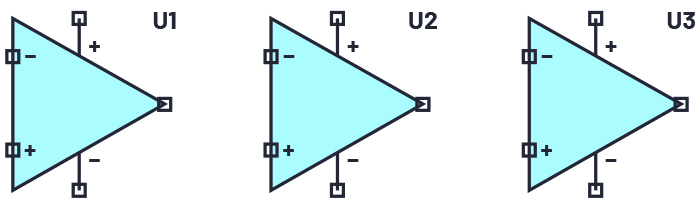

이는 앞으로 우리가 보게 될 문제들을 야기한다. 아날로그 분야에서 삼각형 기호는 연산 증폭기일 수도 있고, 비교기일 수도 있고, 계측 증폭기일 수도 있다. 이것들을 기능 구분 없이 사용할 수도 있으나, 그러면 시스템 성능을 극대화하기 어렵다. 이 글에서는 이 기호들이 어떻게 다르고, 어떻게 설계해야 할지 알아본다.

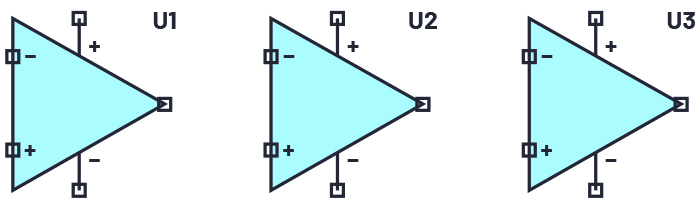

그림 1의 삼각형들 중에서 어떤 것이 연산 증폭기이고, 어떤 것이 비교기이며, 어떤 것이 계측 증폭기일까? 정답은,

‘모두 다 같다’이다.

그림 1: 연산 증폭기, 계측 증폭기, 비교기

그렇다면 차이는 무엇이고, 왜 그 차이를 이해해야 할까? 표 1을 보면, 몇몇 특성들이 크게 차이가 난다는 것을 알 수 있다. 하지만 이 차이들은 회로와 시스템 차원에서 어떤 의미를 나타낼까?

표 1: 연산 증폭기, 비교기, 계측 증폭기 비교

이제부터 이러한 내용에 대해 조금 더 자세히 살펴보기로 한다.

피드백

연산 증폭기는 이득이 엄청나게 높다. 공학 수업 시간에 배울 때에는, 두 입력 간에 차가 0인 것을 가지고 분석을 시작한다. 하지만 실제 현실에서는 그렇게 되지 않는다. 만약에 개방 루프 이득이 1백만이면, 출력에서 5V를 얻기 위해서 입력이 5mV여야 한다. 현실적으로 사용할 수 있는 회로가 되려면, 피드백을 적용해야 한다. 따라서 출력이 매우 높으면 입력으로 제어 신호를 되먹임해서 원래의 자극을 상쇄한다. 예를 들어서 네거티브 피드백을 들 수 있다. 비교기로 사용할 때는 피드백을 사용하지 않으므로 출력이 어느 한쪽 레일로 쏠릴 것이다. 포지티브 피드백을 사용하면 같은 방향으로 더 심하게 쏠릴 것이다. 그러므로 연산 증폭기는 네거티브 피드백을 필요로 한다. 실제로 어떤 연산 증폭기는 피드백을 적용하지 않고 비교기로서 사용하면 전원 전류가 데이터 시트에 표기된 최대값보다 5배에서 무려 10배까지 더 높아질 수도 있다.

비교기는 포지티브 피드백을 필요로 한다. 피드백을 사용하지 않으면, 비교기의 한쪽 입력이 서서히 다른 쪽 입력을 지나고 출력이 변화한다. 시스템에서 접지 바운스 같은 잡음이 있으면 출력이 역전될 수 있다. 이것은 제어 시스템에서 결코 바람직하지 않은 것이다. 그러다 다시 반대 방향으로 변화하기 시작한다. 그럼으로써 발진 동작을 나타낸다. 이것을 “채터(chatter)”라고 한다(MT-083의 그림 5 참조). 레자 모기미(Reza Moghimi)의 “히스터리시스를 사용한 비교기 불안정성 회복(Curing Comparator Instability with Hysteresis)”이라고 하는 글에 보면 히스터리시스라고도 하는 포지티브 피드백의 장점에 대해서 잘 설명되어 있다.

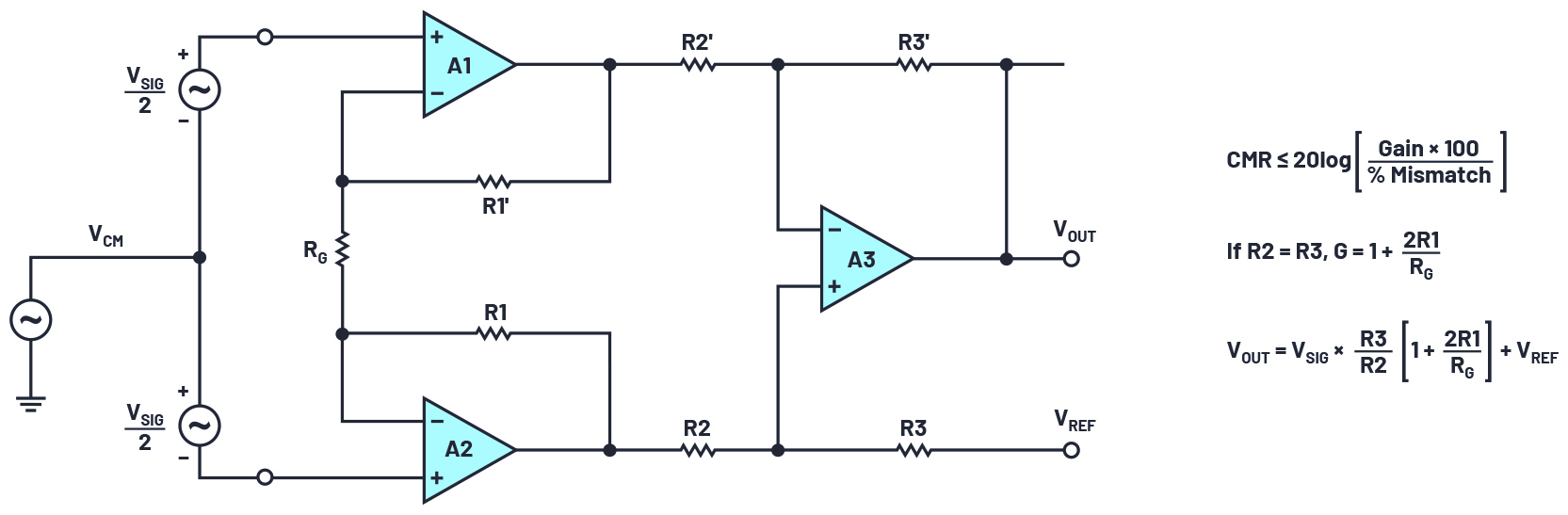

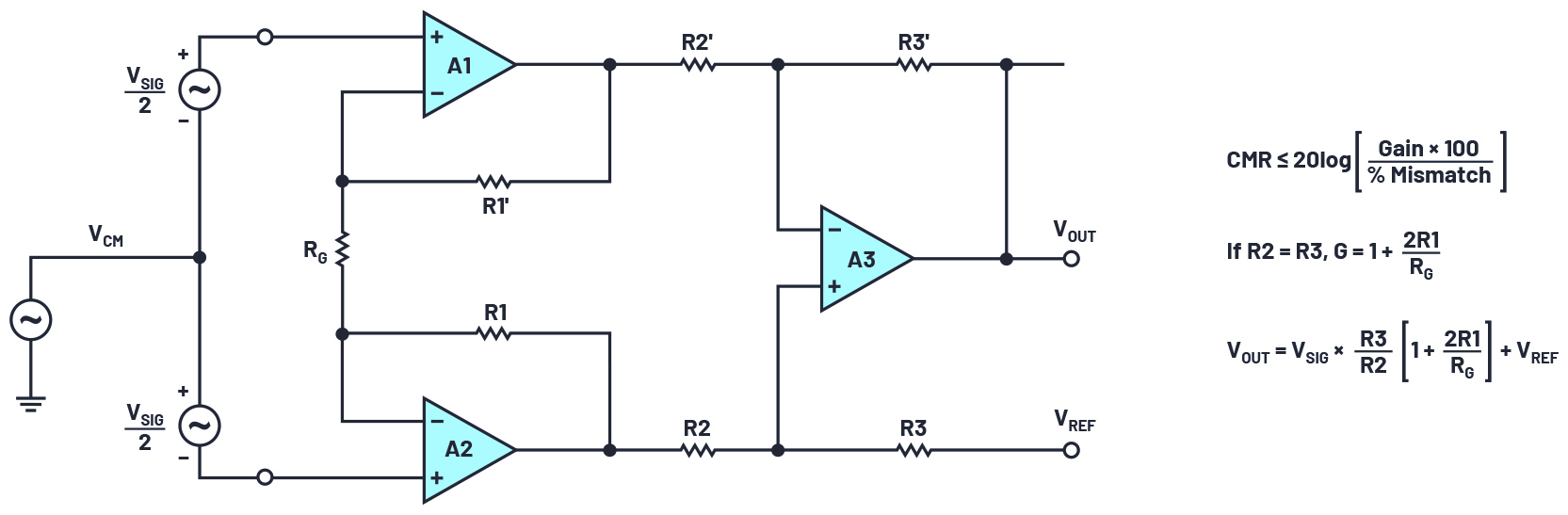

그림 2: 3개의 연산 증폭기로 이루어진 전형적인 계측 증폭기

계측 증폭기는 내부에 이미 피드백을 포함하고 있으므로, 피드백을 추가한다면 부정확한 이득만 발생시킬 뿐이다. 그림 2는 연산 증폭기를 사용해서 구현된 통상적인 계측 증폭기를 보여준다.

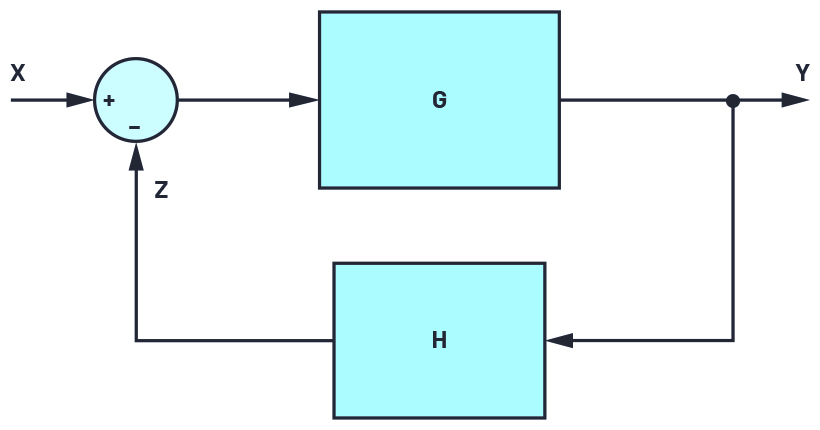

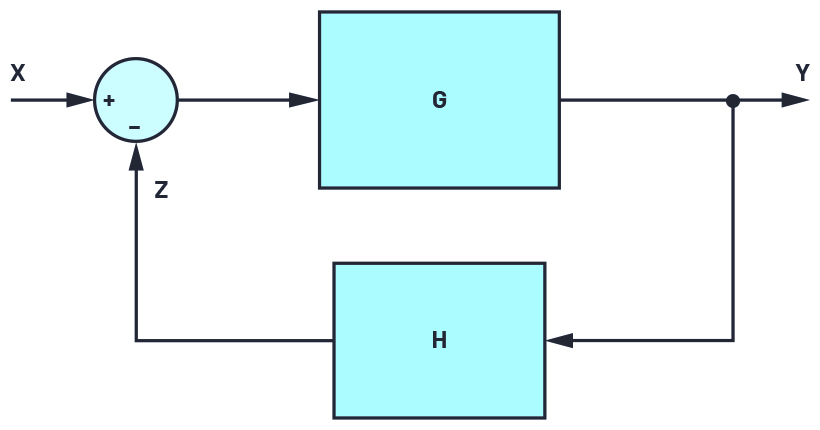

여기서 한 가지 특징은, 각각의 연산 증폭기마다 피드백을 사용한다는 것이다. 표준 네거티브 피드백 다이어그램을 이용해 살펴보자. 그림 3에서 계측 증폭기는 G이고, 원하는 이득은 10이고, 피드백 계수는 0.1이라고 하자. 그리고 계측 증폭기 고정 이득을 100으로 선택해 보겠다. 그러면 공식 1을 사용해서 실제 폐쇄 루프 이득은 9.09로서, 오차는 거의 10%이다. 그러므로 계측 증폭기 삼각형을 연산 증폭기로서 사용하고, 여기에 피드백을 사용하는 것은 타당하지 않다.

그림 3: 전형적인 피드백 회로

요약해 보면, 연산 증폭기는 네거티브 피드백이 필요하고, 비교기는 포지티브 피드백이 필요하며, 계측 증폭기는 피드백이 필요 없다.

개방 루프 및 폐쇄 루프 이득

연산 증폭기는 공식 1에서 보는 것처럼, 개방 루프 이득(AVOL)이 높을수록 폐쇄 루프 이득이 더 정확하다. 대부분의 연산 증폭기는 개방 루프 이득이 10만 ~ 1,000만에 이르지만, 구식의 일부 고속 연산 증폭기는 3000 정도로 낮은 것도 있다. 앞서도 언급했듯이, 개방 루프 이득이 높을수록 폐쇄 루프 이득 오차가 낮아진다.

비교기는 출력에서의 로직 스윙이 3V이고 1mV 임계를 원한다면 최소 이득이 3000은 되어야 한다. 이득이 높으면 불확실성을 낮출 수 있다. 그렇다고 이득이 너무 높으면 수 마이크로볼트(µV)의 잡음만으로도 비교기를 트리거 할 수 있다.

계측 증폭기는 개방 루프 이득 개념이 적용되지 않는다.

입력 커패시터

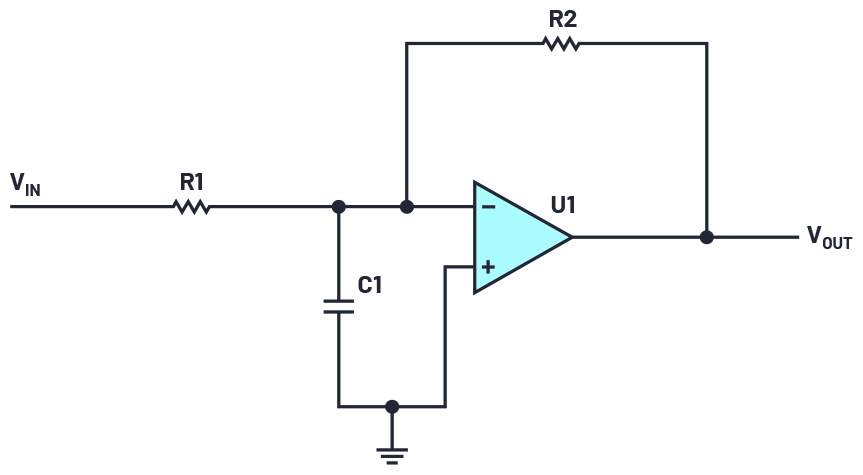

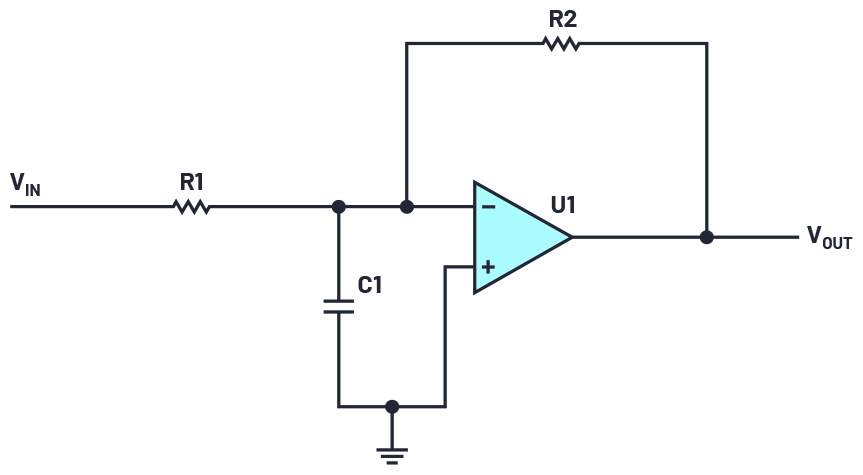

커패시터는 대역폭을 제한하기 위해 회로에 추가되곤 한다. 그림 4는 언뜻 보면 R1과 C1이 저역통과 필터(LPF)를 형성하는 것으로 보인다. 이것은 좋은 방법이 아니고 발진을 일으킬 수 있다. 반전 증폭기(inverting amplifier)의 피드백 계수는 R2/R1인데, 그림 4에서는 피드백 계수가 R2/(R1 + Xc)이다. 주파수가 높아질수록 피드백 계수는 증가한다. 그러므로 잡음 이득은 +20dB/디케이드로 증가하고, 연산 증폭기 개방 루프 이득은 -20dB/디케이드로 감소한다. 이들은 40dB 지점에서 교차하는데, 이로써 제어 시스템 이론에 따라서 발진이 일어날 수밖에 없다. 이 회로로 대역폭을 제한하는 방법은 R2로 커패시터를 추가하는 것이다.

그림 4: 연산 증폭기 대역폭 제한 방법

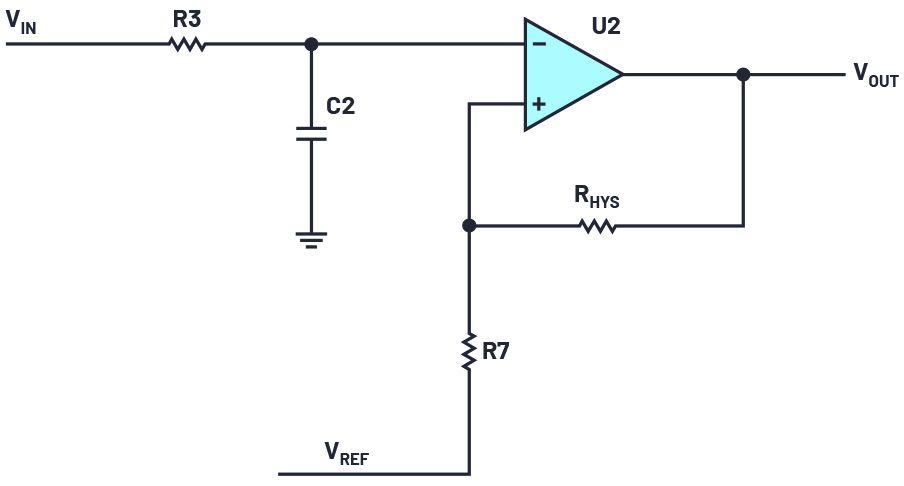

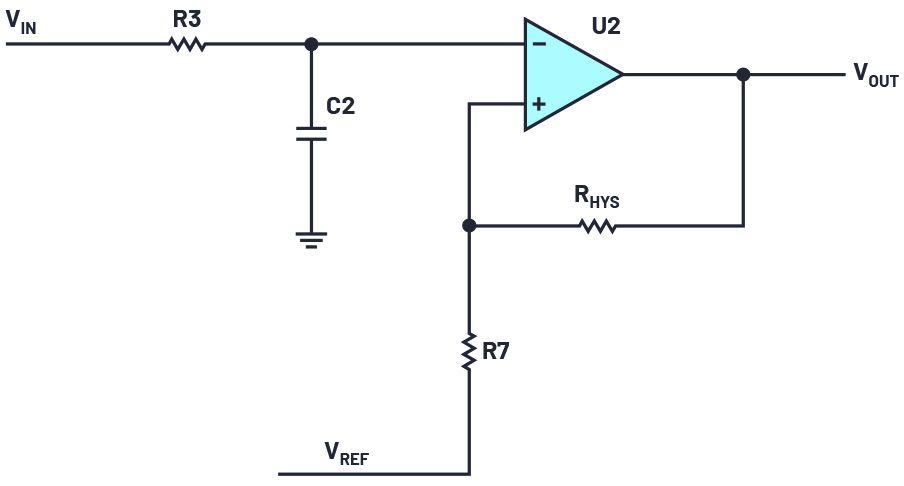

비교기는 네거티브 피드백을 사용하지 않으므로, 그림 5에서 비교기 앞쪽에 간단한 R과 C를 사용해서 저역통과 필터를 형성하는 것이 좋은 방법이다. RHYS가 R7보다 훨씬 커야 하며, 이 둘을 출력 스윙으로 나눠서 소량의 포지티브 피드백(히스터리시스)을 제공할 수 있다. LTC6752나 ADCMP391처럼 비교기가 내부 히스터리시스를 포함한 경우에는 R7과 RHYS를 사용하지 않는다.

그림 5: LPF와 히스터리시스를 지원하는 비교기

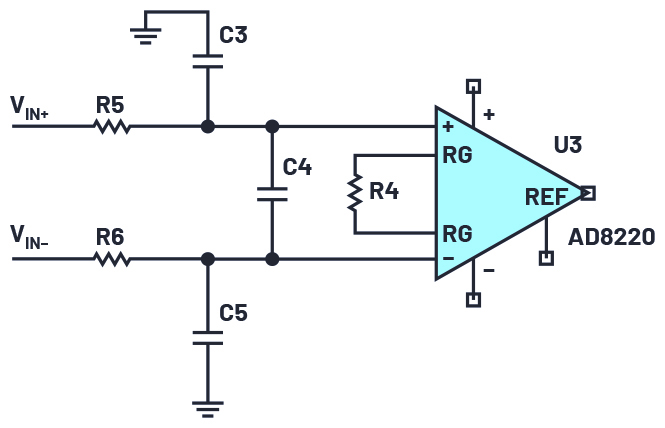

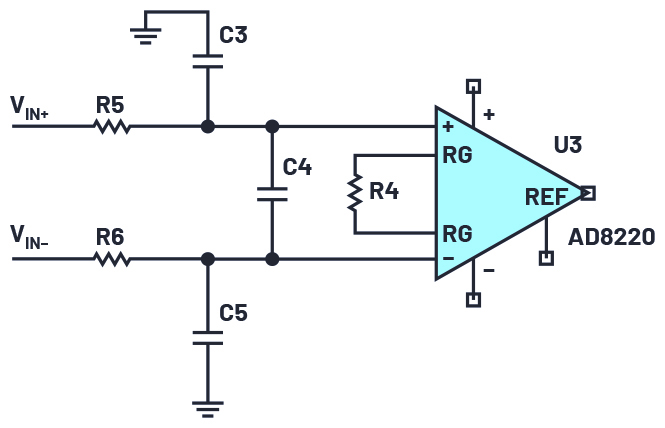

계측 증폭기는 그림 6의 C4처럼 입력에 커패시터를 사용하는 것이 바람직하다. 아나로그디바이스(ADI)의 “계측 증폭기 가이드” 제5장에서는 계측 증폭기를 사용할 때 하면 좋은 것들을 설명하고 있다. 2개의 저항과 3개의 커패시터를 추가하기 위해서 PCB에 적절한 트레이스와 패드를 사용해서 레이아웃을 할 때, 먼저 0W 저항을 사용하고 커패시터는 사용하지 않고 시스템 성능을 측정한다. 그런 다음에 5개 부품의 값을 조절해서 공통 모드 롤오프와 정상 모드 롤오프를 개별적으로 설정할 수 있다(더 자세한 내용은 “계측 증폭기 가이드” 참조).

그림 6: 계측 증폭기 앞쪽에 RFI 필터 사용

출력

연산 증폭기나 계측 증폭기는 출력이 한 레일에서 다른 레일로 스윙할 수 있다. 출력 스테이지에 공통 이미터 구성을 사용하느냐 공통 소스 구성을 사용하느냐에 따라서 출력이 한쪽 레일의 25mV ~ 200mV 이내가 될 수 있다. 그러므로 레일-투-레일 출력이라고 할 수 있다. 만약에 연산 증폭기를 +15V와 -15V로 구동하면 디지털 회로로 인터페이스하기가 불편하다. 기존에 시도되었던 나쁜 방법 중의 하나는 디지털 입력이 손상되지 않도록 보호하기 위해서 출력에 다이오드 클램프를 사용하는 것이다. 그러면 연산 증폭기 전류가 엄청나게 높아져서 연산 증폭기가 손상될 수 있다. 연산 증폭기를 디지털 로직으로 인터페이스하기 위한 좀더 나은 방법은 비교기를 사용하는 것이다.

비교기는 CMOS 토템폴(totem-pole) 출력이나 NPN 또는 NMOS 개방 컬렉터 또는 개방 드레인 출력이 가능하다. 개방 컬렉터 또는 개방 드레인 출력은 풀업 저항을 필요로 하고 상승 및 하강 시간이 불균등하다는 단점이 있지만, 장점은 비교기를 가령 5V로 동작하면서 3.3V 같은 다른 전압으로 동작하는 로직으로 인터페이스할 수 있다는 것이다.

주요 사양

연산 증폭기는 폐쇄 루프 오차를 낮게 유지하기 위해서 이득 대역폭이 최대 신호 주파수보다 높아야 한다. 공식 1을 보면, 원칙적으로 이득 대역폭이 최대 신호 주파수의 10 ~ 100배가 되어야 한다는 것을 알 수 있다. 공식 1에서 AVOL은 주파수에 따른 함수로서, 폐쇄 루프 정확도에 영향을 미친다. 위상 마진 역시 중요하며, 이 사양은 용량성 부하에 따라서 달라진다. 그러므로 사양표에서 테스트 조건을 명확히 해야 한다. DC 정확도를 위해서는 오프셋 전압이 낮아야 한다. 트리밍 된 바이폴라 연산 증폭기로는 25mV ~ 100mV이면 좋은 것이고, FET 입력 연산 증폭기로는 200mV ~ 500mV이면 좋은 것이다. 오토 제로/쵸퍼/제로 드리프트 연산 증폭기는 거의 언제나 전체 온도에 걸쳐서 최대 20mV 미만이다. 이와 관련해서 OP27, AD8610, ADA4522 같은 대표적인 연산 증폭기 데이터 시트를 참고할 수 있다.

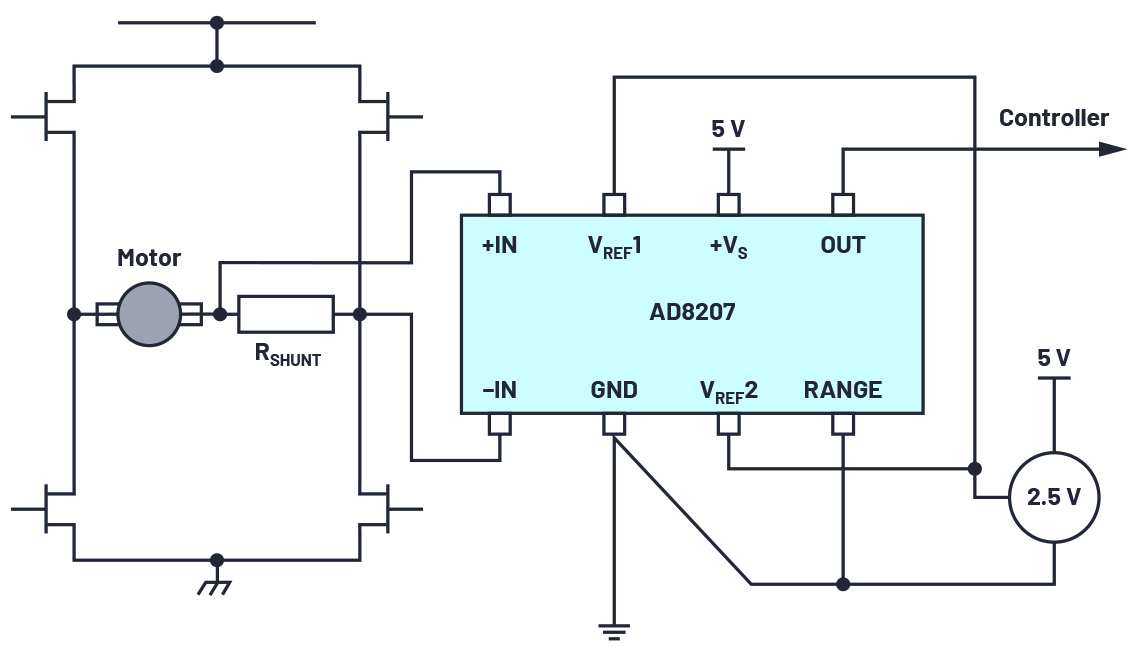

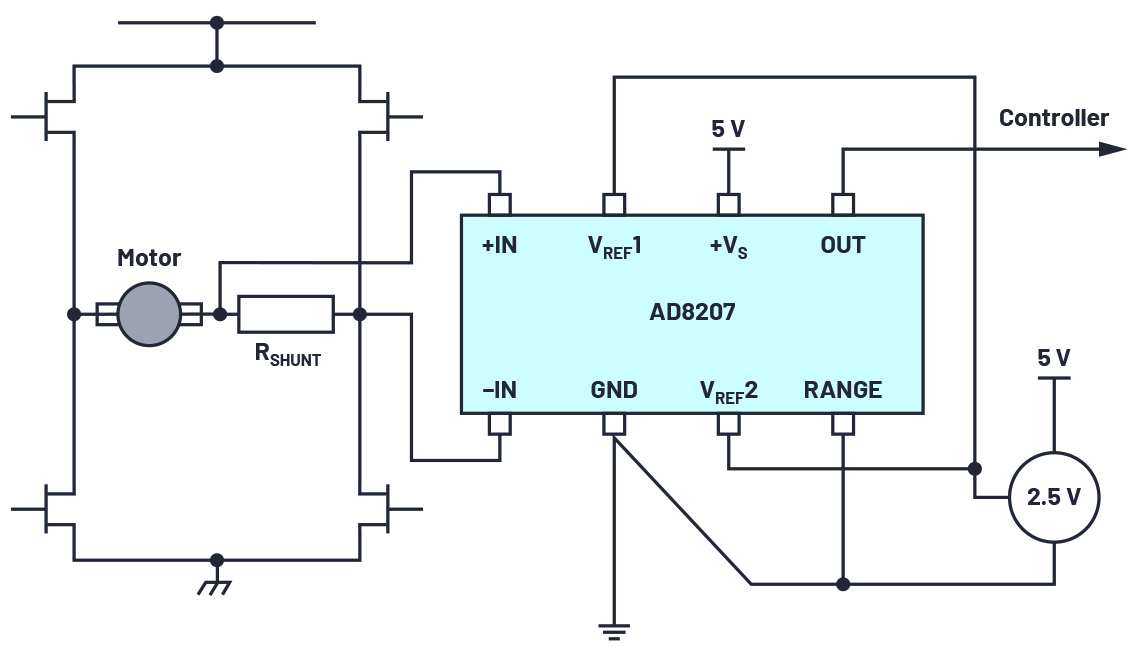

그림 7: 높은 공통 모드 스윙으로 양방향 전류 검출

전파 지연은 비교기에서 중요한 사양이다. 연산 증폭기가 과구동되었을 때 느려지는 것과 달리, 비교기는 과구동되었을 때 빨라진다. 사양서에서는 종종 전파 지연을 예컨대 5mV의 약간의 과구동일 때에 대해서 표기하는데, 과구동이 50mV나 심지어 100mV처럼 더 크다면 지연 특성이 달라질 것이다.

계측 증폭기에서 가장 중요한 사양은 공통 모드 제거비(CMRR)이다. 대개 설계자들은 높은 공통 모드 전압 상에서 매우 낮은 차동 신호를 뽑아내고자 한다. 다른 많은 사양들처럼, 이 사양 역시 주파수에 따라서 달라지며, DC CMRR 또는 매우 낮은 주파수에서의 CMRR을 표기하기도 한다. 통상적으로 주파수에 따른 CMRR 그래프가 제공된다. 예를 들어서 그림 7에서 보는 것과 같은 H-브리지 모터 드라이브로 전류를 검출하고자 할 때 이 사양이 중요하다.

이 애플리케이션은 계측 증폭기와 관련하여 가장 까다로운 애플리케이션 중의 하나일 것이다. 공통 모드 전압이 한 레일에 가까웠다가 다른 레일에 가까워지고 전류가 빠르게 역전되기 때문이다. 이득 대역폭과 슬루율 역시 중요하다.

프로그래밍

여기서 말하는 프로그래밍은 코드를 작성하는 것이 아니라 부품을 시스템 요건에 맞게 구성하는 것을 뜻한다. (다만 일부 계측 증폭기는 SPI 포트와 레지스터를 통해서 전통적인 의미의 소프트웨어 프로그래밍이 가능하기도 하다.)

연산 증폭기는 네거티브 피드백을 사용해서 구성할 수 있다. 이것은 전적으로 저항성 소자일 수 있으나, 보통은 대역폭을 제한하기 위해서 저항과 함께 커패시터를 병렬로 사용한다. 이렇게 하면 신호대 잡음비 측면에서 도움이 된다. 전체적인 범위의 일부만 사용하면서도 전체 범위에 걸쳐서 잡음을 적분하기 때문이다. 또한 커패시터를 사용해서 적분기나 미분기를 구현할 수 있다.

비교기는 언제나 약간의 포지티브 피드백을 사용해야 한다. 그럼으로써 일단 입력이 출력을 움직이게 하면 출력이 이 움직임을 강화한다(그림 4와 그림 5 참조). MT-083에서는 이와 관련된 그림과 계산들을 볼 수 있다. 일부 비교기는 내부 히스터리시스를 포함하며, 필요하면 더 추가할 수도 있다. 내부 히스터리시스를 포함하는 비교기는 저항을 추가해서 이 양을 조절할 수 있는 핀을 제공한다.

연산 증폭기를 비교기로 사용하는 것은 가능은 하지만 그다지 바람직하지는 않으며, 많은 것들을 고려해야 한다. 설계자가 유능한 아날로그 설계 엔지니어야 할 것이다. MT-083을 비롯한 많은 자료들에서 이와 관련된 내용들을 볼 수 있다. 굳이 모험을 즐기고자 한다면 참고문헌들을 참고할 수 있을 것이다.

비교기는 거의 언제나 저항을 사용해서 프로그램 한다. 높은 값의 저항을 사용해서 약간의 포지티브 피드백을 제공할 수 있으며, AC 피드백을 위해 커패시터를 사용함으로써 DC 히스터리시스를 추가하는 것을 피할 수 있다. 어떤 비교기는 내부 히스터리시스를 포함하며, 이 역시 약간의 포지티브 피드백을 추가해서 높일 수 있다.

그 밖의 고려사항

연산 증폭기를 비교기로 사용하려면 까다로운 점들이 있다. 꽤 많은 저잡음 바이폴라 연산 증폭기가 입력들 사이에 역평행 다이오드를 사용한다. 대부분 비교기의 입력 공통 모드 범위가 총 범위의 80% 혹은 그 이상에 이른다. 하지만 어떤 저잡음 바이폴라 연산 증폭기들은 입력들 사이에 1 ~ 2개의 다이오드를 직렬로 사용한다. 이렇게 하면 입력 스테이지가 이미터 베이스 접합부로 제너 효과(Zenering)를 일으키는 것을 방지할 수 있다. 만약에 이것이 발생한다면 시간이 지날수록 잡음 성능이 저하될 것이다.

그러므로 3.3V 시스템에서 파워굿(power-good) 지시를 위해서 5V 연산 증폭기를 3V 임계 수준의 비교기로 사용하면 한쪽 입력은 3V가 되고 다른 쪽 입력은 0V가 되어서 문제가 될 수 있다. 이들 다이오드가 연산 증폭기 입력으로 허용되는 최대 차동 전압을 제한하기 때문이다.

맺음말

많은 애플리케이션에서 연산 증폭기는 요구되는 DC 정확도, AC 정확도, 입력 오프셋 전압, 이득 대역폭, 전원 전압에 따라서 최적의 제품을 선택할 수 있다. 2020년에 ADI는 700종 이상의 연산 증폭기 제품을 제공했다. 비교기를 선택할 때 중요하게 고려해야 할 파라미터는 전파 지연과 전원 전압이다. 비교기 선택은 비교적 쉬운데, 122개 제품 중에서 선택할 수 있다. 계측 증폭기를 선택할 때 중요한 파라미터는 주파수에 따른 CMRR이다. DC 부근에서는 오프셋 전압과 이득 정확도 또한 중요하다. 계측 증폭기는 좀더 특수하므로, 선택할 수 있는 제품이 63개로 줄어든다.

용도에 따라서 적합한 제품을 선택함으로써 문제를 줄이고 수명이 오래가는 설계를 설계할 수 있다.

저자 소개

해리 홀트(Harry Holt)는 아나로그디바이스(캘리포니아주 산호세)에서 14년 간 재직했으며, 애플리케이션 그룹의 스태프 애플리케이션 엔지니어였다. ADI 입사 전에는 27년 간 내셔널 세미컨덕터(National Semiconductor)에서 데이터 컨버터, 연산 증폭기, 레퍼런스, 오디오 코덱, FPGA를 비롯한 다양한 제품들을 취급했다. 산호세 주립대학에서 BSEE를 취득했으며, Tau Beta Pi 협회의 종신 회원이자 IEEE의 종신 시니어 회원이다.

마이크 스크로치(Mike Skroch)는 미국 중부 및 그레이트 레이크 지역 FAE 팀의 애플리케이션 엔지니어이다. 2014년에 리니어 테크놀로지(Linear Technology)에 입사했으며, 2017년에 리니어가 ADI에 인수되면서 ADI에서 근무해 왔다. 반도체 업계에 몸 담기 전에는 16년 간 텔레콤 업계에서 제조, 테스트 개발, 반품 및 수리, R&D와 관련한 여러 직책을 거쳤다. 문의: mike.skroch@analog.com

회로도 기호는 설계를 이해하는 데 도움이 될까, 아니면 방해가 될까?

기호가 중요하긴 하지만, 하나의 기호가 여러 가지 의미를 나타낸다면 어떻게 될까?

이는 앞으로 우리가 보게 될 문제들을 야기한다. 아날로그 분야에서 삼각형 기호는 연산 증폭기일 수도 있고, 비교기일 수도 있고, 계측 증폭기일 수도 있다. 이것들을 기능 구분 없이 사용할 수도 있으나, 그러면 시스템 성능을 극대화하기 어렵다. 이 글에서는 이 기호들이 어떻게 다르고, 어떻게 설계해야 할지 알아본다.

그림 1의 삼각형들 중에서 어떤 것이 연산 증폭기이고, 어떤 것이 비교기이며, 어떤 것이 계측 증폭기일까? 정답은,

‘모두 다 같다’이다.

그림 1: 연산 증폭기, 계측 증폭기, 비교기

그렇다면 차이는 무엇이고, 왜 그 차이를 이해해야 할까? 표 1을 보면, 몇몇 특성들이 크게 차이가 난다는 것을 알 수 있다. 하지만 이 차이들은 회로와 시스템 차원에서 어떤 의미를 나타낼까?

표 1: 연산 증폭기, 비교기, 계측 증폭기 비교

| 연산 증폭기 | 비교기 | 계측 증폭기 | |

| 피드백 | 네거티브 | 없음/포지티브 | 내장 |

| 개루프 이득 | 5k ~ 10M | 3k ~ 50k | 고정 0.2 ~ 10k |

| 폐루프 이득 | 통상 10,000 이하 | 고정 0.2 ~ 10k | |

| 입력 커패시터 갯수 | 전혀 없음 | 있을 수도 있음 | 많음 |

| 출력 | 아날로그/리니어 | 디지털 | 아날로그/리니어 |

| 주요 사양 | VOS, GBW/PM | 전파 지연 | CMRR |

| 프로그래밍 | R 또는 C | 없음 | R, SPI, 점퍼 |

이제부터 이러한 내용에 대해 조금 더 자세히 살펴보기로 한다.

피드백

연산 증폭기는 이득이 엄청나게 높다. 공학 수업 시간에 배울 때에는, 두 입력 간에 차가 0인 것을 가지고 분석을 시작한다. 하지만 실제 현실에서는 그렇게 되지 않는다. 만약에 개방 루프 이득이 1백만이면, 출력에서 5V를 얻기 위해서 입력이 5mV여야 한다. 현실적으로 사용할 수 있는 회로가 되려면, 피드백을 적용해야 한다. 따라서 출력이 매우 높으면 입력으로 제어 신호를 되먹임해서 원래의 자극을 상쇄한다. 예를 들어서 네거티브 피드백을 들 수 있다. 비교기로 사용할 때는 피드백을 사용하지 않으므로 출력이 어느 한쪽 레일로 쏠릴 것이다. 포지티브 피드백을 사용하면 같은 방향으로 더 심하게 쏠릴 것이다. 그러므로 연산 증폭기는 네거티브 피드백을 필요로 한다. 실제로 어떤 연산 증폭기는 피드백을 적용하지 않고 비교기로서 사용하면 전원 전류가 데이터 시트에 표기된 최대값보다 5배에서 무려 10배까지 더 높아질 수도 있다.

비교기는 포지티브 피드백을 필요로 한다. 피드백을 사용하지 않으면, 비교기의 한쪽 입력이 서서히 다른 쪽 입력을 지나고 출력이 변화한다. 시스템에서 접지 바운스 같은 잡음이 있으면 출력이 역전될 수 있다. 이것은 제어 시스템에서 결코 바람직하지 않은 것이다. 그러다 다시 반대 방향으로 변화하기 시작한다. 그럼으로써 발진 동작을 나타낸다. 이것을 “채터(chatter)”라고 한다(MT-083의 그림 5 참조). 레자 모기미(Reza Moghimi)의 “히스터리시스를 사용한 비교기 불안정성 회복(Curing Comparator Instability with Hysteresis)”이라고 하는 글에 보면 히스터리시스라고도 하는 포지티브 피드백의 장점에 대해서 잘 설명되어 있다.

그림 2: 3개의 연산 증폭기로 이루어진 전형적인 계측 증폭기

계측 증폭기는 내부에 이미 피드백을 포함하고 있으므로, 피드백을 추가한다면 부정확한 이득만 발생시킬 뿐이다. 그림 2는 연산 증폭기를 사용해서 구현된 통상적인 계측 증폭기를 보여준다.

여기서 한 가지 특징은, 각각의 연산 증폭기마다 피드백을 사용한다는 것이다. 표준 네거티브 피드백 다이어그램을 이용해 살펴보자. 그림 3에서 계측 증폭기는 G이고, 원하는 이득은 10이고, 피드백 계수는 0.1이라고 하자. 그리고 계측 증폭기 고정 이득을 100으로 선택해 보겠다. 그러면 공식 1을 사용해서 실제 폐쇄 루프 이득은 9.09로서, 오차는 거의 10%이다. 그러므로 계측 증폭기 삼각형을 연산 증폭기로서 사용하고, 여기에 피드백을 사용하는 것은 타당하지 않다.

그림 3: 전형적인 피드백 회로

요약해 보면, 연산 증폭기는 네거티브 피드백이 필요하고, 비교기는 포지티브 피드백이 필요하며, 계측 증폭기는 피드백이 필요 없다.

개방 루프 및 폐쇄 루프 이득

연산 증폭기는 공식 1에서 보는 것처럼, 개방 루프 이득(AVOL)이 높을수록 폐쇄 루프 이득이 더 정확하다. 대부분의 연산 증폭기는 개방 루프 이득이 10만 ~ 1,000만에 이르지만, 구식의 일부 고속 연산 증폭기는 3000 정도로 낮은 것도 있다. 앞서도 언급했듯이, 개방 루프 이득이 높을수록 폐쇄 루프 이득 오차가 낮아진다.

비교기는 출력에서의 로직 스윙이 3V이고 1mV 임계를 원한다면 최소 이득이 3000은 되어야 한다. 이득이 높으면 불확실성을 낮출 수 있다. 그렇다고 이득이 너무 높으면 수 마이크로볼트(µV)의 잡음만으로도 비교기를 트리거 할 수 있다.

계측 증폭기는 개방 루프 이득 개념이 적용되지 않는다.

입력 커패시터

커패시터는 대역폭을 제한하기 위해 회로에 추가되곤 한다. 그림 4는 언뜻 보면 R1과 C1이 저역통과 필터(LPF)를 형성하는 것으로 보인다. 이것은 좋은 방법이 아니고 발진을 일으킬 수 있다. 반전 증폭기(inverting amplifier)의 피드백 계수는 R2/R1인데, 그림 4에서는 피드백 계수가 R2/(R1 + Xc)이다. 주파수가 높아질수록 피드백 계수는 증가한다. 그러므로 잡음 이득은 +20dB/디케이드로 증가하고, 연산 증폭기 개방 루프 이득은 -20dB/디케이드로 감소한다. 이들은 40dB 지점에서 교차하는데, 이로써 제어 시스템 이론에 따라서 발진이 일어날 수밖에 없다. 이 회로로 대역폭을 제한하는 방법은 R2로 커패시터를 추가하는 것이다.

그림 4: 연산 증폭기 대역폭 제한 방법

비교기는 네거티브 피드백을 사용하지 않으므로, 그림 5에서 비교기 앞쪽에 간단한 R과 C를 사용해서 저역통과 필터를 형성하는 것이 좋은 방법이다. RHYS가 R7보다 훨씬 커야 하며, 이 둘을 출력 스윙으로 나눠서 소량의 포지티브 피드백(히스터리시스)을 제공할 수 있다. LTC6752나 ADCMP391처럼 비교기가 내부 히스터리시스를 포함한 경우에는 R7과 RHYS를 사용하지 않는다.

그림 5: LPF와 히스터리시스를 지원하는 비교기

계측 증폭기는 그림 6의 C4처럼 입력에 커패시터를 사용하는 것이 바람직하다. 아나로그디바이스(ADI)의 “계측 증폭기 가이드” 제5장에서는 계측 증폭기를 사용할 때 하면 좋은 것들을 설명하고 있다. 2개의 저항과 3개의 커패시터를 추가하기 위해서 PCB에 적절한 트레이스와 패드를 사용해서 레이아웃을 할 때, 먼저 0W 저항을 사용하고 커패시터는 사용하지 않고 시스템 성능을 측정한다. 그런 다음에 5개 부품의 값을 조절해서 공통 모드 롤오프와 정상 모드 롤오프를 개별적으로 설정할 수 있다(더 자세한 내용은 “계측 증폭기 가이드” 참조).

그림 6: 계측 증폭기 앞쪽에 RFI 필터 사용

출력

연산 증폭기나 계측 증폭기는 출력이 한 레일에서 다른 레일로 스윙할 수 있다. 출력 스테이지에 공통 이미터 구성을 사용하느냐 공통 소스 구성을 사용하느냐에 따라서 출력이 한쪽 레일의 25mV ~ 200mV 이내가 될 수 있다. 그러므로 레일-투-레일 출력이라고 할 수 있다. 만약에 연산 증폭기를 +15V와 -15V로 구동하면 디지털 회로로 인터페이스하기가 불편하다. 기존에 시도되었던 나쁜 방법 중의 하나는 디지털 입력이 손상되지 않도록 보호하기 위해서 출력에 다이오드 클램프를 사용하는 것이다. 그러면 연산 증폭기 전류가 엄청나게 높아져서 연산 증폭기가 손상될 수 있다. 연산 증폭기를 디지털 로직으로 인터페이스하기 위한 좀더 나은 방법은 비교기를 사용하는 것이다.

비교기는 CMOS 토템폴(totem-pole) 출력이나 NPN 또는 NMOS 개방 컬렉터 또는 개방 드레인 출력이 가능하다. 개방 컬렉터 또는 개방 드레인 출력은 풀업 저항을 필요로 하고 상승 및 하강 시간이 불균등하다는 단점이 있지만, 장점은 비교기를 가령 5V로 동작하면서 3.3V 같은 다른 전압으로 동작하는 로직으로 인터페이스할 수 있다는 것이다.

주요 사양

연산 증폭기는 폐쇄 루프 오차를 낮게 유지하기 위해서 이득 대역폭이 최대 신호 주파수보다 높아야 한다. 공식 1을 보면, 원칙적으로 이득 대역폭이 최대 신호 주파수의 10 ~ 100배가 되어야 한다는 것을 알 수 있다. 공식 1에서 AVOL은 주파수에 따른 함수로서, 폐쇄 루프 정확도에 영향을 미친다. 위상 마진 역시 중요하며, 이 사양은 용량성 부하에 따라서 달라진다. 그러므로 사양표에서 테스트 조건을 명확히 해야 한다. DC 정확도를 위해서는 오프셋 전압이 낮아야 한다. 트리밍 된 바이폴라 연산 증폭기로는 25mV ~ 100mV이면 좋은 것이고, FET 입력 연산 증폭기로는 200mV ~ 500mV이면 좋은 것이다. 오토 제로/쵸퍼/제로 드리프트 연산 증폭기는 거의 언제나 전체 온도에 걸쳐서 최대 20mV 미만이다. 이와 관련해서 OP27, AD8610, ADA4522 같은 대표적인 연산 증폭기 데이터 시트를 참고할 수 있다.

그림 7: 높은 공통 모드 스윙으로 양방향 전류 검출

전파 지연은 비교기에서 중요한 사양이다. 연산 증폭기가 과구동되었을 때 느려지는 것과 달리, 비교기는 과구동되었을 때 빨라진다. 사양서에서는 종종 전파 지연을 예컨대 5mV의 약간의 과구동일 때에 대해서 표기하는데, 과구동이 50mV나 심지어 100mV처럼 더 크다면 지연 특성이 달라질 것이다.

계측 증폭기에서 가장 중요한 사양은 공통 모드 제거비(CMRR)이다. 대개 설계자들은 높은 공통 모드 전압 상에서 매우 낮은 차동 신호를 뽑아내고자 한다. 다른 많은 사양들처럼, 이 사양 역시 주파수에 따라서 달라지며, DC CMRR 또는 매우 낮은 주파수에서의 CMRR을 표기하기도 한다. 통상적으로 주파수에 따른 CMRR 그래프가 제공된다. 예를 들어서 그림 7에서 보는 것과 같은 H-브리지 모터 드라이브로 전류를 검출하고자 할 때 이 사양이 중요하다.

이 애플리케이션은 계측 증폭기와 관련하여 가장 까다로운 애플리케이션 중의 하나일 것이다. 공통 모드 전압이 한 레일에 가까웠다가 다른 레일에 가까워지고 전류가 빠르게 역전되기 때문이다. 이득 대역폭과 슬루율 역시 중요하다.

프로그래밍

여기서 말하는 프로그래밍은 코드를 작성하는 것이 아니라 부품을 시스템 요건에 맞게 구성하는 것을 뜻한다. (다만 일부 계측 증폭기는 SPI 포트와 레지스터를 통해서 전통적인 의미의 소프트웨어 프로그래밍이 가능하기도 하다.)

연산 증폭기는 네거티브 피드백을 사용해서 구성할 수 있다. 이것은 전적으로 저항성 소자일 수 있으나, 보통은 대역폭을 제한하기 위해서 저항과 함께 커패시터를 병렬로 사용한다. 이렇게 하면 신호대 잡음비 측면에서 도움이 된다. 전체적인 범위의 일부만 사용하면서도 전체 범위에 걸쳐서 잡음을 적분하기 때문이다. 또한 커패시터를 사용해서 적분기나 미분기를 구현할 수 있다.

비교기는 언제나 약간의 포지티브 피드백을 사용해야 한다. 그럼으로써 일단 입력이 출력을 움직이게 하면 출력이 이 움직임을 강화한다(그림 4와 그림 5 참조). MT-083에서는 이와 관련된 그림과 계산들을 볼 수 있다. 일부 비교기는 내부 히스터리시스를 포함하며, 필요하면 더 추가할 수도 있다. 내부 히스터리시스를 포함하는 비교기는 저항을 추가해서 이 양을 조절할 수 있는 핀을 제공한다.

연산 증폭기를 비교기로 사용하는 것은 가능은 하지만 그다지 바람직하지는 않으며, 많은 것들을 고려해야 한다. 설계자가 유능한 아날로그 설계 엔지니어야 할 것이다. MT-083을 비롯한 많은 자료들에서 이와 관련된 내용들을 볼 수 있다. 굳이 모험을 즐기고자 한다면 참고문헌들을 참고할 수 있을 것이다.

비교기는 거의 언제나 저항을 사용해서 프로그램 한다. 높은 값의 저항을 사용해서 약간의 포지티브 피드백을 제공할 수 있으며, AC 피드백을 위해 커패시터를 사용함으로써 DC 히스터리시스를 추가하는 것을 피할 수 있다. 어떤 비교기는 내부 히스터리시스를 포함하며, 이 역시 약간의 포지티브 피드백을 추가해서 높일 수 있다.

그 밖의 고려사항

연산 증폭기를 비교기로 사용하려면 까다로운 점들이 있다. 꽤 많은 저잡음 바이폴라 연산 증폭기가 입력들 사이에 역평행 다이오드를 사용한다. 대부분 비교기의 입력 공통 모드 범위가 총 범위의 80% 혹은 그 이상에 이른다. 하지만 어떤 저잡음 바이폴라 연산 증폭기들은 입력들 사이에 1 ~ 2개의 다이오드를 직렬로 사용한다. 이렇게 하면 입력 스테이지가 이미터 베이스 접합부로 제너 효과(Zenering)를 일으키는 것을 방지할 수 있다. 만약에 이것이 발생한다면 시간이 지날수록 잡음 성능이 저하될 것이다.

그러므로 3.3V 시스템에서 파워굿(power-good) 지시를 위해서 5V 연산 증폭기를 3V 임계 수준의 비교기로 사용하면 한쪽 입력은 3V가 되고 다른 쪽 입력은 0V가 되어서 문제가 될 수 있다. 이들 다이오드가 연산 증폭기 입력으로 허용되는 최대 차동 전압을 제한하기 때문이다.

맺음말

많은 애플리케이션에서 연산 증폭기는 요구되는 DC 정확도, AC 정확도, 입력 오프셋 전압, 이득 대역폭, 전원 전압에 따라서 최적의 제품을 선택할 수 있다. 2020년에 ADI는 700종 이상의 연산 증폭기 제품을 제공했다. 비교기를 선택할 때 중요하게 고려해야 할 파라미터는 전파 지연과 전원 전압이다. 비교기 선택은 비교적 쉬운데, 122개 제품 중에서 선택할 수 있다. 계측 증폭기를 선택할 때 중요한 파라미터는 주파수에 따른 CMRR이다. DC 부근에서는 오프셋 전압과 이득 정확도 또한 중요하다. 계측 증폭기는 좀더 특수하므로, 선택할 수 있는 제품이 63개로 줄어든다.

용도에 따라서 적합한 제품을 선택함으로써 문제를 줄이고 수명이 오래가는 설계를 설계할 수 있다.

저자 소개

해리 홀트(Harry Holt)는 아나로그디바이스(캘리포니아주 산호세)에서 14년 간 재직했으며, 애플리케이션 그룹의 스태프 애플리케이션 엔지니어였다. ADI 입사 전에는 27년 간 내셔널 세미컨덕터(National Semiconductor)에서 데이터 컨버터, 연산 증폭기, 레퍼런스, 오디오 코덱, FPGA를 비롯한 다양한 제품들을 취급했다. 산호세 주립대학에서 BSEE를 취득했으며, Tau Beta Pi 협회의 종신 회원이자 IEEE의 종신 시니어 회원이다.

마이크 스크로치(Mike Skroch)는 미국 중부 및 그레이트 레이크 지역 FAE 팀의 애플리케이션 엔지니어이다. 2014년에 리니어 테크놀로지(Linear Technology)에 입사했으며, 2017년에 리니어가 ADI에 인수되면서 ADI에서 근무해 왔다. 반도체 업계에 몸 담기 전에는 16년 간 텔레콤 업계에서 제조, 테스트 개발, 반품 및 수리, R&D와 관련한 여러 직책을 거쳤다. 문의: mike.skroch@analog.com

제품스펙