Technical Article

제품 및 Tools

메인스트림 시스템 및 플랫폼 디자이너에게 획기적인 생산성 향상을 선사하는 비바도(Vivado) HLx 에디션

메인스트림 시스템 및 플랫폼 디자이너에게 획기적인 생산성 향상을 선사하는 비바도(Vivado) HLx 에디션

2016-02-22

비바도 디자인 수트 HLx 에디션

시스템 플랫폼의 효율적인 적용 및 구현을 위해 획기적인 생산성을 제공하는 새로운 접근법

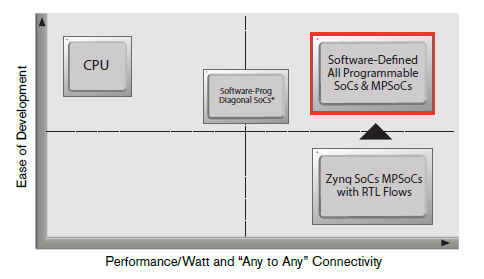

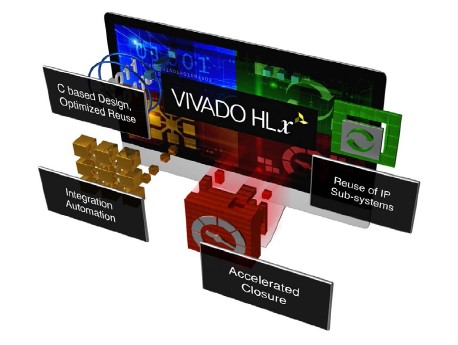

비바도 디자인 수트(Vivado® Design Suite)는 차세대 C/C++ 및 IP 기반 디자인의 생산성을 획기적으로 향상시켜주는 새로운 접근법을 제공한다. 새로운 HLx 에디션은 HL 시스템 에디션 및 HL 디자인 에디션, HL WebPACK™ 에디션을 포함하고 있다. 사용자는 새로운 UltraFast™ 하이-레벨 생산성 디자인 방법론 가이드(High-Level Productivity Design Methodology Guide)를 이용해 기존의 접근방식 대비 10배에서 15배의 생산성 향상을 실현할 수 있다.

<비바도 디자인 수트(Vivado Design Suite) HLx 에디션>

15배의 생산성 향상 실현:

• C/C++ 기반 디자인 및 재사용 가속화

• 도메인별로 특화된 라이브러리

• IP 서브시스템

• 통합 자동화

• 더 빨라진 디자인 클로저

• 빠른 플랫폼 생성 및 구축 가능

• 징크(Zynq) SoC 및 새로운 MPSoC와 더불어 ASIC급 FPGA 및 3D IC 지원

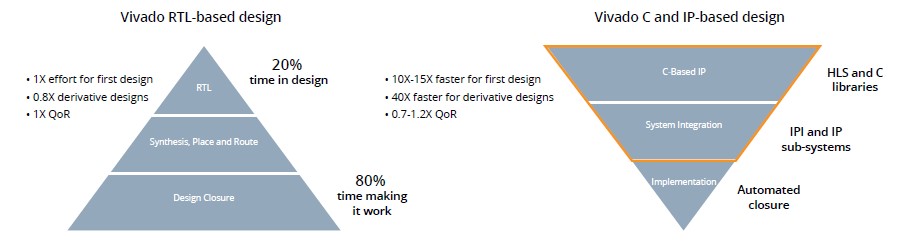

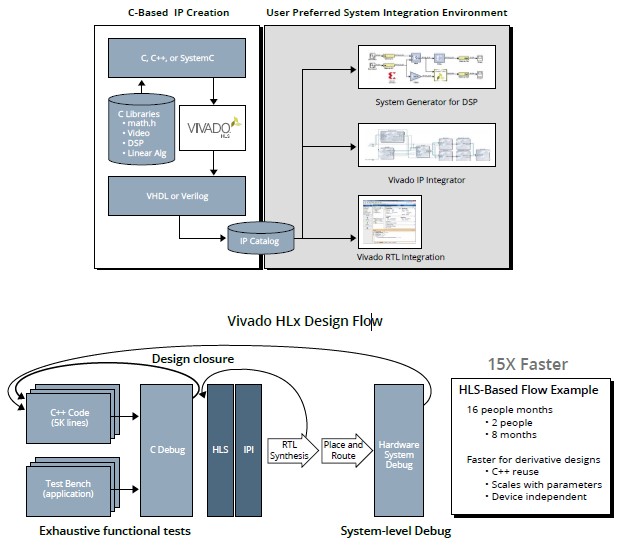

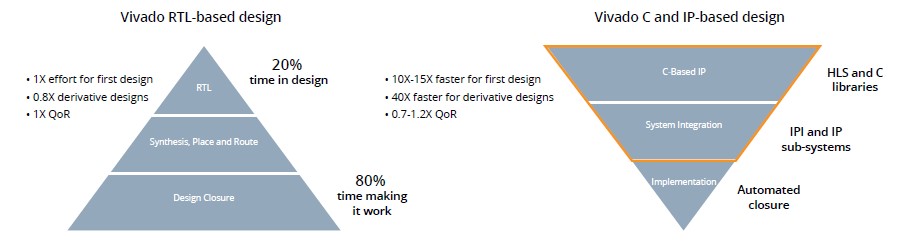

주로 디자인 프로세스 후반부에 대부분의 디자인 작업이 집중되어야 하는 기존의 RTL 기반 디자인과 달리, C 및 IP 기반 디자인은 검증 및 구현, 디자인 컨버전스 등의 개발주기를 단축시켜 주기 때문에 디자이너들은 로직의 차별화에 주력할 수 있다. 플로우는 다음과 같다:

• 필요한 소프트웨어 스택과 함께 빠른 플랫폼 커넥티비티 디자인

• 하이-레벨 디자인을 이용해 빠르게 차별화된 로직 개발. 또한 뛰어난 디자인 재사용 능력 제공

• RTL과 비교해 하이-레벨 언어로 검증 시간을 획기적으로 단축

디자인 팀은 하이-레벨 추상화를 이용해 신속하게 전반적인 성능을 향상시키거나, 성능, 전력, 활용도 측면에서 동일한 품질 결과(QoR; Quality of Results)를 얻을 수 있다.

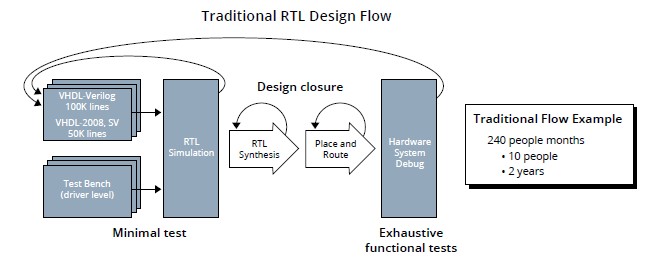

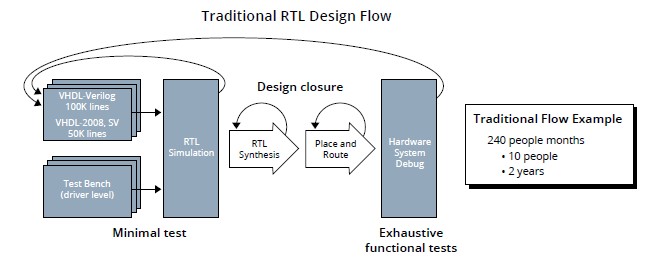

UltraFast 하이-레벨 생산성 디자인 방법론 가이드

기존 디자인 개발방법은 숙련된 시스템 설계자와 함께 새로운 기술을 어떻게 구현해야 할지 평가하고, 하이-레벨 모델링 구성방식으로 보다 뛰어난 차별화된 로직과 시스템 커넥티비티 요건을 모두 파일화하여 시작하게 된다. 그런 다음 RTL 디자인에서 이러한 요건을 구현한다. RTL 디자인 사이클은 보통 각 블록은 물론, 전체 디자인에 대한 검증 및 디자인 클로저를 반복하게 된다. 이러한 방법으로 인해 플랫폼 커넥티비는 결코 안정화될 수 없는데, 이유는 차별화된 로직 상의 변경이 가해지면, IO 인터페이스(예를 들어, DDR 메모리, 이더넷, PCIe 등)가 타이밍 요건의 실패를 유발할 수 있기 때문이다. 또한 RTL 검증 사이클은 하드웨어 구현 이전에 철저한 기능적 테스트가 가능하지 않다.

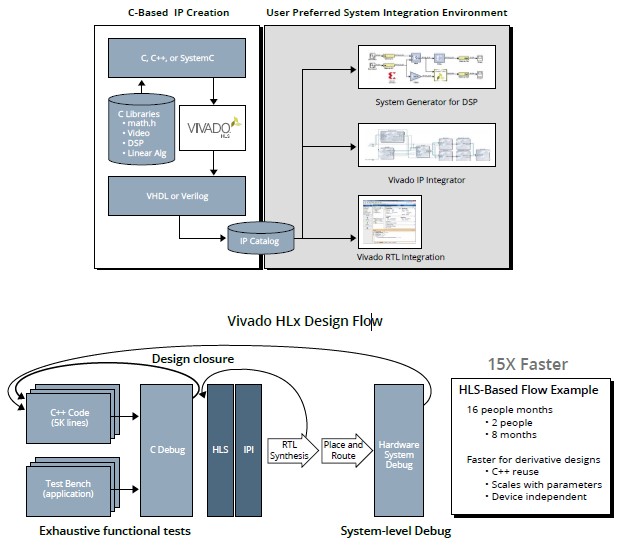

하이-레벨 디자인 방법론(High-Level Design Methodology)은 디자이너들이 RTL 코딩보다는 보다 부가가치 있는 로직을 설계하는데 더 많은 개발시간을 투자하고, 동작 검증시간을 줄일 수 있도록 해주며, 이러한 플로우는 RTL 디자인 플로우와 비교해 디자인 사이클을 15배까지 단축시켜 준다. 하이-레벨 방법론의 주요 속성(Attribute)은 다음과 같다:

• 플랫폼 개발 및 차별화된 로직을 분리함으로써 디자이너가 고유의 기능 개발에 주력할 수 있도록 해준다.

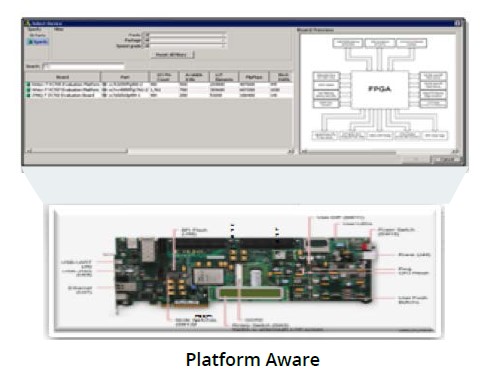

• 보드 인식(Board Awareness) 기능을 갖춘 비바도 IPI(IP Integrator)는 물론, 비바도 IP 시스템을 이용한 플랫폼 커넥티비티의 고속 구성 및 제너레이션, 클로저

• 차별화된 로직을 위한 C-기반 시뮬레이션을 통해 기존 RTL 시뮬레이션 대비 중요도에 따라 시뮬레이션 시간 감소

• 비바도 HLS(High-Level Synthesis) 하이-레벨 합성 및 C/C++ 라이브러리와 IPI는 C에서 실리콘으로 빠른 구현 및 시스템 통합 가능

UltraFast 하이-레벨 생산성 디자인 방법론 가이드의 모든 단계는 쌍방향으로 상호동작이 가능하며, 명령어 라인 스크립트를 이용할 수 있다. 디자인 시뮬레이션에서 FPGA 프로그래밍, 완전 자동화에 이르기까지 전반의 플로우에 걸친 모든 매뉴얼 상호작용의 결과는 스크립트에 저장할 수 있다. 또한 고도로 자동화된 플로우를 통해 RTL 디자인 시뮬레이션이 완료되기 전에 FPGA 비트스트림 생성 및 보드 상의 디자인 테스트가 가능하다.

한편 디자인 파생 제품을 구현하는 경우 더욱 뛰어난 생산성 향상을 얻을 수 있다. 다른 디바이스나 클럭 속도, 디자인 구성을 타깃하는 경우 C 파라미터나 비바도 HLS 옵션을 수정해 간단히 구현할 수 있다. 그러면, 이 툴은 새로운 제품 요건에 부합하는 새로운 마이크로 아키텍처를 자동으로 선택하게 된다.

HLx는 소프트웨어 프로그램이 가능한 맞춤형-플랫폼 설계를 위한 방법론을 제공함으로써 자일링스의 소프트웨어 기반 환경인 SDx 제품군을 보완하고, 구현, 디자인 수정 및 재사용을 가속화해준다.

C-기반 디자인 및 재사용 가속

일반적인 시스템은 시스템의 소프트웨어 모델로 개발이 시작된다. 엔터테인먼트나 게임, 통신, 의학에 이르기까지 대부분의 제품들은 소프트웨어 모델이나 시제품으로 시작된다. 그런 다음 이 모델은 하드웨어 및 임베디드 소프트웨어 팀으로 분배되는데, 하드웨어 디자인 팀은 시스템 요건에 부합하는 RTL 마이크로 아키텍처를 선택하는 업무를 맡게 된다.

FPGA와 같은 프로그래머블 디바이스의 가장 큰 장점은 어떠한 특정 애플리케이션에도 최적화할 수 있는 맞춤형-하드웨어를 구현할 수 있다는 점이다. 이를 통해 최종 제품은 분산형 프로세서 기반 시스템에서 구동되는 소프트웨어 프로그램 보다 훨씬 뛰어난 와트당 성능을 달성할 수 있다.

비바도 HLS 컴파일러는 프로세서 컴파일러에서 제공하는 것과 유사한 프로그래밍 환경을 제공한다. 주요 차이점은, 비바도 HLS은 C 코드를 최적화된 RTL 마이크로 아키텍처에 맞게 합성이 가능한 반면, 프로세서 기반 컴파일러는 고정된 GHz 속도의 프로세서 아키텍처 상에서 실행되도록 어셈블리 코드를 생성한다는 것이다.

또한 시스템 설계자와 소프트웨어 프로그래머, 하드웨어 엔지니어는 비바도 HLS를 이용하여 처리량 및 전력소모, 지연시간 등에 최적화된 맞춤형 하드웨어를 구현할 수 있다. 따라서 연산이나 저장, 네트워킹 등의 애플리케이션을 위한 최적의 고성능, 저전력, 저비용 시스템을 구현할 수 있다.

비바도 HLS는 디자인 요건에 기반한 다양한 마이크로 아키텍처를 검토한 후에, C/C++ 사양을 VHDL이나 Verilog RTL로 직접 합성함으로써 디자인 구현 및 검증을 가속화할 수 있다. 기능 시뮬레이션도 이 단계에서 수행이 가능한데, VHDL이나 Verilog 시뮬레이션에 비해 획기적으로 시간을 단축할 수 있다. 예를 들어, 비디오 모션 예측 알고리즘의 경우, 비바도 HLS에 입력된 C는 10초에 10개의 비디오 데이터 프레임을 실행할 수 있지만, 이에 상응하는 RTL 모델은 동일한 10개의 비디오 프레임을 처리하는데 대략 이틀이 소요된다.

비바도 IPI와 함께 비바도 HLS는 디자이너 및 시스템 설계자에게 보다 빠르고, 보다 안정적으로 탁월한 품질의 디자인을 구현할 수 있는 방법으로 제공한다.

비바도 HLS는 보다 빠른 IP 구현 방법을 제공한다

• 알고리즘 정의, 데이터 타입의 사양(정수, 고정소수점, 부동소수점), 인터페이스(FIFO, AXI4, AXI4-Lite, AXI4-Stream) 추상화

• 디렉티브(Directive) 기반 아키텍처-인식 합성 방법으로 성능 및 전력, 공간 활용도 측면에서 수작업 코딩 방식의 RTL 구현방식 보다 훨씬 뛰어나거나 필적할만한 디자인을 신속하게 달성할 수 있다.

• C/C++ 테스트 벤치 시뮬레이션 및 자동 VHDL/Verilog 시뮬레이션, 테스트 벤치 생성을 이용해 검증을 가속화한다.

• C, C++, OpenCL, SystemC 등의 다양한 언어를 지원하며, 업계에서 가장 폭넓은 언어를 커버하고 있다.

• 자일링스의 온칩 메모리 구조와 DSP(Digital Signal Processing) 연산요소, 부동소수점 라이브러리를 자동으로 사용할 수 있다.

도메인별로 특화된 소프트웨어 라이브러리

지원되는 라이브러리에는 고성능, 저전력 구현을 위한 Math, DSP, 비디오, LA(Linear Algebra) 라이브러리 등이 있다. 또한 HLS는 FFT 및 필터 등과 같은 복잡한 코어를 위해 최고의 품질결과를 제공하도록 최적화된 LogiCORE™ IP FFT 및 FIR Compiler를 통합하고 있다. 한편 도메인별로 개발을 가속화할 수 있도록, 자일링스 얼라이언스 회원사(Xilinx Alliance members)들은 OpenCV, BLAS, 머신 러닝(Machine Learning) 등을 위한 특화된 라이브러리를 제공하고 있다. 보다 자세한 정보는 http://www.xilinx.com/HLS에서 확인할 수 있다.

완벽한 IP 서브시스템 재사용

자일링스와 얼라이언스 회원사들은 제품을 빠르게 시장에 출시할 수 있도록 풍부한 IP(Intellectual Property) 라이브러리를 구축하고 있다. 이 IP들은 처음부터 성공적으로 사용될 수 있도록 다양한 테스트와 검증 작업을 거쳤다. 또한 간편한 코어 라이브러리와 더불어 생산성을 증대할 수 있는 솔루션도 공급된다.

자일링스의 새로운 LogiCORE IP 서브시스템은 데이터-무버(Data-Mover), 소프트웨어 드라이버, 예제 디자인, 테스트 벤치를 비롯해 복수의 개별 IP 코어를 통합하고 있는 마켓별로 특화된 빌딩 블록으로, 유연하게 구성이 가능하다. 비바도 디자인 수트에서 제공되는 새로운 IP 서브시스템은 이더넷, PCIe, HDMI, 비디오 프로세싱, 이미지 센서 프로세싱, OTN 개발 등 다양하다. 예를 들어, AXI-4 PCIe 서브시스템은 PCIe, DMA, AXI-4 인터커넥트를 비롯한 복수의 IP 코어를 활용하고 있으며, 프로세서 시스템에 사용되는 필요한 소프트웨어 스택도 공급한다.

모든 IP 서브시스템은 산업 표준인 AMBA® AXI™4 인터커넥트 프로토콜 및 IEEE P1735 암호화, XDC 디자인 제약조건(Constraint) 등에 기반하고 있으며, 통합이 용이하도록 사용자 및 자일링스 얼라이언스 회원사의 패키지 IP와 상호 운용성이 지원된다.

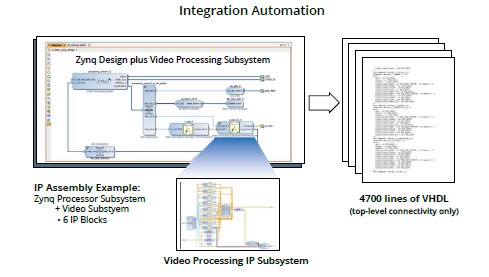

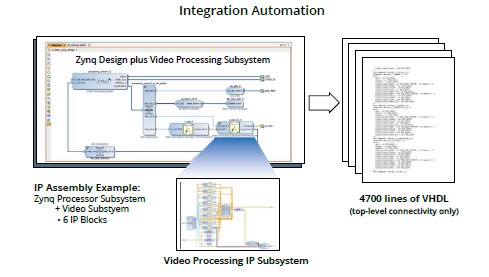

통합 자동화

비바도 디자인 수트는 업계 최초의 플러그&플레이 시스템 통합 디자인 환경인 비바도 IPI를 통해 RTL 디자인 생산성을 획기적으로 개선할 수 있다.

비바도 IPI는 보드 인터페이스를 위해 원하는 형식의 커넥티비티를 생성함으로써 빠르게 플랫폼을 구현할 수 있다. 또한 플랫폼 상에 C/C++로 생성된 여러 기능이 동시에 공존하는 시스템 어셈블리가 가능하다.

비바도 IPI는 그래픽 방식의 Tcl-기반 자동오류제거(Correct-by-Construction) 디자인 개발 플로우를 제공한다. 이는 지능형 핵심 인터페이스 자동연결 및 원클릭 서브시스템 생성, 실시간 DRC, 인터페이스 변경 전파, 그리고 강력한 디버깅 기능까지 지원하는 디바이스 및 플랫폼 인식 기반 상호 동작이 가능한 쌍방향 환경을 제공한다.

디자이너는 기능을 서로 연결할 때 추상화된 ‘신호’ 레벨이 아닌, ‘인터페이스’로 작업이 가능하기 때문에 생산성을 획기적으로 향상시킬 수 있다. IPI는 업계 표준 AXI4를 활용하고는 있지만, 다른 인터페이스 또한 지원하며, 사용자는 보다 유연성있게 자체 맞춤형 인터페이스를 정의할 수도 있다.

비바도 디자인 수트는 개방형 산업 IP 표준을 통해, 협력업체들이 자사의 IP 포트폴리오를 비바도 IPI로 통합할 수 있도록 개발자들을 지원하고 있다. 또한 사용자는 비바도 IP packager와 함께 비바도 HLS 및 DSP를 위한 시스템 제너레이터(System Generator)를 이용해 자신의 고유의 RTL이나 C/C++/SystemC, MATLAB®/Simulink® 알고리즘을 IP 카탈로그에 통합할 수도 있다.

클로저 가속

비바도 디자인 수트는 하루에 더 많은 실행이 가능하기 때문에 구현 프로세스를 가속화하는 것은 물론, 필요한 디자인 반복 수를 줄여준다. 또한 공유 및 확장 가능한 데이터 모델을 통해 전례없는 컴파일 시간과 메모리 사용량을 제공하며, 전력, 타이밍, 리소스 활용도와 같은 핵심 디자인 요소들을 조기에 분석할 수 있다. 이러한 요소들은 반복이 보다 빠른 디자인 초기단계에서 시스템 성능에 더 많은 영향을 미치는 디자인 및 툴 설정을 수정할 수 있도록 해준다.

하이-레벨 디자인 방법론을 이용해 반복은 C/C++ 레벨에서 더욱 가속화될 수 있으며, 반복이 더욱 빨라지고, 더 많은 영향을 미치는, 최종 단계에서 P&R 클로저의 반복 필요성 및 영향을 감소시켜 준다.

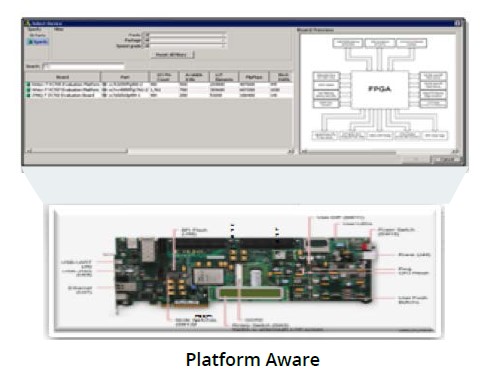

플랫폼 생성 및 재사용

비바도 디자인 수트는 징크 SoC, MPSoC는 물론, ASIC 등급의 FPGA 및 3D IC 보드 및 키트를 지원하는 디바이스 인식, 즉 타깃 플랫폼 인식 기능을 갖추고 있다. 타깃 플랫폼을 인식함으로써 비바도는 보드에 특화된 DRC(Design Rule Checks)를 구성, 적용하여 신속하게 시스템을 동작시킬 수 있다.

예를 들어, 징크-7000 올 프로그래머블(All Programmable) SoC ZC702 평가키트(Evaluation Kit)를 선택하고, IPI로 징크 프로세싱 시스템을 구성함으로써, 비바도는 보드를 지원하는 적절한 주변장치와 드라이버, 메모리 맵으로 프로세싱 시스템을 미리 구성한다. 또한 플랫폼 디자이너는 듀얼 코어 ARM® 프로세싱 시스템과 고성능 FPGA 로직을 타깃하여 보다 빠르게 소프트웨어 및 하드웨어 IP를 통합하고, 재사용하고, 확인할 수 있게 되었다.

사용자는 프로세싱 시스템 및 로직 간의 인터페이스를 일련의 대화상자를 통해 손쉽게 지정할 수 있다. 이 인터페이스는 성능 및 공간에 맞게 자동으로 생성 및 최적화되며, 사용자는 비바도 HLS 또는 비바도 IP 카탈로그를 사용하여 자체 알고리즘을 추가함으로써 고유의 디자인을 완성할 수 있다.

결론

복잡하면서도, 보다 스마트한 시스템을 신속하게 개발하기 위해서는 RTL 레벨 디자인을 넘어서는 자동화 단계가 필요하다. 비바도 디자인 수트 HLx 에디션은 이를 위해 특화된 솔루션이다.

새로운 비바도 HLx 에디션은 차세대 플랫폼 디자인 자동화를 비롯해 C/C++ 프로그래밍 기반의 차별화된 로직, 그래픽 시스템 어셈블리를 통해 획기적으로 생산성을 증대시킬 수 있는 새로운 접근방식을 제공한다. 이 접근법은 UltraFast 하이-레벨 생산성 디자인 방법론 가이드(UG1197)에 설명되어 있으며, RTL 기반 방법론에 비해 디자인 생성 및 검증시간을 15배까지 단축시킬 수 있는 것으로 확인되었다.

또한 HLx는 소프트웨어 및 시스템 엔지니어에게 최적화된 자일링스의 SDx 개발환경(SDSoC, SDAccel, SDNet)을 보완해 준다. HLx 방법론은 플랫폼 디자인 생성을 자동화하고, SDx 제품군 개발환경은 C, C++, OpenCL이나 패킷 프로세싱을 위한 새로운 P4 언어를 이용해 이러한 플랫폼의 소프트웨어 정의(Software-Defined) 기반 프로그래밍이 가능하도록 해준다.

HLx 및 SDx는 자일링스의 새로운 소프트웨어 프로래머빌리티 솔루션 분야를 대표하는 제품군으로, 징크 SoC 및 MPSoC, ASIC-등급 FPGA, 3D IC를 포함한 모든 올 프로그래머블 디바이스를 이용한 맞춤형 하드웨어에 최적화된 최종 제품을 활용하여 보다 스마트하고 차별화된 커넥티드 시스템을 개발할 수 있도록 해준다.

시스템 플랫폼의 효율적인 적용 및 구현을 위해 획기적인 생산성을 제공하는 새로운 접근법

비바도 디자인 수트(Vivado® Design Suite)는 차세대 C/C++ 및 IP 기반 디자인의 생산성을 획기적으로 향상시켜주는 새로운 접근법을 제공한다. 새로운 HLx 에디션은 HL 시스템 에디션 및 HL 디자인 에디션, HL WebPACK™ 에디션을 포함하고 있다. 사용자는 새로운 UltraFast™ 하이-레벨 생산성 디자인 방법론 가이드(High-Level Productivity Design Methodology Guide)를 이용해 기존의 접근방식 대비 10배에서 15배의 생산성 향상을 실현할 수 있다.

<비바도 디자인 수트(Vivado Design Suite) HLx 에디션>

15배의 생산성 향상 실현:

• C/C++ 기반 디자인 및 재사용 가속화

• 도메인별로 특화된 라이브러리

• IP 서브시스템

• 통합 자동화

• 더 빨라진 디자인 클로저

• 빠른 플랫폼 생성 및 구축 가능

• 징크(Zynq) SoC 및 새로운 MPSoC와 더불어 ASIC급 FPGA 및 3D IC 지원

주로 디자인 프로세스 후반부에 대부분의 디자인 작업이 집중되어야 하는 기존의 RTL 기반 디자인과 달리, C 및 IP 기반 디자인은 검증 및 구현, 디자인 컨버전스 등의 개발주기를 단축시켜 주기 때문에 디자이너들은 로직의 차별화에 주력할 수 있다. 플로우는 다음과 같다:

• 필요한 소프트웨어 스택과 함께 빠른 플랫폼 커넥티비티 디자인

• 하이-레벨 디자인을 이용해 빠르게 차별화된 로직 개발. 또한 뛰어난 디자인 재사용 능력 제공

• RTL과 비교해 하이-레벨 언어로 검증 시간을 획기적으로 단축

디자인 팀은 하이-레벨 추상화를 이용해 신속하게 전반적인 성능을 향상시키거나, 성능, 전력, 활용도 측면에서 동일한 품질 결과(QoR; Quality of Results)를 얻을 수 있다.

UltraFast 하이-레벨 생산성 디자인 방법론 가이드

기존 디자인 개발방법은 숙련된 시스템 설계자와 함께 새로운 기술을 어떻게 구현해야 할지 평가하고, 하이-레벨 모델링 구성방식으로 보다 뛰어난 차별화된 로직과 시스템 커넥티비티 요건을 모두 파일화하여 시작하게 된다. 그런 다음 RTL 디자인에서 이러한 요건을 구현한다. RTL 디자인 사이클은 보통 각 블록은 물론, 전체 디자인에 대한 검증 및 디자인 클로저를 반복하게 된다. 이러한 방법으로 인해 플랫폼 커넥티비는 결코 안정화될 수 없는데, 이유는 차별화된 로직 상의 변경이 가해지면, IO 인터페이스(예를 들어, DDR 메모리, 이더넷, PCIe 등)가 타이밍 요건의 실패를 유발할 수 있기 때문이다. 또한 RTL 검증 사이클은 하드웨어 구현 이전에 철저한 기능적 테스트가 가능하지 않다.

하이-레벨 디자인 방법론(High-Level Design Methodology)은 디자이너들이 RTL 코딩보다는 보다 부가가치 있는 로직을 설계하는데 더 많은 개발시간을 투자하고, 동작 검증시간을 줄일 수 있도록 해주며, 이러한 플로우는 RTL 디자인 플로우와 비교해 디자인 사이클을 15배까지 단축시켜 준다. 하이-레벨 방법론의 주요 속성(Attribute)은 다음과 같다:

• 플랫폼 개발 및 차별화된 로직을 분리함으로써 디자이너가 고유의 기능 개발에 주력할 수 있도록 해준다.

• 보드 인식(Board Awareness) 기능을 갖춘 비바도 IPI(IP Integrator)는 물론, 비바도 IP 시스템을 이용한 플랫폼 커넥티비티의 고속 구성 및 제너레이션, 클로저

• 차별화된 로직을 위한 C-기반 시뮬레이션을 통해 기존 RTL 시뮬레이션 대비 중요도에 따라 시뮬레이션 시간 감소

• 비바도 HLS(High-Level Synthesis) 하이-레벨 합성 및 C/C++ 라이브러리와 IPI는 C에서 실리콘으로 빠른 구현 및 시스템 통합 가능

UltraFast 하이-레벨 생산성 디자인 방법론 가이드의 모든 단계는 쌍방향으로 상호동작이 가능하며, 명령어 라인 스크립트를 이용할 수 있다. 디자인 시뮬레이션에서 FPGA 프로그래밍, 완전 자동화에 이르기까지 전반의 플로우에 걸친 모든 매뉴얼 상호작용의 결과는 스크립트에 저장할 수 있다. 또한 고도로 자동화된 플로우를 통해 RTL 디자인 시뮬레이션이 완료되기 전에 FPGA 비트스트림 생성 및 보드 상의 디자인 테스트가 가능하다.

한편 디자인 파생 제품을 구현하는 경우 더욱 뛰어난 생산성 향상을 얻을 수 있다. 다른 디바이스나 클럭 속도, 디자인 구성을 타깃하는 경우 C 파라미터나 비바도 HLS 옵션을 수정해 간단히 구현할 수 있다. 그러면, 이 툴은 새로운 제품 요건에 부합하는 새로운 마이크로 아키텍처를 자동으로 선택하게 된다.

HLx는 소프트웨어 프로그램이 가능한 맞춤형-플랫폼 설계를 위한 방법론을 제공함으로써 자일링스의 소프트웨어 기반 환경인 SDx 제품군을 보완하고, 구현, 디자인 수정 및 재사용을 가속화해준다.

C-기반 디자인 및 재사용 가속

일반적인 시스템은 시스템의 소프트웨어 모델로 개발이 시작된다. 엔터테인먼트나 게임, 통신, 의학에 이르기까지 대부분의 제품들은 소프트웨어 모델이나 시제품으로 시작된다. 그런 다음 이 모델은 하드웨어 및 임베디드 소프트웨어 팀으로 분배되는데, 하드웨어 디자인 팀은 시스템 요건에 부합하는 RTL 마이크로 아키텍처를 선택하는 업무를 맡게 된다.

FPGA와 같은 프로그래머블 디바이스의 가장 큰 장점은 어떠한 특정 애플리케이션에도 최적화할 수 있는 맞춤형-하드웨어를 구현할 수 있다는 점이다. 이를 통해 최종 제품은 분산형 프로세서 기반 시스템에서 구동되는 소프트웨어 프로그램 보다 훨씬 뛰어난 와트당 성능을 달성할 수 있다.

비바도 HLS 컴파일러는 프로세서 컴파일러에서 제공하는 것과 유사한 프로그래밍 환경을 제공한다. 주요 차이점은, 비바도 HLS은 C 코드를 최적화된 RTL 마이크로 아키텍처에 맞게 합성이 가능한 반면, 프로세서 기반 컴파일러는 고정된 GHz 속도의 프로세서 아키텍처 상에서 실행되도록 어셈블리 코드를 생성한다는 것이다.

또한 시스템 설계자와 소프트웨어 프로그래머, 하드웨어 엔지니어는 비바도 HLS를 이용하여 처리량 및 전력소모, 지연시간 등에 최적화된 맞춤형 하드웨어를 구현할 수 있다. 따라서 연산이나 저장, 네트워킹 등의 애플리케이션을 위한 최적의 고성능, 저전력, 저비용 시스템을 구현할 수 있다.

비바도 HLS는 디자인 요건에 기반한 다양한 마이크로 아키텍처를 검토한 후에, C/C++ 사양을 VHDL이나 Verilog RTL로 직접 합성함으로써 디자인 구현 및 검증을 가속화할 수 있다. 기능 시뮬레이션도 이 단계에서 수행이 가능한데, VHDL이나 Verilog 시뮬레이션에 비해 획기적으로 시간을 단축할 수 있다. 예를 들어, 비디오 모션 예측 알고리즘의 경우, 비바도 HLS에 입력된 C는 10초에 10개의 비디오 데이터 프레임을 실행할 수 있지만, 이에 상응하는 RTL 모델은 동일한 10개의 비디오 프레임을 처리하는데 대략 이틀이 소요된다.

비바도 IPI와 함께 비바도 HLS는 디자이너 및 시스템 설계자에게 보다 빠르고, 보다 안정적으로 탁월한 품질의 디자인을 구현할 수 있는 방법으로 제공한다.

비바도 HLS는 보다 빠른 IP 구현 방법을 제공한다

• 알고리즘 정의, 데이터 타입의 사양(정수, 고정소수점, 부동소수점), 인터페이스(FIFO, AXI4, AXI4-Lite, AXI4-Stream) 추상화

• 디렉티브(Directive) 기반 아키텍처-인식 합성 방법으로 성능 및 전력, 공간 활용도 측면에서 수작업 코딩 방식의 RTL 구현방식 보다 훨씬 뛰어나거나 필적할만한 디자인을 신속하게 달성할 수 있다.

• C/C++ 테스트 벤치 시뮬레이션 및 자동 VHDL/Verilog 시뮬레이션, 테스트 벤치 생성을 이용해 검증을 가속화한다.

• C, C++, OpenCL, SystemC 등의 다양한 언어를 지원하며, 업계에서 가장 폭넓은 언어를 커버하고 있다.

• 자일링스의 온칩 메모리 구조와 DSP(Digital Signal Processing) 연산요소, 부동소수점 라이브러리를 자동으로 사용할 수 있다.

도메인별로 특화된 소프트웨어 라이브러리

지원되는 라이브러리에는 고성능, 저전력 구현을 위한 Math, DSP, 비디오, LA(Linear Algebra) 라이브러리 등이 있다. 또한 HLS는 FFT 및 필터 등과 같은 복잡한 코어를 위해 최고의 품질결과를 제공하도록 최적화된 LogiCORE™ IP FFT 및 FIR Compiler를 통합하고 있다. 한편 도메인별로 개발을 가속화할 수 있도록, 자일링스 얼라이언스 회원사(Xilinx Alliance members)들은 OpenCV, BLAS, 머신 러닝(Machine Learning) 등을 위한 특화된 라이브러리를 제공하고 있다. 보다 자세한 정보는 http://www.xilinx.com/HLS에서 확인할 수 있다.

완벽한 IP 서브시스템 재사용

자일링스와 얼라이언스 회원사들은 제품을 빠르게 시장에 출시할 수 있도록 풍부한 IP(Intellectual Property) 라이브러리를 구축하고 있다. 이 IP들은 처음부터 성공적으로 사용될 수 있도록 다양한 테스트와 검증 작업을 거쳤다. 또한 간편한 코어 라이브러리와 더불어 생산성을 증대할 수 있는 솔루션도 공급된다.

자일링스의 새로운 LogiCORE IP 서브시스템은 데이터-무버(Data-Mover), 소프트웨어 드라이버, 예제 디자인, 테스트 벤치를 비롯해 복수의 개별 IP 코어를 통합하고 있는 마켓별로 특화된 빌딩 블록으로, 유연하게 구성이 가능하다. 비바도 디자인 수트에서 제공되는 새로운 IP 서브시스템은 이더넷, PCIe, HDMI, 비디오 프로세싱, 이미지 센서 프로세싱, OTN 개발 등 다양하다. 예를 들어, AXI-4 PCIe 서브시스템은 PCIe, DMA, AXI-4 인터커넥트를 비롯한 복수의 IP 코어를 활용하고 있으며, 프로세서 시스템에 사용되는 필요한 소프트웨어 스택도 공급한다.

모든 IP 서브시스템은 산업 표준인 AMBA® AXI™4 인터커넥트 프로토콜 및 IEEE P1735 암호화, XDC 디자인 제약조건(Constraint) 등에 기반하고 있으며, 통합이 용이하도록 사용자 및 자일링스 얼라이언스 회원사의 패키지 IP와 상호 운용성이 지원된다.

통합 자동화

비바도 디자인 수트는 업계 최초의 플러그&플레이 시스템 통합 디자인 환경인 비바도 IPI를 통해 RTL 디자인 생산성을 획기적으로 개선할 수 있다.

비바도 IPI는 보드 인터페이스를 위해 원하는 형식의 커넥티비티를 생성함으로써 빠르게 플랫폼을 구현할 수 있다. 또한 플랫폼 상에 C/C++로 생성된 여러 기능이 동시에 공존하는 시스템 어셈블리가 가능하다.

비바도 IPI는 그래픽 방식의 Tcl-기반 자동오류제거(Correct-by-Construction) 디자인 개발 플로우를 제공한다. 이는 지능형 핵심 인터페이스 자동연결 및 원클릭 서브시스템 생성, 실시간 DRC, 인터페이스 변경 전파, 그리고 강력한 디버깅 기능까지 지원하는 디바이스 및 플랫폼 인식 기반 상호 동작이 가능한 쌍방향 환경을 제공한다.

디자이너는 기능을 서로 연결할 때 추상화된 ‘신호’ 레벨이 아닌, ‘인터페이스’로 작업이 가능하기 때문에 생산성을 획기적으로 향상시킬 수 있다. IPI는 업계 표준 AXI4를 활용하고는 있지만, 다른 인터페이스 또한 지원하며, 사용자는 보다 유연성있게 자체 맞춤형 인터페이스를 정의할 수도 있다.

비바도 디자인 수트는 개방형 산업 IP 표준을 통해, 협력업체들이 자사의 IP 포트폴리오를 비바도 IPI로 통합할 수 있도록 개발자들을 지원하고 있다. 또한 사용자는 비바도 IP packager와 함께 비바도 HLS 및 DSP를 위한 시스템 제너레이터(System Generator)를 이용해 자신의 고유의 RTL이나 C/C++/SystemC, MATLAB®/Simulink® 알고리즘을 IP 카탈로그에 통합할 수도 있다.

클로저 가속

비바도 디자인 수트는 하루에 더 많은 실행이 가능하기 때문에 구현 프로세스를 가속화하는 것은 물론, 필요한 디자인 반복 수를 줄여준다. 또한 공유 및 확장 가능한 데이터 모델을 통해 전례없는 컴파일 시간과 메모리 사용량을 제공하며, 전력, 타이밍, 리소스 활용도와 같은 핵심 디자인 요소들을 조기에 분석할 수 있다. 이러한 요소들은 반복이 보다 빠른 디자인 초기단계에서 시스템 성능에 더 많은 영향을 미치는 디자인 및 툴 설정을 수정할 수 있도록 해준다.

하이-레벨 디자인 방법론을 이용해 반복은 C/C++ 레벨에서 더욱 가속화될 수 있으며, 반복이 더욱 빨라지고, 더 많은 영향을 미치는, 최종 단계에서 P&R 클로저의 반복 필요성 및 영향을 감소시켜 준다.

플랫폼 생성 및 재사용

비바도 디자인 수트는 징크 SoC, MPSoC는 물론, ASIC 등급의 FPGA 및 3D IC 보드 및 키트를 지원하는 디바이스 인식, 즉 타깃 플랫폼 인식 기능을 갖추고 있다. 타깃 플랫폼을 인식함으로써 비바도는 보드에 특화된 DRC(Design Rule Checks)를 구성, 적용하여 신속하게 시스템을 동작시킬 수 있다.

예를 들어, 징크-7000 올 프로그래머블(All Programmable) SoC ZC702 평가키트(Evaluation Kit)를 선택하고, IPI로 징크 프로세싱 시스템을 구성함으로써, 비바도는 보드를 지원하는 적절한 주변장치와 드라이버, 메모리 맵으로 프로세싱 시스템을 미리 구성한다. 또한 플랫폼 디자이너는 듀얼 코어 ARM® 프로세싱 시스템과 고성능 FPGA 로직을 타깃하여 보다 빠르게 소프트웨어 및 하드웨어 IP를 통합하고, 재사용하고, 확인할 수 있게 되었다.

사용자는 프로세싱 시스템 및 로직 간의 인터페이스를 일련의 대화상자를 통해 손쉽게 지정할 수 있다. 이 인터페이스는 성능 및 공간에 맞게 자동으로 생성 및 최적화되며, 사용자는 비바도 HLS 또는 비바도 IP 카탈로그를 사용하여 자체 알고리즘을 추가함으로써 고유의 디자인을 완성할 수 있다.

결론

복잡하면서도, 보다 스마트한 시스템을 신속하게 개발하기 위해서는 RTL 레벨 디자인을 넘어서는 자동화 단계가 필요하다. 비바도 디자인 수트 HLx 에디션은 이를 위해 특화된 솔루션이다.

새로운 비바도 HLx 에디션은 차세대 플랫폼 디자인 자동화를 비롯해 C/C++ 프로그래밍 기반의 차별화된 로직, 그래픽 시스템 어셈블리를 통해 획기적으로 생산성을 증대시킬 수 있는 새로운 접근방식을 제공한다. 이 접근법은 UltraFast 하이-레벨 생산성 디자인 방법론 가이드(UG1197)에 설명되어 있으며, RTL 기반 방법론에 비해 디자인 생성 및 검증시간을 15배까지 단축시킬 수 있는 것으로 확인되었다.

또한 HLx는 소프트웨어 및 시스템 엔지니어에게 최적화된 자일링스의 SDx 개발환경(SDSoC, SDAccel, SDNet)을 보완해 준다. HLx 방법론은 플랫폼 디자인 생성을 자동화하고, SDx 제품군 개발환경은 C, C++, OpenCL이나 패킷 프로세싱을 위한 새로운 P4 언어를 이용해 이러한 플랫폼의 소프트웨어 정의(Software-Defined) 기반 프로그래밍이 가능하도록 해준다.

HLx 및 SDx는 자일링스의 새로운 소프트웨어 프로래머빌리티 솔루션 분야를 대표하는 제품군으로, 징크 SoC 및 MPSoC, ASIC-등급 FPGA, 3D IC를 포함한 모든 올 프로그래머블 디바이스를 이용한 맞춤형 하드웨어에 최적화된 최종 제품을 활용하여 보다 스마트하고 차별화된 커넥티드 시스템을 개발할 수 있도록 해준다.

- 적용분야 :

- High Performance Computing

- 관련제품 :

- ZYNQ