Technical Article

제품 및 Tools

업계 최초로 Softly Defined Network 실현

업계 최초로 Softly Defined Network 실현

2014-06-02

업계 최초로 Softly Defined Network 실현

개요

수년 간의 연구작업과 방대한 투자가 정점에 이르면서, 자일링스(Xilinx)는 드디어 새로운 SDNet(Software Defined Specification Environment for Networking)을 공개했다. SDNet은 하이 레벨 사용자 지정 사양을 고도로 최적화된 올 프로그래머블(All Programmable) FPGA 및 SoC에 합성하는 방식으로 고성능 패킷 프로세싱 시스템을 손쉽게 구현할 수 있도록 해준다. 보다 구체적으로 말하면, 자일링스의 올 프로그래머블 디바이스와 함께 SDNet은 기술적 과도기에 Softly Defined Network을 구현할 수 있다는 것이다. Softly Defined Network은 SDN(Software Defined Network) 객체를 지원할 뿐만 아니라, 콘텐트 인텔리전스(Content Intelligence)를 갖춘 소프트웨어로 정의된 데이터 플레인 하드웨어를 지원함으로써 새로운 변화에 대응할 수 있다.

이 글은 SDNet의 다양한 기능을 이해하고자 하는 네트워킹 시스템 설계자 및 엔지니어링 매니저들이 까다로운 기술적인 문제들을 해결하고, 궁극적으로 올 프로그래머블 및 보다 스마트한 Softly Defined Networks을 구축하는데 어떻게 적용할 것인지를 결정하는데 도움을 주고자 작성되었다. 이 글과 더불어, SDNet의 특정 기능을 다루고 있는 다른 컨설팅 자료를 통해서도 관심영역을 보다 더 깊이 이해할 수 있기를 바란다.

Softly Defined Network의 필요성

지속적으로 진화하고 있는 사용자들의 요구를 해결하기 위해, 네트워크 시스템 벤더들은 개발 사이클을 수년에서 수개월로 줄이는 것은 물론, SDN을 비롯한 새로운 네트워킹 토폴로지를 반드시 지원해야 한다. 이는 빠른 표준의 발전과 새로운 커넥티비티 옵션, 그리고 처리량 및 인터페이스 옵션, 사이즈가 각기 다른 다중 라인 카드에 걸쳐 동적으로 혹은 통일된 방식으로 확장이 가능해야 하는 OTT(Over-The-Top) 서비스의 등장으로 인해 더욱 가속화되고 있다. 이와 동시에 통신 사업자들은 프로비저닝 및 매니지먼트, 자본지출 등을 간소화하기 위해 SDN 및 NFV와 같은 새로운 네트워크 아키텍처에 대해서도 검토하고 있다. 이상적인 솔루션은 소프트웨어로 제어할 수 있고, 커스텀 하드웨어 구현으로 새로운 기능을 수용할 수 있는 유입에서 유출까지 완벽한 프로그래머블 및 확장 가능한 라인 카드이다.

지나치게 증가하고 있는 개발 비용과 늘어나는 개발 주기, 그리고 근본적인 유연성 부족 등은 장비 공급업체들이 기존 제품에서 차세대 ASIC으로의 마이그레이션을 저해한다. 성공적인 ASIC 프로젝트라 하더라도 부가적인 ‘미래 지향적(Future-Proofing)’인 리소스들은 계속 축적되기 때문에 비용, 크기, 전력, 오버헤드는 반드시 추가되기 마련이다. 전체적으로 매우 소수의 시스템 벤더들이 내부 데이터 플레인 ASIC을 50~100Gbit/sec 데이터 레이트 이상으로 확장하고자 시도하고 있다. 한편 서로 전혀 다른 새로운 애플리케이션 요건들과 데이터 레이트는 ASSP 벤더들에게도 이와 유사한 방식으로 영향을 미치고 있기 때문에 상용 실리콘 공급에서도 갭이 유발되고 있다. 간단하게 말해서, 고정형 실리콘 솔루션 비즈니스는 빠르게 자취를 감추고 있다.

ASIC 및 ASSP 벤더들이 네트워킹 분야의 문제들을 해결하고자 노력하고 있는 반면, IT 산업은 기존의 경계를 허물고 더욱 새롭게 진화하고 있다. 새롭게 부상하는 경향 중 하나는 IT 설계자들이 고정된 기능의 ASIC이나 보다 유연한 상용 NPU 기반의 라인 카드의 가치에 의문을 제기하면서 소프트웨어로 제어가 가능한 일련의 동적인 가상 서비스로 진화할 수 있는 하드웨어를 추구하고 있다는 것이다. 하지만 고도의 기능들을 소프트웨어로 처리하고, 간단한 스위칭 하드웨어에만 기반한 솔루션은 성능 요건을 달성할 수 없으며, 컨텍스트도 매우 제한적일 수밖에 없다.

올 프로그래머블 FPGA 및 SoC는 소프트웨어로 프로그램이 가능한 고도로 유연한 하드웨어에 대한 요구를 해결할 수 있는 가능성을 가지고 있다. 유입에서 유출까지 거의 모든 라인 카드의 기능은 최신 올 프로그래머블 디바이스를 이용한 프로그래머블 기술을 통해 구현이 가능하며, 차세대 네트워크 플랫폼과 관련된 필요한 최대 속도와 패킷 프로세싱 레이트를 지원할 수 있다.

자일링스는 차세대 프로그래머블 네트워킹 플랫폼을 유연하게 구현 가능한 네트워킹, 즉 Softly Defined Networking 디바이스로 명명했으며, SDN은 물론, 그 이후의 기능까지 해결할 수 있는 성능 및 소프트웨어, 하드웨어 측면의 모든 올 프로그래머블의 특성을 강조하고 있다.

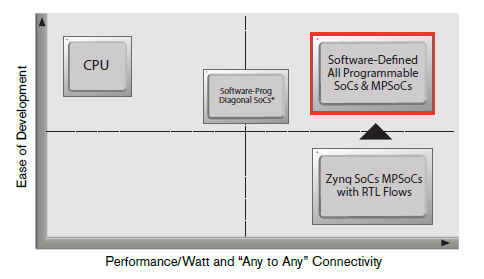

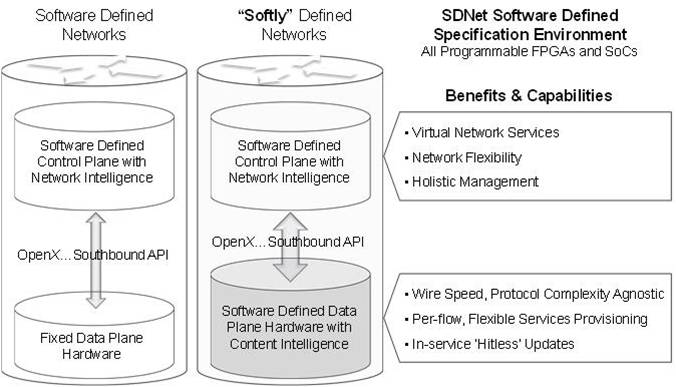

그림 1. SDN(Softly Defined Networking)으로의 진화

그림 1은 네트워크 디바이스(스위치, 라우터, 관련 기기들)의 발전을 보여주고 있다. 첫 번째 단계는 개방형의 유연한 소프트웨어 컨트롤을 통해 소프트웨어로 정의된 네트워킹으로 나아가고 있는 광범위한 흐름을 보여주고 있지만, 하드웨어는 폐쇄형의 단순한 고정형이다. 두 번째 단계는 더 나아가 최신 차동 콘텐트-지향적 네트워킹의 성능 및 과제를 해결하기 위해 개방형의 유연하고 복잡한 하드웨어 데이터 플레인을 갖춘 자일링스의 유연하게 정의된 네트워킹, 즉 Softly Defined Networking으로 진화되는 것을 볼 수 있다. 소프트웨어로 정의된 네트워킹의 제한된 Southbound API가 훨씬 풍부해지면서 상당한 규모의 고속 데이터 플레인 리프로그래밍을 지원하고, 데이터 플레인에서 프로그램된 트래픽 분석을 회수할 수 있다. 소프트웨어 정의된 데이터 플레인 하드웨어에서 얻을 수 있는 부가적인 장점은 상당하며, 여기에는 WSPA(Wire-Speed Protocol-Agnostic) 지원, 고도로 유연한 향상된 QoS(Quality of Service), 플로우 및 세션 인식 기능 등이 있으며, 이외에도 네트워크 가상화, NFV(Network Functions Virtualization), 사용자 정의 및 커스텀 기능을 지원한다.

혁신적인 자일링스의 SDNet 사양 환경은 유연하게 정의된 네트워킹, 즉 Softly Defined Networking으로 이행할 수 있도록 해주며, 자일링스 올 프로그래머블 디바이스 상에 패킷 프로세싱 기능을 빠르게 프로토타이핑 및 개발, 구축할 수 있도록 해준다. 패킷 프로세싱 요건의 자동 매핑 기능으로 최적의 프로그래머블 하드웨어를 구현할 수 있는 하이-레벨 기능 사양의 도입 방법은 업계 및 기술 판도를 변화시키고 있다.

SDNet 사양 환경의 개요

SDNet 환경의 기반은 일련의 통합 개발 툴로 처리되는 하이-레벨 네트워킹 사양을 사용하는 것이다. 이는 사용자들이 어떠한 세부 구현법을 사용하지 않고도 필요한 패킷 프로세싱 기능을 원래의 방법대로 서술하는 것이 가능하다. 그런 다음, 이 사양은 최적의 비용과 전력, 성능에서 최대 속도를 제공하는 자일링스의 올 프로그래머블 디바이스 상에 최적의 하드웨어 구현 형태로 자동 전환된다. 이것이 바로 유연하게 정의된 네트워킹, Softly Defined Networking에 이르는 방법이다.

SDNet 통합 개발 환경의 주요 컴포넌트는 다음과 같다:

특정 기능을 위한 커스텀 하드웨어 컴포넌트 생성(예, 파싱(Parsing), 에디팅)

사용자 요건에 부합하는 커스텀 패킷 데이터 플레인 하드웨어 서브 시스템 생성

생성된 SDNet 하드웨어 아키텍처를 위한 커스텀 펌웨어 생성

디버깅 및 검증을 위한 테스트 벤치 생성

SDNet 환경에서 생성되는 패킷 프로세싱 아키텍처는 히트리스(Hitless) 업데이트를 지원하는데, 라인-레이트 서비스를 전혀 방해하지 않고 패킷 간에 데이터 플레인 프로세싱 기능이 변경될 수 있다. 이러한 가동 중의 변경은 커스텀 펌웨어 업데이트를 통해 가능하며, 또한 사용자들이 만든 SDNet 사양 변경을 통해서도 생성된다.

SDNet은 자일링스의 최적화된 네트워킹을 위한 SmartCOREs™와 커넥비티 및 외부 메모리 제어, 임베디드 프로세서를 위한 LogiCOREs™를 통합할 수 있다. 이는 업계 선도적인 자일링스의 비바도(Vivado®) 디자인 환경과 SDNet이 결합됨으로써 달성할 수 있다.

SDNet 환경은 확장이 가능하기 때문에 사용자가 제공한 컴포넌트를 통합할 수 있다:

긴밀한 하드웨어 통합: 사용자 엔진을 SDNet에 도입

외부 하드웨어 통합: 사용자 IP 블록을 완성된 SDNet 하드웨어 블록과 연결

소프트웨어 통합: 사용자 소프트웨어를 SDNet 매니지먼트 API와 연결

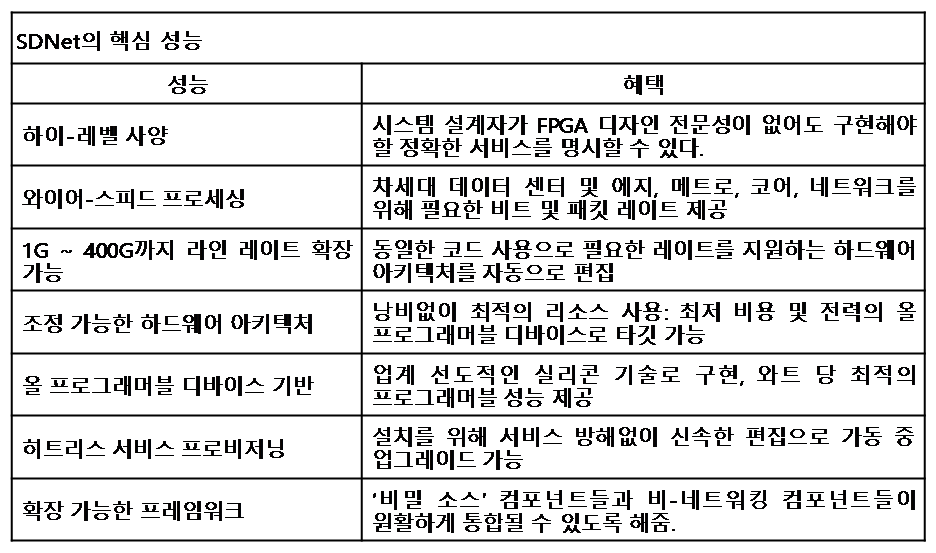

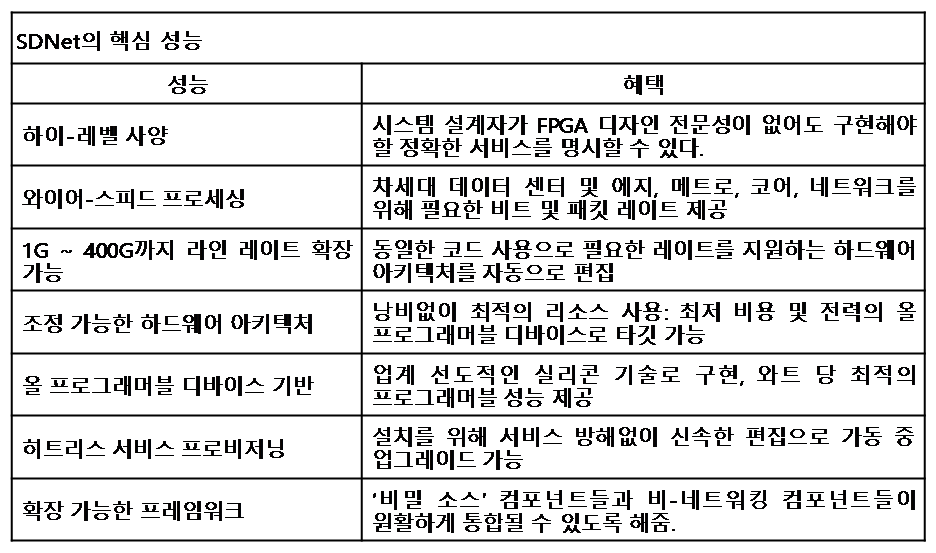

혁신적인 SDNet의 핵심 성능 및 혜택은 다음과 같다:

SDNet의 핵심 성능

SDNet을 이용한 차세대 라인 카드와 Softly Defined Networks

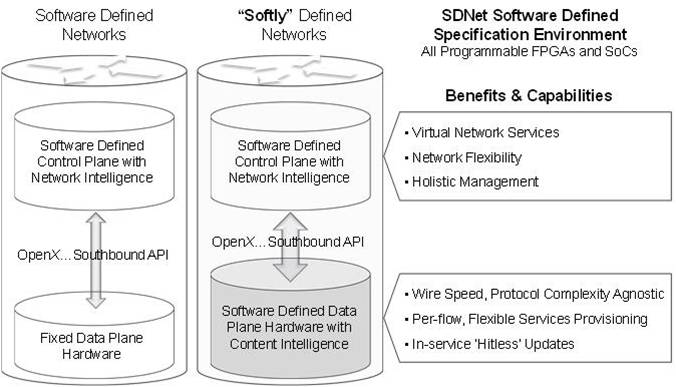

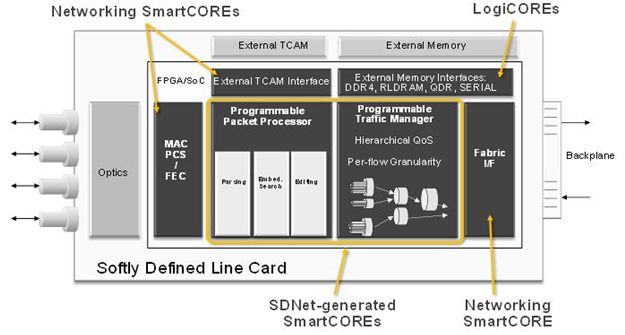

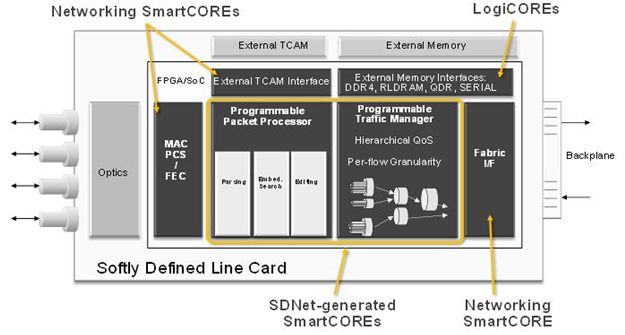

그림 2는 SDNet이 일반적인 라인 카드 상에서도 실현될 수 있는 기능의 예를 보여준다.

그림 2. SDNet 유연하게 정의된 라인 카드의 예

그림 2에 나타낸 것처럼, 광부품 및 외부 메모리를 제외하고 완전히 올 프로그래머블 디바이스 만으로 차세대 서비스를 지원하는 라인 카드를 실현할 수 있다. SDNet 사양 환경은 가능하거나 현실성있는 올 프로그래머블 라인 카드를 실제로 만들 수 있다. 위의 블록 다이어그램에서 패킷 프로세싱 및 프로그래머블 트래픽 매니저로 구성되는 커스텀 데이터 플레인은 SDNet 환경을 통해 정의할 수 있다. 또한 위에 나타낸 것처럼, MAC, PCS, FEC, 패브릭 인터페이스 코어는 자일링스의 방대한 SmartCORE 네트워킹 라이브러리에서 소싱이 가능하며, 외부 메모리 인터페이스를 비롯한 다른 기본 인터페이스 코어는 자일링스의 LogiCORE IP 라이브러리에서 이용할 수 있다.

SDNet 사양 환경의 매우 독특한 능력은 가동 중 히트리스 업데이트를 지원하는 데이터 경로 프로세싱 기능을 생성할 수 있다는 것이다. 예를 들어, 각기 다른 라인 카드 컴포넌트를 표준 SDNet API를 통한 소프트웨어 컨트롤러를 이용해 새로운 기능이나 성능으로 업데이트 할 수 있다. 업데이트 소프트웨어는 임베디드 소프트 프로세서나 외부 프로세서 상에서 구동할 수 있다. 타깃이 자일링스 징크(Zynq®) 올 프로그래머블 SoC인 경우, 소프트웨어는 디바이스의 임베디드 ARM® 프로세서에서 구동할 수 있다. 따라서 SDNet은 소프트웨어 기반 완벽한 하드웨어 프로그래머빌리티 기반의 유연하게 정의된 네트워킹으로 여분의 공간을 제공할 수 있다.

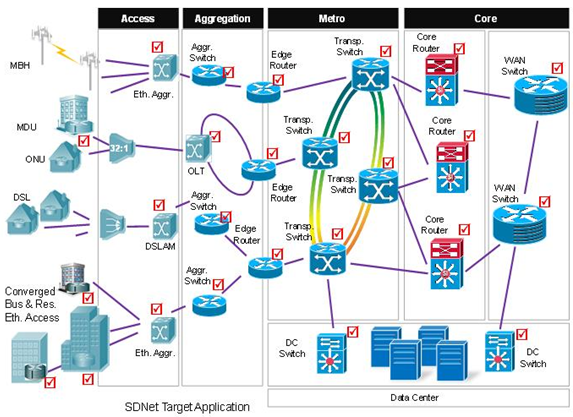

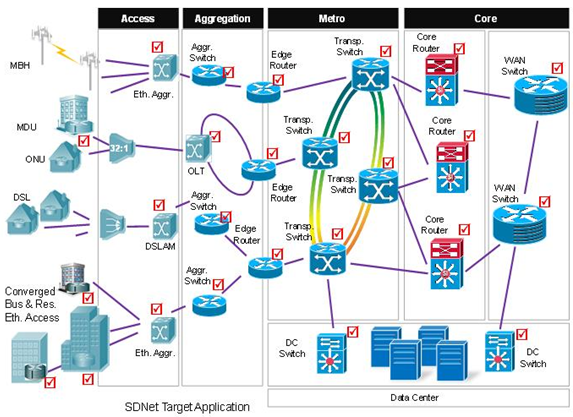

그림 3은 네트워크 내부의 각기 다른 구축 가능한 SDNet-기반 솔루션을 보여준다.

그림 3. SDNet-기반 네트워크 구축 사례

SDNet 디스크립션

컴퓨터 공학의 발전은 기계적인 수행 방법 보다는 사람의 방식대로 묘사되도록 하는 추상화의 증가를 가져온다. 잘 알려진 두 가지 사례는, 근본적인 데이터베이스 구현 방법에 대한 어떠한 세부사항 없이 데이터베이스 질문이 자연스런 방식으로 표현되는 SQL 디스크립션과 특정 기기 상에 페이지가 디스플레이되는 방식에 대한 어떠한 세부사항 없이 텍스트를 마크-업하는 것처럼 웹 페이지의 모양을 표현하는 HTML 디스크립션 등이 있다. 이러한 디스크립션은 특정 애플리케이션 분야에 커스터마이즈된 도메인에 특화된 언어로 작성된다. 이는 제한이 없는 자연언어와 표준 컴퓨터 프로그래밍 언어 간의 실질적인 절충이 가능하다.

패킷 프로세싱에서 특정 프로토콜에 대한 요건은 일반적으로 인터넷 RFC(Requests for Comment)나 ISO 표준 도큐먼트처럼 영어 디스크립션으로 표현된다. 하지만 그런 다음에는 수동으로 로우-레벨 및 특정 구현방식, 그리고 어떻게 패킷 프로세싱을 범용 프로세서나 특화된 네트워크 프로세서, 혹은 커스텀 ASIC으로 디자인된 하드웨어로 수행할 것인지에 대한 디스크립션으로 바꿔야 한다.

패킷 프로세싱은 비교적 적은 수의 특유의 기능들을 포함하고 있기 때문에, 커스텀 방식은 네트워킹 전문가들이 요구되는 패킷 프로세싱을 자연스런 방식으로 묘사할 수 있도록 해주는 좋은 방안이다. SDNet은 이러한 기능을 제공한다. 또한 SDNet은 이러한 사양을 효율적인 구현형태로 변환하고, 매핑하는 최적의 컴파일러를 제공하며, 유연하고 최적화된 하드웨어를 구현할 수 있는 적절한 FPGA 기술을 목표로 하는 사용자들에게 높은 수준의 생산성 혜택을 제공한다.

SDNet은 사용자들이 파싱, 에디팅, 검색, QoS 정책, 엔진을 비롯해 다양한 형태의 필요한 패킷 프로세싱 엔진 동작을 묘사할 수 있도록 해준다. 또한 패킷 데이터 플로우와 인터커넥트된 보다 간단한 서브 엔진과 관련해서는 계층적으로 엔진을 묘사할 수 있도록 해준다. 이러한 서브 엔진은 사용자가 제공하는 엔진을 포함할 수도 있다. SDNet 디스크립션은 세부적인 구현사항을 포함하지 않으며, 사용자들이 해당 디자인의 성능 및 전력, 리소스를 재프로그래밍할 필요없이 확장할 수 있다. 또한 SDNet은 어떠한 특정 네트워크 프로토콜에 한정되지 않는다.

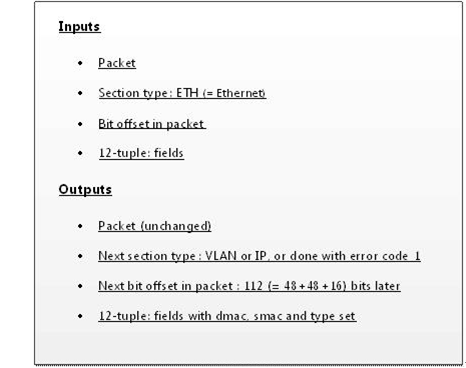

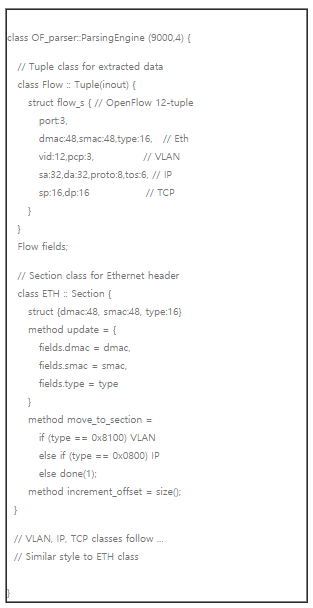

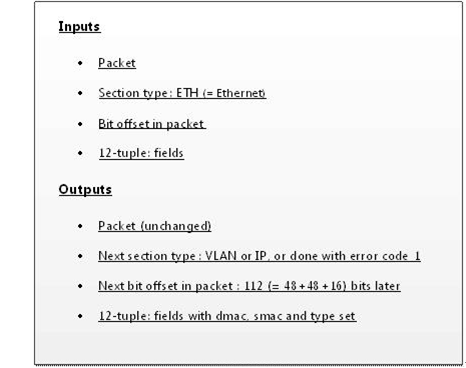

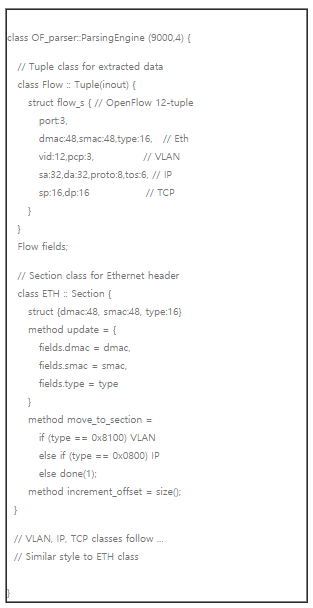

트래버싱(Traversing) 이더넷 패킷 헤더를 위한 패킷 파싱 기능의 일부 예를 그림 5에 나타낸 SDNet 디스크립션과 상응하여 그림 4에 나타냈다. 일반적인 트래버스 프로세스는 특정 형태의 섹션(헤더나 트레일러, 혹은 다른 관심 패킷의 일부)이 되도록 기대되는 패킷 내의 특정 비트 오프셋을 수반하며, 가동한 후에 다음 섹션으로 이동하거나 완료되면 중단된다. 이 사례는 특정 관심 이더넷 헤더 필드가 어떻게 12-투플(tuple)로 추출되고 배치되는지를 보여주며, 이후 연결된 검색 엔진을 이용해 분류하는데 사용할 수 있다.

완벽한 패킷 파서(Packet Parser)는 유사한 클래스들의 모음과 각 프로토콜 헤더 타입 중 하나를 포함하고 있다. 각 클래스는 헤더 포맷의 서술과 더불어, 다음 관심 헤더로 트래버스하기 위한 룰을 정의하는 방법, 즉 패킷 내부의 타입 및 오프셋을 함께 포함하고 있다. 패킷 에디팅은 패킷 트레일러나 헤더의 유사한 트래버스를 수반하며, 헤더나 트레일러의 삽입 및 제거도 포함된다.

그림 4. ETH 파싱 단계의 예

그림 5. ETH 파싱에 대한 SDNet 디스크립션 그림 6. MPLS_LSR 시스템에 대한 SDNet 디스크립션

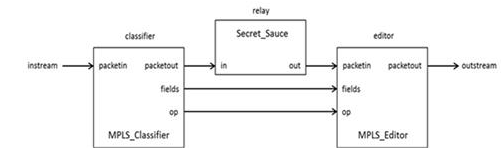

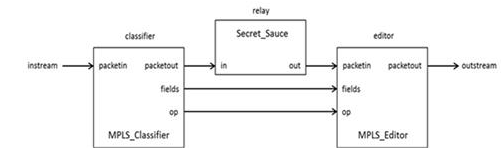

그림 7. 엔진 구성 사례: MPLS_LSP 시스템

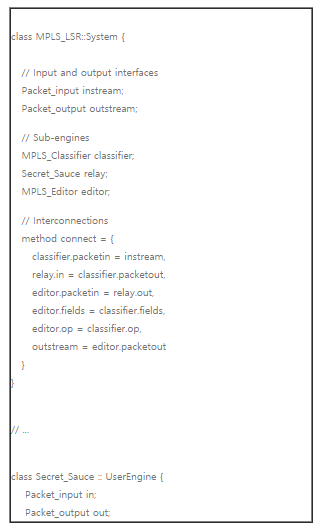

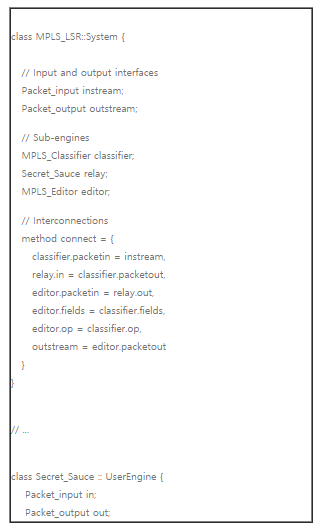

사용자는 패킷 데이터 플로우 매크로-아키텍처 내에 다양한 컴포넌트 서브-엔진을 인터커넥팅함으로써 엔진을 구성할 수 있다. 서술된 인터커넥션 패턴은 어떠한 비순환 방향성 그래프에도 순응할 수 있다. 간단한 예로, 그림 6에 나타낸 SDNet 디스크립션에 상응하는 3개의 컴포넌트 서브-엔진으로 구성한 엔진을 그림 7에 나타냈다. 또한 이 SDNet 디스크립션 단편은 사용자가 제공하는 엔진의 디스크립션도 포함하며, 이는 입력 및 출력 인터페이스로만으로 특성화된다. 이때 사용자 엔진은 패킷 분류 결과를 통해 이뤄지는 패킷 에디팅 이전에, 메인 패킷 스트림 상에서 일부 커스텀 변형을 수행하는데 사용된다. 이 사례에서, 에디터는 하나의 패킷 스트림 입력과 2개의 부가적인 데이터 투플(Tuple) 스트림 입력이다.

이 구성 방법론은 분산 검색 엔진에 대한 SDNet 접근법의 중심이다. 여기에는 SDNet에 포함된 3개 클래스의 검색 엔진이 있다.

- CAM(Content Addressable Memory): 정확한 매칭

- LPM(Longest-Prefix Match) 엔진

- TCAM(Ternary Content Addressable Memory): 와일드카드 매칭

SDNet 디스크립션에서 사용자는 키 및 결과 폭, 그리고 LUT(Lookup Table) 깊이 등 검색 엔진의 크기를 규정할 수 있으며, 그런 다음 이 엔진은 애플리케이션에서 요구될 때 전반적인 시스템 데이터 플로우 아키텍처 내에 통합된다. 따라서 전반적인 검색 성능은 특정 애플리케이션에 따라 최적화된다.

애플리케이션에 특화된 대표적인 검색엔진 모음을 이용한 사례는 다음과 같다:

- 이더넷 수신 어드레스 검색을 위한 정확한 매칭 CAM: 64K 엔트리, 48bit 폭

- 이더넷 소스 어드레스 러닝(Address Learning)을 위한 정확한 매칭 CAM: 4K 엔트리, 48bit 폭

- IPv4 수신지 어드레스 검색을 위한 LPM(Longest-Prefix Match): 64K 엔트리, 32bit 폭

- IPv6 수신지 어드레스 검색을 위한 LPM(Longest-Prefix Match): 8K 엔트리, 128bit 폭

- ACL 검색을 위한 TCAM(Ternary CAM): 4K 엔트리, 112bit 폭

이는 Ethernet/IP/TCP/UDP 패킷에 대한 포괄적인 처리가 가능할 수 있다. 각 검색 엔진은 정밀한 애플리케이션 요건에 따라 개별적으로 최적화하거나 크기를 정할 수 있으며, 관련 패킷 프로세싱 엔진과 직접 연결되어 병목현상을 피할 수 있다.

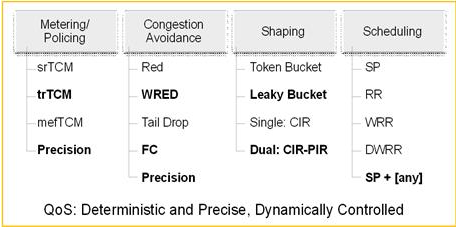

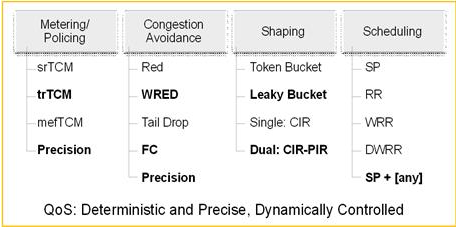

그림 8. 엔진 구성 방침의 예

인터커넥트된 정책 엔진들을 조정함으로써 유사한 구성방법을 QoS(Quality of Service)에 적용할 수 있다. 필요한 서비스 프로비저닝 즉, 계층적 플로우 수 및 레벨 수는 디자이너가 정할 수 있으며, 각 플로우에 대한 세분화된 처리방식 및 쉐이핑, 스케쥴링, 어카운팅, 정체관리, 알고리즘을 선택할 수 있다. 전반적인 QoS 정책 기능은 특정 애플리케이션에 따라 최적화되며, 플로우 유형에 따른 관련 패킷 프로세싱 및 패킷 마킹을 자동으로 생성된 컴포넌트 내에 함께 집어넣을 수 있다.

그림 8은 패킷이 다중 레벨의 QoS 계층으로 트래버스됨에 따라 플로우 당 유지될 수 있는 정책들의 조합 예를 보여준다. 처리활동 프로파일(여기서는 TRTCM(Two-Rate Three-Color Marking)을 선택한 다음, 적절한 정체 방지 조치(여기서는 계층 레벨 간의 플로우 제어를 통한 WRED(Weighted Random Early Detection))가 할당된다. 발신되어 나가는 패킷을 위한 쉐이핑 프로파일(여기서는 DLB(Dual Leaky Bucket))을 선택한 다음, 스케쥴링 관리(여기서는 SPP(Strict Priority Plus))가 적용된다.

요약하면, SDNet 사양은 사용자를 위한 본래의 짧고 간단한 디스크립션을 포함하고 있으며, 커스터마이즈된 FPGA 구현은 매우 낮은 전력소모에서 패킷 프로세싱을 보다 효율적이면서도 빠르게 만들어 준다.

사용자 지정 사양으로 생성된 SDNet 패킷 프로세싱 데이터 플레인 하드웨어는 모든 패킷 프로세싱 기능과 트래픽 통계 및 커스텀 스케치 모음으로의 히트리스 업데이트를 비롯한 제어 플레인 소프트웨어로 액세스가 가능한 폭넓은 관리 기능을 위한 스터브를 생성함으로써 보완된다. 이러한 방법으로 SDNet은 실제로 유연하게 정의된 네트워킹을 제공하며, 이는 최적화된 프로그래머블 하드웨어와 더불어 이에 수반되는 제어 소프트웨어, 하이-레벨의 독립적 구현 사양으로 모두 처리된다.

SDNet 방법론

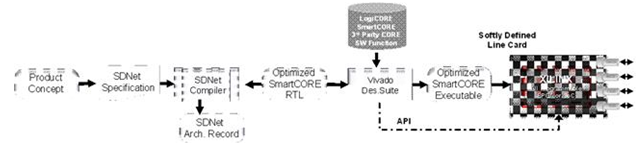

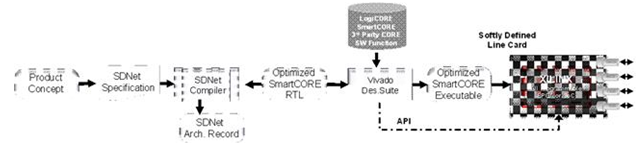

그림 9는 SDNet을 이용할 때의 전반적인 디자인 플로우를 보여준다. SDNet 디스크립션으로 시작해, 자일링스 올 프로그래머블 디바이스 컨피규레이션을 위한 비트스트림을 만들게 된다.

그림 9. SDNet 디자인 플로우

첫 번째 단계는 SDNet 컴파일러를 이용해 필요한 하드웨어 기능에 대한 RTL-레벨 디스크립션을 생성하는 것이다. 사용자는 컴파일러로 생성된 최적화된 하드웨어 아키텍처에 영향을 미치는 성능(처리량 및 지연) 요건 및 런-타임 프로그래머빌리티 요건과 관련된 부가 정보를 컴파일러에 제공한다. 또한 컴파일러는 RTL(Register-Transfer Level) 하드웨어 디스크립션과 함께 소프트웨어 제어 기능 및 디버깅, 그리고 검증 인프라를 위한 스터브를 생성한다.

두 번째 단계는 자일링스 비바도 디자인 툴을 이용하는 것이다. 이는 주요 기능을 갖추고 있는데, 첫 번째는 SDNet 컴파일러로 생성된 RTL-레벨 아키텍처 디스크립션을 최적화된 자일링스 FPGA 구현으로 변환하는 것이다. 두 번째는 완벽한 시스템을 구현하기 위해 다른 SmartCOREs 및 LogiCOREs를 이 서브시스템에 통합하고, 선택한 자일링스 올 프로그래머블 디바이스 제품군에 최적화된 최종 비트스트림을 생성하는 것이다.

시스템 통합 기능을 통해 SDNet 데이터 플레인 프로세싱 기능을 더 큰 시스템의 일부로 포함시킬 수 있으며, 다른 사용자-제공 컴포넌트, 특히 예를 들어 이더넷이나 인터라켄(Interlaken) 커넥티비티, 혹은 외부 DRAM이나 TCAM 메모리와 액세스하기 위한 SmartCORE 및 LogiCORE 인터페이스 등이 포함된다.

또한 SDNet은 여러 레벨의 디버깅 및 검증을 위한 인프라를 지원한다. SDNet 데이터 플레인 입력(혹은 SDNet 데이터 플레인 출력)을 위한 테스트 패킷 모음은 컴파일러로 생성되거나 사용자가 제공할 수 있다. 그런 다음 테스트 패킷은 3개의 각기 다른 레벨로 적용이 가능하다.

- SDNet 사양에 대한 해석

- SDNet 컴파일러로 생성된 RTL-레벨 디스크립션 시뮬레이션

- 네트워크 테스트 장비를 이용한 최종 구현 하드웨어 검증

테스트 패킷과 더불어, 검색 엔진 LUT에 상응하는 컨텐츠 또한 컴파일러로 생성되거나 사용자가 제공할 수 있다.

전반적인 SDNet 디자인 플로우의 결과는 패킷 프로세싱 요건에 대한 사용자의 하이-레벨 사양을 원활하게 수용하고, 이를 자동으로 최적화된 커스텀 SmartCORE에 매핑하는 것이다

.

SDNet의 유연성

SDNet의 핵심 가치 제안은 정확한 라인 카드 데이터 플레인 프로세싱 요건을 위한 최적화된 하드웨어를 제공하는 것이며, 이는 자일링스 올 프로그래머블 디바이스 기술을 이용함으로써 달성할 수 있다. 기본적인 디자인 플로우 상에서 물리적인 하드웨어 변경없이 새로운 비트스트림을 생성할 수 있고, 올 프로그래머블 디바이스를 재컨피규레이션함으로써 필드에서 디자인 업그레이드를 수행할 수 있다.

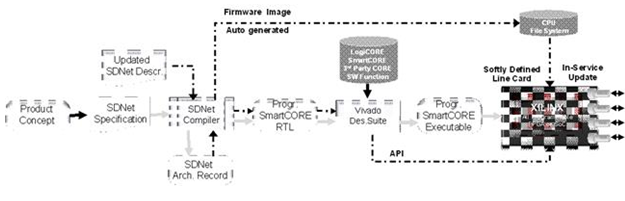

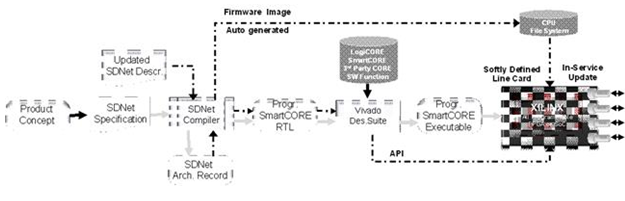

올 프로그래머블 디바이스를 재컨피규레이션할 수 있을 뿐만 아니라, SDNet은 최대 속도로 처리되는 패킷 사이에서 소프트웨어 제어를 통해 히트리스(Hitless) 업그레이드를 수행할 수 있다. 다시 말하면, 사용자는 하나의 패킷이 이전 버전의 디자인을 이용해 처리되고, 다음 패킷은 새로운 버전의 디자인을 이용해 처리될 수 있도록 신속하게 구현 및 업그레이드가 가능하다는 것이다. 그림 10은 이러한 기능을 적용한 확장된 버전의 디자인을 나타낸 것이다.

가장 중요한 부가사항은 SDNet 컴파일러는 패킷 프로세싱 데이터 플레인의 여러 세밀한 기능들을 컨피규레이션하는 펌웨어를 생성할 있다는 점이다. 펌웨어 운영 및 바이너리 인코딩은 생성된 아키텍처의 각각의 개별 컴포넌트를 위한 컴파일러로 완벽하게 커스터마이징이 가능하다. 이는 프로세싱 전반에 걸쳐 매우 긴밀하게 제어될 수 있도록 해준다. 매우 낮은 레벨의 펌웨어라 하더라도, SDNet 디스크립션에서 자동으로 생성되며, 사용자에게는 보이지 않는다.

그림 10에 나타낸 것처럼, 컴파일러는 구동 중에 SDNet 아키텍처를 기록하게 되는데, 여기에는 생성된 아키텍처 및 펌웨어의 세부사항이 저장되어 있다. 사용자가 입력을 업데이트된 SDNet 디스크립션으로 컴파일러를 재구동하는 경우, 새로운 하드웨어를 생성하지 않고 오직 펌웨어 업데이트로만 수용이 가능한지, 혹은 하드웨어(그리고 펌웨어) 재생성이 필요한지를 결정하게 된다. 대부분의 경우, 라인 카드에서 처리되는 프로토콜을 추가하거나 삭제하는 것과 같은 중간 규모의 업데이트는 펌웨어 업데이트 만으로 처리가 가능하다.

그림 10. SDNet 디자인 및 업데이트 플로우

모두 SDNet 컴파일러로 생성된 펌웨어 및 아키텍처 간의 긴밀한 연결은 사용자들이 히트리스 업그레이드를 수행할 수 있음을 의미하며, 이에 따라 펌웨어는 패킷 플로우를 방해하지 않고 서비스 중에 변경 및 배치된다. 따라서 기업들은 상당한 서비스 업그레이드를 어떠한 서비스 중단 없이도 수행할 수 있다. 이러한 혁신적인 개발은 독보적인 SDNet 기술의 특성 및 자일링스 올 프로그래머블 디바이스의 하이-레벨 사양이 결함됨으로써 달성되었다.

자일링스의 기반 기술

자일링스의 올 프로그래머블 디바이스는 1Gbit/sec에서 수 100Gbit/sec에 이르는 풀 라인 속도에서 차별화된 네트워크 프로토콜을 처리할 수 있는 완벽한 라인 카드 데이터 플레인 프로세서를 구현할 수 있다. 이러한 차원의 성능을 제공하는 FPGA는 수백 명의 사람들이 수년 간의 디자인을 통해 이룩할 수 있는 것으로, 전체론적인 접근방법으로 방대한 분야에 걸친 전문기술이 필요하고, 수많은 도전과제들을 해결해야 한다.

차세대 패킷 프로세싱과 관련된 극단적인 요건까지 서비스 할 수 있는 프로그래머블 디바이스를 설계할 때 발생되는 시스템-레벨의 문제는 상당히 엄청나다. 테라비트 데이터가 최신 SerDes 커넥티비티를 통해 멀티-기가비트 속도에서 최소한의 지연으로 FPGA로 입출력되어야 하며, 고속으로 동작하는 패킷 프로세싱 컴포넌트를 통과하기 위해 폭이 2,048bit 이상이 되는 내부 버스가 편재되어야 하고, 칩-전반의 클럭 스큐 및 지터 한도는 서브 나노세컨드 범위에 있어야 하고, 또한 모두 아주 적은 전력 한계치 만이 주어진다.

7 시리즈 올 프로그래머블 로직 디바이스와 보다 최근에 발표된 울트라스케일(UltraScale™) 제품군을 통해 자일링스는 고속 데이터 경로 프로세싱의 매우 어려운 과제들을 해결할 수 있는 업계 선도적인 다양한 첨단 기술을 현실화할 수 있게 되었다. 28nm 기반의 버텍스(Virtex®), 킨텍스(Kintex®), 아틱스(Artix®) 제품군은 28Gbit/sec를 지원하는 트랜시버, 통합 PCIe 3.0 컨트롤러, 완전 상용화된 3D IC 기반 제품을 비롯한 네트워킹에 필수적인 광범위한 기능들을 갖추고 있으며, 징크 올 프로그래머블 SoC는 ARM 코어텍스(Cortex) A9 프로세싱 서브 시스템을 통합하고 있다. 이러한 방대한 포트폴리오는 네트워크의 코어에서 에지에 이르기까지 네트워킹 장비를 위한 최적화 및 성능, 통합이 가능한 필수 실리콘 플랫폼을 제공하고 있다.

7 시리즈 제품군의 성공을 발판으로 자일링스는 차세대 네트워킹 애플리케이션의 과제를 보다 효과적으로 해결할 수 있는 향상된 울트라스케일 제품군을 출시했다. 울트라스케일은 ASIC-등급의 시스템-레벨 성능으로 전례 없는 뛰어난 통합 및 기능을 제공하는 업계 최초이자 유일한 아키텍처이다. 울트라스케일 아키텍처는 모놀리식에서 3D IC로의 확장과 더불어, 20nm 플래나 공정에서 16nm FinFET 기술을 넘어 더욱 진화하고 있다.

자일링스 비바도 디자인 수트를 통한 분석적 코-최적화를 통해, 울트라스케일 아키텍처는 방대한 라우팅 성능을 제공하면서도, 이전에는 전혀 가능하지 않았던 방법으로 전형적인 병목현상들을 효과적으로 해결할 수 있다.

차별화된 차세대 네트워킹 애플리케이션의 요구를 해결하기 위해 다음과 같은 다양한 기능과 성능들이 울트라스케일 제품군에 포함되었다:

멀티-테라비트 처리량 및 낮은 지연의 와이드 버스에 최적화된 방대한 데이터 플로우.

2세대 3D IC 시스템 통합 및 새로운 3D IC 와이드-메모리에 최적화된 인터페이스를 위한 인터-다이 대역폭의 단계 함수(Step Function).

차세대 DDR4 메모리 및 HMC(Hybrid Memory Cube) 기술 지원을 비롯한 방대한 I/O 및 메모리 대역폭.

매우 낮은 클럭 스큐와 고성능 확장성으로 저전력 클럭 네트워크를 제공하는 ASIC과 유사한 다중-영역 클럭킹.

하드와이어드된 ASIC-등급의 다중 100G 이더넷 및 150G 인터라켄, PCIe 및 기타 코어들.

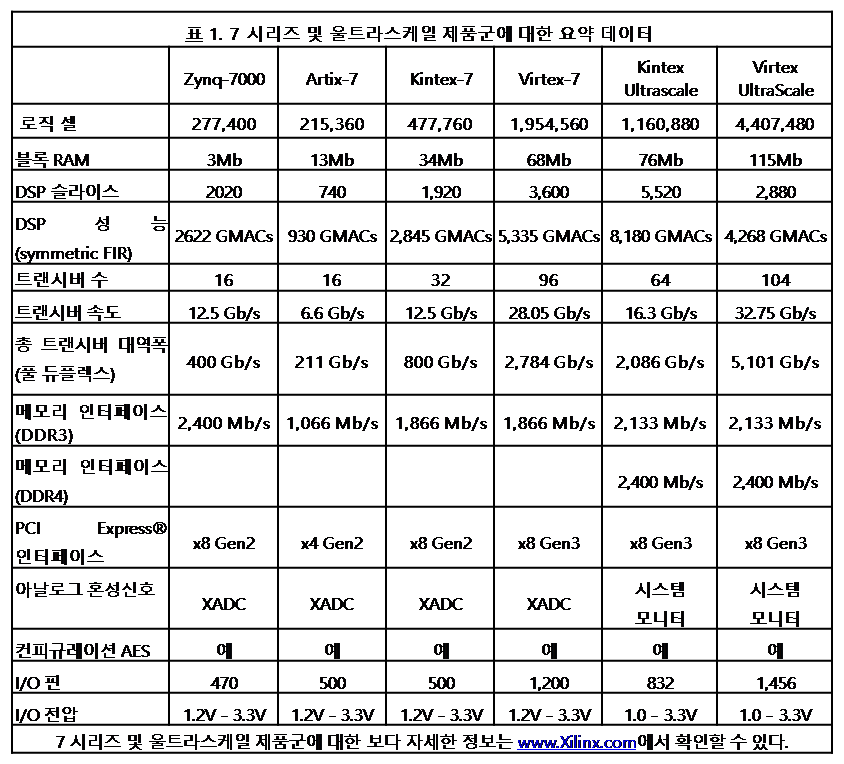

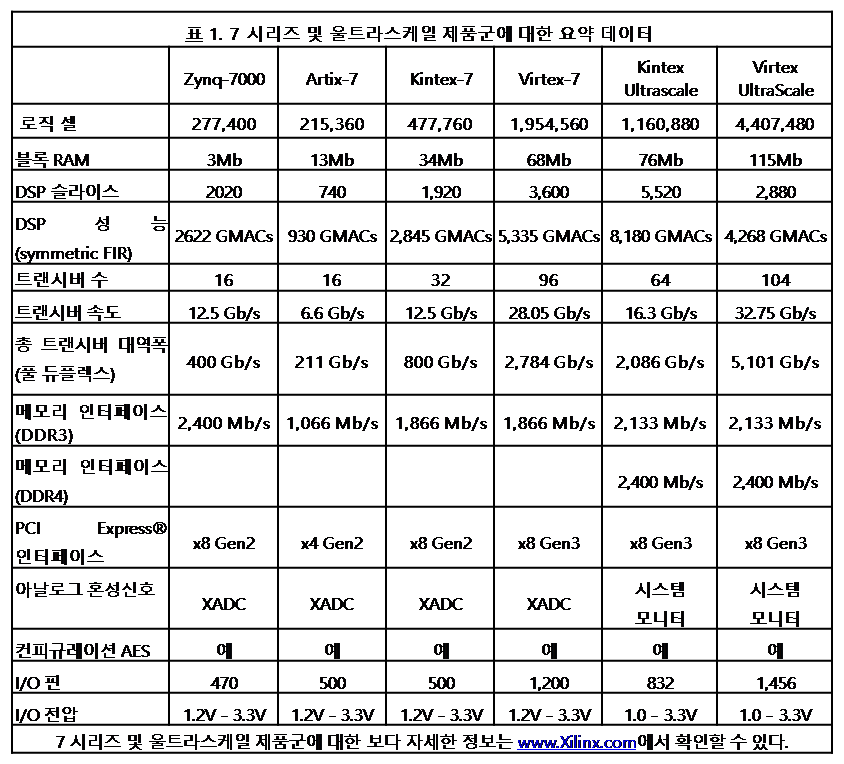

7 시리즈 및 울트라스케일 제품군에 대한 개괄적인 설명은 표 1에 정리하였다.

자일링스 SDNet 소프트웨어 환경은 기본 비바도 디자인 수트에 기반하고 있으며, 디자인 수트 및 타깃 디바이스 간의 분석적 코-최적화를 통해 올 프로그래머블 아키텍처 제품군의 모든 잠재 가능성을 실현할 수 있다. 이러한 비용 및 성능, 전력이 완벽하게 최적화된 솔루션은 특정 데이터 플레인 프로세싱 기능 세트를 실현할 수 있다. SDNet 사양이 하이-레벨이면서도 독립적인 구현형태이기 때문에 사용자는 적합한 디바이스를 위한 적절한 기능들을 자동으로 구현할 수 있다.

또한 SDNet은 비바도 IPI(IP Integrator)와의 상호 연동을 통해 혜택을 얻을 수 있으며, 대형 시스템 구축을 위한 IP 코어 통합 시간을 단축할 수 있다. 기본적인 비바도 통합 디자인 환경에 기반한 IPI는 강력한 디버깅 기능과 더불어, 디바이스 및 플랫폼을 인지할 수 있는 인터랙티브 환경으로 핵심 IP 인터페이스에 대한 인텔리전트 자동-연결 기능 및 원-클릭 IP 서브시스템 생성, 실시간 디자인 룰 체크, 인터페이스 변경 전파 등을 지원한다. IPI는 비바도 디자인 툴을 이용해 디자인 및 IP를 올바르게 컨피규레이션할 수 있으며, IPI를 통해 오류없이 디자인을 구현할 수 있다. 인터페이스 레벨에서 작업하는 디자인 팀 또한 신속하게 복잡한 시스템을 구성할 수 있다. IPI의 통합 자동화된 인터페이스 및 디바이스 드라이버, 어드레스 맵 생성 기능은 디자인 어셈블리를 보다 가속화할 수 있다.

SDNet을 이용해 구현된 서브시스템은 SmartCORE IP 코어처럼 패킹이 가능하며, 이후 이렇게 생성된 SmartCOREs를 IPI를 이용해 다른 자일링스의 SmartCOREs 및 LogiCOREs, 써드파티 얼라이언스 코어(Alliance Cores), 사용자 고유의 IP 코어와 함께 통합하여 보다 큰 시스템을 구현할 수 있다. 또한 임베디드 프로세서 코어 상에서 동작하는 소프트웨어 컴포넌트도 포함시킬 수도 있다. 따라서 SDNet의 특화된 기능을 다른 프로세싱 도메인에 특화된 전력 툴과 함께 사용할 수 있다.

다른 접근법과의 비교

그림 11은 필요한 최고 속도의 데이터 경로 프로세싱을 제공하는 다른 대안적 접근방식의 특성과 비교한 SDNet의 일부 주요 기능을 보여주고 있다.

그림 11. 다른 대안적 방법과 비교한 SDNet의 주요 특징들

맨 하단은 사전 고정형 기술 부분에서 사용하지 않은 리소스가 낭비되지 않도록 SDNet이 리소스를 최적화하여 구현한 것이다. 또한 고정형 아키텍처 기술을 넘어 패킷 플로우 아키텍처 매칭으로 설계를 최적화하여 구현할 수 있도록 해준다. 더불어 동일한 SDNet 패킷 프로세싱 사양을 성능 요건을 늘리거나 줄이는 경우에도 사용할 수 있다.

처음부터 SDNet으로 구현하는 특성화 작업은 네트워크 및 네트워크 기능의 가상화, 그리고 이러한 네트워크의 소프트웨어 정의가 보다 더 중요한 시기에는 더욱 필수적이다. 이는 필요한 성능을 제공하는 하드웨어는 물론, 빠르게 변화하는 기능 및 프로비저닝, 프로토콜, 표준에 대응할 수 있는 유연성도 제공한다. 따라서 SDNet은 독자적으로 완벽한 차세대 기술이 될 수 있다.

요약

자일링스의 SDNet 사양 환경은 SDN 및 Softly Defined Networks 모두를 아우르는 새롭고 혁신적인 제품을 효율적으로 현실화하는 네트워킹 시스템 설계의 새로운 가능성을 제시하는 획기적인 기술이다. SDNet은 매우 높은 라인 레이트로 데이터를 수신 및 전송할 수 있는 자일링스의 방대한 올 프로그래머블 디바이스의 성능을 통해 탁월한 혜택을 얻을 수 있으며, 모든 레벨의 네트워크에서 요구되는 라인 카드 데이터 플레인 프로세싱 기능을 수행할 수 있다. SDNet의 혁신은 가공되지 않은 실리콘 기능을 어떻게 구현할 것인가 보다는 필요한 사양을 현실화해 주는 최상의 하이-레벨 디자인 방법론을 통해 보다 많은 사용자들이 손쉽게 이용할 수 있도록 해주는 것이다. 이러한 방법론은 새로운 시스템 컴포넌트를 위한 스마트 편집기능 및 표준 네트워킹 기능을 위한 최적화된 SmartCOREs 라이브러리를 모두 통합하고 있다. 히트리스 현장 업그레이드 수행능력 및 네트워크 인텔리전스 기반 소프트웨어 정의 제어 플레인, 그리고 콘텐트 인텔리전스 기반 소프트웨어 정의 데이터 플레인 기능을 모두 겸비하고 있는 SDNet은 위험요소를 줄이고, 마켓 출시시기를 단축할 수 있으며, 가용성 및 확장 가능성이 향상된다. 다시 말해, SDNet은 업계의 SDN 흐름에 대응할 수 있는 핵심 열쇠이며, 네트워킹 시스템 디자이너 및 설계자들의 생산성 또한 높일 수 있다.

SDNet에 대한 보다 자세한 정보는 자일링스 웹사이트(www.xilinx.com)나 한국지사를 통해 얻을 수 있다.

개요

수년 간의 연구작업과 방대한 투자가 정점에 이르면서, 자일링스(Xilinx)는 드디어 새로운 SDNet(Software Defined Specification Environment for Networking)을 공개했다. SDNet은 하이 레벨 사용자 지정 사양을 고도로 최적화된 올 프로그래머블(All Programmable) FPGA 및 SoC에 합성하는 방식으로 고성능 패킷 프로세싱 시스템을 손쉽게 구현할 수 있도록 해준다. 보다 구체적으로 말하면, 자일링스의 올 프로그래머블 디바이스와 함께 SDNet은 기술적 과도기에 Softly Defined Network을 구현할 수 있다는 것이다. Softly Defined Network은 SDN(Software Defined Network) 객체를 지원할 뿐만 아니라, 콘텐트 인텔리전스(Content Intelligence)를 갖춘 소프트웨어로 정의된 데이터 플레인 하드웨어를 지원함으로써 새로운 변화에 대응할 수 있다.

이 글은 SDNet의 다양한 기능을 이해하고자 하는 네트워킹 시스템 설계자 및 엔지니어링 매니저들이 까다로운 기술적인 문제들을 해결하고, 궁극적으로 올 프로그래머블 및 보다 스마트한 Softly Defined Networks을 구축하는데 어떻게 적용할 것인지를 결정하는데 도움을 주고자 작성되었다. 이 글과 더불어, SDNet의 특정 기능을 다루고 있는 다른 컨설팅 자료를 통해서도 관심영역을 보다 더 깊이 이해할 수 있기를 바란다.

Softly Defined Network의 필요성

지속적으로 진화하고 있는 사용자들의 요구를 해결하기 위해, 네트워크 시스템 벤더들은 개발 사이클을 수년에서 수개월로 줄이는 것은 물론, SDN을 비롯한 새로운 네트워킹 토폴로지를 반드시 지원해야 한다. 이는 빠른 표준의 발전과 새로운 커넥티비티 옵션, 그리고 처리량 및 인터페이스 옵션, 사이즈가 각기 다른 다중 라인 카드에 걸쳐 동적으로 혹은 통일된 방식으로 확장이 가능해야 하는 OTT(Over-The-Top) 서비스의 등장으로 인해 더욱 가속화되고 있다. 이와 동시에 통신 사업자들은 프로비저닝 및 매니지먼트, 자본지출 등을 간소화하기 위해 SDN 및 NFV와 같은 새로운 네트워크 아키텍처에 대해서도 검토하고 있다. 이상적인 솔루션은 소프트웨어로 제어할 수 있고, 커스텀 하드웨어 구현으로 새로운 기능을 수용할 수 있는 유입에서 유출까지 완벽한 프로그래머블 및 확장 가능한 라인 카드이다.

지나치게 증가하고 있는 개발 비용과 늘어나는 개발 주기, 그리고 근본적인 유연성 부족 등은 장비 공급업체들이 기존 제품에서 차세대 ASIC으로의 마이그레이션을 저해한다. 성공적인 ASIC 프로젝트라 하더라도 부가적인 ‘미래 지향적(Future-Proofing)’인 리소스들은 계속 축적되기 때문에 비용, 크기, 전력, 오버헤드는 반드시 추가되기 마련이다. 전체적으로 매우 소수의 시스템 벤더들이 내부 데이터 플레인 ASIC을 50~100Gbit/sec 데이터 레이트 이상으로 확장하고자 시도하고 있다. 한편 서로 전혀 다른 새로운 애플리케이션 요건들과 데이터 레이트는 ASSP 벤더들에게도 이와 유사한 방식으로 영향을 미치고 있기 때문에 상용 실리콘 공급에서도 갭이 유발되고 있다. 간단하게 말해서, 고정형 실리콘 솔루션 비즈니스는 빠르게 자취를 감추고 있다.

ASIC 및 ASSP 벤더들이 네트워킹 분야의 문제들을 해결하고자 노력하고 있는 반면, IT 산업은 기존의 경계를 허물고 더욱 새롭게 진화하고 있다. 새롭게 부상하는 경향 중 하나는 IT 설계자들이 고정된 기능의 ASIC이나 보다 유연한 상용 NPU 기반의 라인 카드의 가치에 의문을 제기하면서 소프트웨어로 제어가 가능한 일련의 동적인 가상 서비스로 진화할 수 있는 하드웨어를 추구하고 있다는 것이다. 하지만 고도의 기능들을 소프트웨어로 처리하고, 간단한 스위칭 하드웨어에만 기반한 솔루션은 성능 요건을 달성할 수 없으며, 컨텍스트도 매우 제한적일 수밖에 없다.

올 프로그래머블 FPGA 및 SoC는 소프트웨어로 프로그램이 가능한 고도로 유연한 하드웨어에 대한 요구를 해결할 수 있는 가능성을 가지고 있다. 유입에서 유출까지 거의 모든 라인 카드의 기능은 최신 올 프로그래머블 디바이스를 이용한 프로그래머블 기술을 통해 구현이 가능하며, 차세대 네트워크 플랫폼과 관련된 필요한 최대 속도와 패킷 프로세싱 레이트를 지원할 수 있다.

자일링스는 차세대 프로그래머블 네트워킹 플랫폼을 유연하게 구현 가능한 네트워킹, 즉 Softly Defined Networking 디바이스로 명명했으며, SDN은 물론, 그 이후의 기능까지 해결할 수 있는 성능 및 소프트웨어, 하드웨어 측면의 모든 올 프로그래머블의 특성을 강조하고 있다.

그림 1. SDN(Softly Defined Networking)으로의 진화

그림 1은 네트워크 디바이스(스위치, 라우터, 관련 기기들)의 발전을 보여주고 있다. 첫 번째 단계는 개방형의 유연한 소프트웨어 컨트롤을 통해 소프트웨어로 정의된 네트워킹으로 나아가고 있는 광범위한 흐름을 보여주고 있지만, 하드웨어는 폐쇄형의 단순한 고정형이다. 두 번째 단계는 더 나아가 최신 차동 콘텐트-지향적 네트워킹의 성능 및 과제를 해결하기 위해 개방형의 유연하고 복잡한 하드웨어 데이터 플레인을 갖춘 자일링스의 유연하게 정의된 네트워킹, 즉 Softly Defined Networking으로 진화되는 것을 볼 수 있다. 소프트웨어로 정의된 네트워킹의 제한된 Southbound API가 훨씬 풍부해지면서 상당한 규모의 고속 데이터 플레인 리프로그래밍을 지원하고, 데이터 플레인에서 프로그램된 트래픽 분석을 회수할 수 있다. 소프트웨어 정의된 데이터 플레인 하드웨어에서 얻을 수 있는 부가적인 장점은 상당하며, 여기에는 WSPA(Wire-Speed Protocol-Agnostic) 지원, 고도로 유연한 향상된 QoS(Quality of Service), 플로우 및 세션 인식 기능 등이 있으며, 이외에도 네트워크 가상화, NFV(Network Functions Virtualization), 사용자 정의 및 커스텀 기능을 지원한다.

혁신적인 자일링스의 SDNet 사양 환경은 유연하게 정의된 네트워킹, 즉 Softly Defined Networking으로 이행할 수 있도록 해주며, 자일링스 올 프로그래머블 디바이스 상에 패킷 프로세싱 기능을 빠르게 프로토타이핑 및 개발, 구축할 수 있도록 해준다. 패킷 프로세싱 요건의 자동 매핑 기능으로 최적의 프로그래머블 하드웨어를 구현할 수 있는 하이-레벨 기능 사양의 도입 방법은 업계 및 기술 판도를 변화시키고 있다.

SDNet 사양 환경의 개요

SDNet 환경의 기반은 일련의 통합 개발 툴로 처리되는 하이-레벨 네트워킹 사양을 사용하는 것이다. 이는 사용자들이 어떠한 세부 구현법을 사용하지 않고도 필요한 패킷 프로세싱 기능을 원래의 방법대로 서술하는 것이 가능하다. 그런 다음, 이 사양은 최적의 비용과 전력, 성능에서 최대 속도를 제공하는 자일링스의 올 프로그래머블 디바이스 상에 최적의 하드웨어 구현 형태로 자동 전환된다. 이것이 바로 유연하게 정의된 네트워킹, Softly Defined Networking에 이르는 방법이다.

SDNet 통합 개발 환경의 주요 컴포넌트는 다음과 같다:

특정 기능을 위한 커스텀 하드웨어 컴포넌트 생성(예, 파싱(Parsing), 에디팅)

사용자 요건에 부합하는 커스텀 패킷 데이터 플레인 하드웨어 서브 시스템 생성

생성된 SDNet 하드웨어 아키텍처를 위한 커스텀 펌웨어 생성

디버깅 및 검증을 위한 테스트 벤치 생성

SDNet 환경에서 생성되는 패킷 프로세싱 아키텍처는 히트리스(Hitless) 업데이트를 지원하는데, 라인-레이트 서비스를 전혀 방해하지 않고 패킷 간에 데이터 플레인 프로세싱 기능이 변경될 수 있다. 이러한 가동 중의 변경은 커스텀 펌웨어 업데이트를 통해 가능하며, 또한 사용자들이 만든 SDNet 사양 변경을 통해서도 생성된다.

SDNet은 자일링스의 최적화된 네트워킹을 위한 SmartCOREs™와 커넥비티 및 외부 메모리 제어, 임베디드 프로세서를 위한 LogiCOREs™를 통합할 수 있다. 이는 업계 선도적인 자일링스의 비바도(Vivado®) 디자인 환경과 SDNet이 결합됨으로써 달성할 수 있다.

SDNet 환경은 확장이 가능하기 때문에 사용자가 제공한 컴포넌트를 통합할 수 있다:

긴밀한 하드웨어 통합: 사용자 엔진을 SDNet에 도입

외부 하드웨어 통합: 사용자 IP 블록을 완성된 SDNet 하드웨어 블록과 연결

소프트웨어 통합: 사용자 소프트웨어를 SDNet 매니지먼트 API와 연결

혁신적인 SDNet의 핵심 성능 및 혜택은 다음과 같다:

SDNet의 핵심 성능

SDNet을 이용한 차세대 라인 카드와 Softly Defined Networks

그림 2는 SDNet이 일반적인 라인 카드 상에서도 실현될 수 있는 기능의 예를 보여준다.

그림 2. SDNet 유연하게 정의된 라인 카드의 예

그림 2에 나타낸 것처럼, 광부품 및 외부 메모리를 제외하고 완전히 올 프로그래머블 디바이스 만으로 차세대 서비스를 지원하는 라인 카드를 실현할 수 있다. SDNet 사양 환경은 가능하거나 현실성있는 올 프로그래머블 라인 카드를 실제로 만들 수 있다. 위의 블록 다이어그램에서 패킷 프로세싱 및 프로그래머블 트래픽 매니저로 구성되는 커스텀 데이터 플레인은 SDNet 환경을 통해 정의할 수 있다. 또한 위에 나타낸 것처럼, MAC, PCS, FEC, 패브릭 인터페이스 코어는 자일링스의 방대한 SmartCORE 네트워킹 라이브러리에서 소싱이 가능하며, 외부 메모리 인터페이스를 비롯한 다른 기본 인터페이스 코어는 자일링스의 LogiCORE IP 라이브러리에서 이용할 수 있다.

SDNet 사양 환경의 매우 독특한 능력은 가동 중 히트리스 업데이트를 지원하는 데이터 경로 프로세싱 기능을 생성할 수 있다는 것이다. 예를 들어, 각기 다른 라인 카드 컴포넌트를 표준 SDNet API를 통한 소프트웨어 컨트롤러를 이용해 새로운 기능이나 성능으로 업데이트 할 수 있다. 업데이트 소프트웨어는 임베디드 소프트 프로세서나 외부 프로세서 상에서 구동할 수 있다. 타깃이 자일링스 징크(Zynq®) 올 프로그래머블 SoC인 경우, 소프트웨어는 디바이스의 임베디드 ARM® 프로세서에서 구동할 수 있다. 따라서 SDNet은 소프트웨어 기반 완벽한 하드웨어 프로그래머빌리티 기반의 유연하게 정의된 네트워킹으로 여분의 공간을 제공할 수 있다.

그림 3은 네트워크 내부의 각기 다른 구축 가능한 SDNet-기반 솔루션을 보여준다.

그림 3. SDNet-기반 네트워크 구축 사례

SDNet 디스크립션

컴퓨터 공학의 발전은 기계적인 수행 방법 보다는 사람의 방식대로 묘사되도록 하는 추상화의 증가를 가져온다. 잘 알려진 두 가지 사례는, 근본적인 데이터베이스 구현 방법에 대한 어떠한 세부사항 없이 데이터베이스 질문이 자연스런 방식으로 표현되는 SQL 디스크립션과 특정 기기 상에 페이지가 디스플레이되는 방식에 대한 어떠한 세부사항 없이 텍스트를 마크-업하는 것처럼 웹 페이지의 모양을 표현하는 HTML 디스크립션 등이 있다. 이러한 디스크립션은 특정 애플리케이션 분야에 커스터마이즈된 도메인에 특화된 언어로 작성된다. 이는 제한이 없는 자연언어와 표준 컴퓨터 프로그래밍 언어 간의 실질적인 절충이 가능하다.

패킷 프로세싱에서 특정 프로토콜에 대한 요건은 일반적으로 인터넷 RFC(Requests for Comment)나 ISO 표준 도큐먼트처럼 영어 디스크립션으로 표현된다. 하지만 그런 다음에는 수동으로 로우-레벨 및 특정 구현방식, 그리고 어떻게 패킷 프로세싱을 범용 프로세서나 특화된 네트워크 프로세서, 혹은 커스텀 ASIC으로 디자인된 하드웨어로 수행할 것인지에 대한 디스크립션으로 바꿔야 한다.

패킷 프로세싱은 비교적 적은 수의 특유의 기능들을 포함하고 있기 때문에, 커스텀 방식은 네트워킹 전문가들이 요구되는 패킷 프로세싱을 자연스런 방식으로 묘사할 수 있도록 해주는 좋은 방안이다. SDNet은 이러한 기능을 제공한다. 또한 SDNet은 이러한 사양을 효율적인 구현형태로 변환하고, 매핑하는 최적의 컴파일러를 제공하며, 유연하고 최적화된 하드웨어를 구현할 수 있는 적절한 FPGA 기술을 목표로 하는 사용자들에게 높은 수준의 생산성 혜택을 제공한다.

SDNet은 사용자들이 파싱, 에디팅, 검색, QoS 정책, 엔진을 비롯해 다양한 형태의 필요한 패킷 프로세싱 엔진 동작을 묘사할 수 있도록 해준다. 또한 패킷 데이터 플로우와 인터커넥트된 보다 간단한 서브 엔진과 관련해서는 계층적으로 엔진을 묘사할 수 있도록 해준다. 이러한 서브 엔진은 사용자가 제공하는 엔진을 포함할 수도 있다. SDNet 디스크립션은 세부적인 구현사항을 포함하지 않으며, 사용자들이 해당 디자인의 성능 및 전력, 리소스를 재프로그래밍할 필요없이 확장할 수 있다. 또한 SDNet은 어떠한 특정 네트워크 프로토콜에 한정되지 않는다.

트래버싱(Traversing) 이더넷 패킷 헤더를 위한 패킷 파싱 기능의 일부 예를 그림 5에 나타낸 SDNet 디스크립션과 상응하여 그림 4에 나타냈다. 일반적인 트래버스 프로세스는 특정 형태의 섹션(헤더나 트레일러, 혹은 다른 관심 패킷의 일부)이 되도록 기대되는 패킷 내의 특정 비트 오프셋을 수반하며, 가동한 후에 다음 섹션으로 이동하거나 완료되면 중단된다. 이 사례는 특정 관심 이더넷 헤더 필드가 어떻게 12-투플(tuple)로 추출되고 배치되는지를 보여주며, 이후 연결된 검색 엔진을 이용해 분류하는데 사용할 수 있다.

완벽한 패킷 파서(Packet Parser)는 유사한 클래스들의 모음과 각 프로토콜 헤더 타입 중 하나를 포함하고 있다. 각 클래스는 헤더 포맷의 서술과 더불어, 다음 관심 헤더로 트래버스하기 위한 룰을 정의하는 방법, 즉 패킷 내부의 타입 및 오프셋을 함께 포함하고 있다. 패킷 에디팅은 패킷 트레일러나 헤더의 유사한 트래버스를 수반하며, 헤더나 트레일러의 삽입 및 제거도 포함된다.

그림 4. ETH 파싱 단계의 예

그림 5. ETH 파싱에 대한 SDNet 디스크립션 그림 6. MPLS_LSR 시스템에 대한 SDNet 디스크립션

그림 7. 엔진 구성 사례: MPLS_LSP 시스템

사용자는 패킷 데이터 플로우 매크로-아키텍처 내에 다양한 컴포넌트 서브-엔진을 인터커넥팅함으로써 엔진을 구성할 수 있다. 서술된 인터커넥션 패턴은 어떠한 비순환 방향성 그래프에도 순응할 수 있다. 간단한 예로, 그림 6에 나타낸 SDNet 디스크립션에 상응하는 3개의 컴포넌트 서브-엔진으로 구성한 엔진을 그림 7에 나타냈다. 또한 이 SDNet 디스크립션 단편은 사용자가 제공하는 엔진의 디스크립션도 포함하며, 이는 입력 및 출력 인터페이스로만으로 특성화된다. 이때 사용자 엔진은 패킷 분류 결과를 통해 이뤄지는 패킷 에디팅 이전에, 메인 패킷 스트림 상에서 일부 커스텀 변형을 수행하는데 사용된다. 이 사례에서, 에디터는 하나의 패킷 스트림 입력과 2개의 부가적인 데이터 투플(Tuple) 스트림 입력이다.

이 구성 방법론은 분산 검색 엔진에 대한 SDNet 접근법의 중심이다. 여기에는 SDNet에 포함된 3개 클래스의 검색 엔진이 있다.

- CAM(Content Addressable Memory): 정확한 매칭

- LPM(Longest-Prefix Match) 엔진

- TCAM(Ternary Content Addressable Memory): 와일드카드 매칭

SDNet 디스크립션에서 사용자는 키 및 결과 폭, 그리고 LUT(Lookup Table) 깊이 등 검색 엔진의 크기를 규정할 수 있으며, 그런 다음 이 엔진은 애플리케이션에서 요구될 때 전반적인 시스템 데이터 플로우 아키텍처 내에 통합된다. 따라서 전반적인 검색 성능은 특정 애플리케이션에 따라 최적화된다.

애플리케이션에 특화된 대표적인 검색엔진 모음을 이용한 사례는 다음과 같다:

- 이더넷 수신 어드레스 검색을 위한 정확한 매칭 CAM: 64K 엔트리, 48bit 폭

- 이더넷 소스 어드레스 러닝(Address Learning)을 위한 정확한 매칭 CAM: 4K 엔트리, 48bit 폭

- IPv4 수신지 어드레스 검색을 위한 LPM(Longest-Prefix Match): 64K 엔트리, 32bit 폭

- IPv6 수신지 어드레스 검색을 위한 LPM(Longest-Prefix Match): 8K 엔트리, 128bit 폭

- ACL 검색을 위한 TCAM(Ternary CAM): 4K 엔트리, 112bit 폭

이는 Ethernet/IP/TCP/UDP 패킷에 대한 포괄적인 처리가 가능할 수 있다. 각 검색 엔진은 정밀한 애플리케이션 요건에 따라 개별적으로 최적화하거나 크기를 정할 수 있으며, 관련 패킷 프로세싱 엔진과 직접 연결되어 병목현상을 피할 수 있다.

그림 8. 엔진 구성 방침의 예

인터커넥트된 정책 엔진들을 조정함으로써 유사한 구성방법을 QoS(Quality of Service)에 적용할 수 있다. 필요한 서비스 프로비저닝 즉, 계층적 플로우 수 및 레벨 수는 디자이너가 정할 수 있으며, 각 플로우에 대한 세분화된 처리방식 및 쉐이핑, 스케쥴링, 어카운팅, 정체관리, 알고리즘을 선택할 수 있다. 전반적인 QoS 정책 기능은 특정 애플리케이션에 따라 최적화되며, 플로우 유형에 따른 관련 패킷 프로세싱 및 패킷 마킹을 자동으로 생성된 컴포넌트 내에 함께 집어넣을 수 있다.

그림 8은 패킷이 다중 레벨의 QoS 계층으로 트래버스됨에 따라 플로우 당 유지될 수 있는 정책들의 조합 예를 보여준다. 처리활동 프로파일(여기서는 TRTCM(Two-Rate Three-Color Marking)을 선택한 다음, 적절한 정체 방지 조치(여기서는 계층 레벨 간의 플로우 제어를 통한 WRED(Weighted Random Early Detection))가 할당된다. 발신되어 나가는 패킷을 위한 쉐이핑 프로파일(여기서는 DLB(Dual Leaky Bucket))을 선택한 다음, 스케쥴링 관리(여기서는 SPP(Strict Priority Plus))가 적용된다.

요약하면, SDNet 사양은 사용자를 위한 본래의 짧고 간단한 디스크립션을 포함하고 있으며, 커스터마이즈된 FPGA 구현은 매우 낮은 전력소모에서 패킷 프로세싱을 보다 효율적이면서도 빠르게 만들어 준다.

사용자 지정 사양으로 생성된 SDNet 패킷 프로세싱 데이터 플레인 하드웨어는 모든 패킷 프로세싱 기능과 트래픽 통계 및 커스텀 스케치 모음으로의 히트리스 업데이트를 비롯한 제어 플레인 소프트웨어로 액세스가 가능한 폭넓은 관리 기능을 위한 스터브를 생성함으로써 보완된다. 이러한 방법으로 SDNet은 실제로 유연하게 정의된 네트워킹을 제공하며, 이는 최적화된 프로그래머블 하드웨어와 더불어 이에 수반되는 제어 소프트웨어, 하이-레벨의 독립적 구현 사양으로 모두 처리된다.

SDNet 방법론

그림 9는 SDNet을 이용할 때의 전반적인 디자인 플로우를 보여준다. SDNet 디스크립션으로 시작해, 자일링스 올 프로그래머블 디바이스 컨피규레이션을 위한 비트스트림을 만들게 된다.

그림 9. SDNet 디자인 플로우

첫 번째 단계는 SDNet 컴파일러를 이용해 필요한 하드웨어 기능에 대한 RTL-레벨 디스크립션을 생성하는 것이다. 사용자는 컴파일러로 생성된 최적화된 하드웨어 아키텍처에 영향을 미치는 성능(처리량 및 지연) 요건 및 런-타임 프로그래머빌리티 요건과 관련된 부가 정보를 컴파일러에 제공한다. 또한 컴파일러는 RTL(Register-Transfer Level) 하드웨어 디스크립션과 함께 소프트웨어 제어 기능 및 디버깅, 그리고 검증 인프라를 위한 스터브를 생성한다.

두 번째 단계는 자일링스 비바도 디자인 툴을 이용하는 것이다. 이는 주요 기능을 갖추고 있는데, 첫 번째는 SDNet 컴파일러로 생성된 RTL-레벨 아키텍처 디스크립션을 최적화된 자일링스 FPGA 구현으로 변환하는 것이다. 두 번째는 완벽한 시스템을 구현하기 위해 다른 SmartCOREs 및 LogiCOREs를 이 서브시스템에 통합하고, 선택한 자일링스 올 프로그래머블 디바이스 제품군에 최적화된 최종 비트스트림을 생성하는 것이다.

시스템 통합 기능을 통해 SDNet 데이터 플레인 프로세싱 기능을 더 큰 시스템의 일부로 포함시킬 수 있으며, 다른 사용자-제공 컴포넌트, 특히 예를 들어 이더넷이나 인터라켄(Interlaken) 커넥티비티, 혹은 외부 DRAM이나 TCAM 메모리와 액세스하기 위한 SmartCORE 및 LogiCORE 인터페이스 등이 포함된다.

또한 SDNet은 여러 레벨의 디버깅 및 검증을 위한 인프라를 지원한다. SDNet 데이터 플레인 입력(혹은 SDNet 데이터 플레인 출력)을 위한 테스트 패킷 모음은 컴파일러로 생성되거나 사용자가 제공할 수 있다. 그런 다음 테스트 패킷은 3개의 각기 다른 레벨로 적용이 가능하다.

- SDNet 사양에 대한 해석

- SDNet 컴파일러로 생성된 RTL-레벨 디스크립션 시뮬레이션

- 네트워크 테스트 장비를 이용한 최종 구현 하드웨어 검증

테스트 패킷과 더불어, 검색 엔진 LUT에 상응하는 컨텐츠 또한 컴파일러로 생성되거나 사용자가 제공할 수 있다.

전반적인 SDNet 디자인 플로우의 결과는 패킷 프로세싱 요건에 대한 사용자의 하이-레벨 사양을 원활하게 수용하고, 이를 자동으로 최적화된 커스텀 SmartCORE에 매핑하는 것이다

.

SDNet의 유연성

SDNet의 핵심 가치 제안은 정확한 라인 카드 데이터 플레인 프로세싱 요건을 위한 최적화된 하드웨어를 제공하는 것이며, 이는 자일링스 올 프로그래머블 디바이스 기술을 이용함으로써 달성할 수 있다. 기본적인 디자인 플로우 상에서 물리적인 하드웨어 변경없이 새로운 비트스트림을 생성할 수 있고, 올 프로그래머블 디바이스를 재컨피규레이션함으로써 필드에서 디자인 업그레이드를 수행할 수 있다.

올 프로그래머블 디바이스를 재컨피규레이션할 수 있을 뿐만 아니라, SDNet은 최대 속도로 처리되는 패킷 사이에서 소프트웨어 제어를 통해 히트리스(Hitless) 업그레이드를 수행할 수 있다. 다시 말하면, 사용자는 하나의 패킷이 이전 버전의 디자인을 이용해 처리되고, 다음 패킷은 새로운 버전의 디자인을 이용해 처리될 수 있도록 신속하게 구현 및 업그레이드가 가능하다는 것이다. 그림 10은 이러한 기능을 적용한 확장된 버전의 디자인을 나타낸 것이다.

가장 중요한 부가사항은 SDNet 컴파일러는 패킷 프로세싱 데이터 플레인의 여러 세밀한 기능들을 컨피규레이션하는 펌웨어를 생성할 있다는 점이다. 펌웨어 운영 및 바이너리 인코딩은 생성된 아키텍처의 각각의 개별 컴포넌트를 위한 컴파일러로 완벽하게 커스터마이징이 가능하다. 이는 프로세싱 전반에 걸쳐 매우 긴밀하게 제어될 수 있도록 해준다. 매우 낮은 레벨의 펌웨어라 하더라도, SDNet 디스크립션에서 자동으로 생성되며, 사용자에게는 보이지 않는다.

그림 10에 나타낸 것처럼, 컴파일러는 구동 중에 SDNet 아키텍처를 기록하게 되는데, 여기에는 생성된 아키텍처 및 펌웨어의 세부사항이 저장되어 있다. 사용자가 입력을 업데이트된 SDNet 디스크립션으로 컴파일러를 재구동하는 경우, 새로운 하드웨어를 생성하지 않고 오직 펌웨어 업데이트로만 수용이 가능한지, 혹은 하드웨어(그리고 펌웨어) 재생성이 필요한지를 결정하게 된다. 대부분의 경우, 라인 카드에서 처리되는 프로토콜을 추가하거나 삭제하는 것과 같은 중간 규모의 업데이트는 펌웨어 업데이트 만으로 처리가 가능하다.

그림 10. SDNet 디자인 및 업데이트 플로우

모두 SDNet 컴파일러로 생성된 펌웨어 및 아키텍처 간의 긴밀한 연결은 사용자들이 히트리스 업그레이드를 수행할 수 있음을 의미하며, 이에 따라 펌웨어는 패킷 플로우를 방해하지 않고 서비스 중에 변경 및 배치된다. 따라서 기업들은 상당한 서비스 업그레이드를 어떠한 서비스 중단 없이도 수행할 수 있다. 이러한 혁신적인 개발은 독보적인 SDNet 기술의 특성 및 자일링스 올 프로그래머블 디바이스의 하이-레벨 사양이 결함됨으로써 달성되었다.

자일링스의 기반 기술

자일링스의 올 프로그래머블 디바이스는 1Gbit/sec에서 수 100Gbit/sec에 이르는 풀 라인 속도에서 차별화된 네트워크 프로토콜을 처리할 수 있는 완벽한 라인 카드 데이터 플레인 프로세서를 구현할 수 있다. 이러한 차원의 성능을 제공하는 FPGA는 수백 명의 사람들이 수년 간의 디자인을 통해 이룩할 수 있는 것으로, 전체론적인 접근방법으로 방대한 분야에 걸친 전문기술이 필요하고, 수많은 도전과제들을 해결해야 한다.

차세대 패킷 프로세싱과 관련된 극단적인 요건까지 서비스 할 수 있는 프로그래머블 디바이스를 설계할 때 발생되는 시스템-레벨의 문제는 상당히 엄청나다. 테라비트 데이터가 최신 SerDes 커넥티비티를 통해 멀티-기가비트 속도에서 최소한의 지연으로 FPGA로 입출력되어야 하며, 고속으로 동작하는 패킷 프로세싱 컴포넌트를 통과하기 위해 폭이 2,048bit 이상이 되는 내부 버스가 편재되어야 하고, 칩-전반의 클럭 스큐 및 지터 한도는 서브 나노세컨드 범위에 있어야 하고, 또한 모두 아주 적은 전력 한계치 만이 주어진다.

7 시리즈 올 프로그래머블 로직 디바이스와 보다 최근에 발표된 울트라스케일(UltraScale™) 제품군을 통해 자일링스는 고속 데이터 경로 프로세싱의 매우 어려운 과제들을 해결할 수 있는 업계 선도적인 다양한 첨단 기술을 현실화할 수 있게 되었다. 28nm 기반의 버텍스(Virtex®), 킨텍스(Kintex®), 아틱스(Artix®) 제품군은 28Gbit/sec를 지원하는 트랜시버, 통합 PCIe 3.0 컨트롤러, 완전 상용화된 3D IC 기반 제품을 비롯한 네트워킹에 필수적인 광범위한 기능들을 갖추고 있으며, 징크 올 프로그래머블 SoC는 ARM 코어텍스(Cortex) A9 프로세싱 서브 시스템을 통합하고 있다. 이러한 방대한 포트폴리오는 네트워크의 코어에서 에지에 이르기까지 네트워킹 장비를 위한 최적화 및 성능, 통합이 가능한 필수 실리콘 플랫폼을 제공하고 있다.

7 시리즈 제품군의 성공을 발판으로 자일링스는 차세대 네트워킹 애플리케이션의 과제를 보다 효과적으로 해결할 수 있는 향상된 울트라스케일 제품군을 출시했다. 울트라스케일은 ASIC-등급의 시스템-레벨 성능으로 전례 없는 뛰어난 통합 및 기능을 제공하는 업계 최초이자 유일한 아키텍처이다. 울트라스케일 아키텍처는 모놀리식에서 3D IC로의 확장과 더불어, 20nm 플래나 공정에서 16nm FinFET 기술을 넘어 더욱 진화하고 있다.

자일링스 비바도 디자인 수트를 통한 분석적 코-최적화를 통해, 울트라스케일 아키텍처는 방대한 라우팅 성능을 제공하면서도, 이전에는 전혀 가능하지 않았던 방법으로 전형적인 병목현상들을 효과적으로 해결할 수 있다.

차별화된 차세대 네트워킹 애플리케이션의 요구를 해결하기 위해 다음과 같은 다양한 기능과 성능들이 울트라스케일 제품군에 포함되었다:

멀티-테라비트 처리량 및 낮은 지연의 와이드 버스에 최적화된 방대한 데이터 플로우.

2세대 3D IC 시스템 통합 및 새로운 3D IC 와이드-메모리에 최적화된 인터페이스를 위한 인터-다이 대역폭의 단계 함수(Step Function).

차세대 DDR4 메모리 및 HMC(Hybrid Memory Cube) 기술 지원을 비롯한 방대한 I/O 및 메모리 대역폭.

매우 낮은 클럭 스큐와 고성능 확장성으로 저전력 클럭 네트워크를 제공하는 ASIC과 유사한 다중-영역 클럭킹.

하드와이어드된 ASIC-등급의 다중 100G 이더넷 및 150G 인터라켄, PCIe 및 기타 코어들.

7 시리즈 및 울트라스케일 제품군에 대한 개괄적인 설명은 표 1에 정리하였다.

자일링스 SDNet 소프트웨어 환경은 기본 비바도 디자인 수트에 기반하고 있으며, 디자인 수트 및 타깃 디바이스 간의 분석적 코-최적화를 통해 올 프로그래머블 아키텍처 제품군의 모든 잠재 가능성을 실현할 수 있다. 이러한 비용 및 성능, 전력이 완벽하게 최적화된 솔루션은 특정 데이터 플레인 프로세싱 기능 세트를 실현할 수 있다. SDNet 사양이 하이-레벨이면서도 독립적인 구현형태이기 때문에 사용자는 적합한 디바이스를 위한 적절한 기능들을 자동으로 구현할 수 있다.

또한 SDNet은 비바도 IPI(IP Integrator)와의 상호 연동을 통해 혜택을 얻을 수 있으며, 대형 시스템 구축을 위한 IP 코어 통합 시간을 단축할 수 있다. 기본적인 비바도 통합 디자인 환경에 기반한 IPI는 강력한 디버깅 기능과 더불어, 디바이스 및 플랫폼을 인지할 수 있는 인터랙티브 환경으로 핵심 IP 인터페이스에 대한 인텔리전트 자동-연결 기능 및 원-클릭 IP 서브시스템 생성, 실시간 디자인 룰 체크, 인터페이스 변경 전파 등을 지원한다. IPI는 비바도 디자인 툴을 이용해 디자인 및 IP를 올바르게 컨피규레이션할 수 있으며, IPI를 통해 오류없이 디자인을 구현할 수 있다. 인터페이스 레벨에서 작업하는 디자인 팀 또한 신속하게 복잡한 시스템을 구성할 수 있다. IPI의 통합 자동화된 인터페이스 및 디바이스 드라이버, 어드레스 맵 생성 기능은 디자인 어셈블리를 보다 가속화할 수 있다.

SDNet을 이용해 구현된 서브시스템은 SmartCORE IP 코어처럼 패킹이 가능하며, 이후 이렇게 생성된 SmartCOREs를 IPI를 이용해 다른 자일링스의 SmartCOREs 및 LogiCOREs, 써드파티 얼라이언스 코어(Alliance Cores), 사용자 고유의 IP 코어와 함께 통합하여 보다 큰 시스템을 구현할 수 있다. 또한 임베디드 프로세서 코어 상에서 동작하는 소프트웨어 컴포넌트도 포함시킬 수도 있다. 따라서 SDNet의 특화된 기능을 다른 프로세싱 도메인에 특화된 전력 툴과 함께 사용할 수 있다.

다른 접근법과의 비교

그림 11은 필요한 최고 속도의 데이터 경로 프로세싱을 제공하는 다른 대안적 접근방식의 특성과 비교한 SDNet의 일부 주요 기능을 보여주고 있다.

그림 11. 다른 대안적 방법과 비교한 SDNet의 주요 특징들

맨 하단은 사전 고정형 기술 부분에서 사용하지 않은 리소스가 낭비되지 않도록 SDNet이 리소스를 최적화하여 구현한 것이다. 또한 고정형 아키텍처 기술을 넘어 패킷 플로우 아키텍처 매칭으로 설계를 최적화하여 구현할 수 있도록 해준다. 더불어 동일한 SDNet 패킷 프로세싱 사양을 성능 요건을 늘리거나 줄이는 경우에도 사용할 수 있다.

처음부터 SDNet으로 구현하는 특성화 작업은 네트워크 및 네트워크 기능의 가상화, 그리고 이러한 네트워크의 소프트웨어 정의가 보다 더 중요한 시기에는 더욱 필수적이다. 이는 필요한 성능을 제공하는 하드웨어는 물론, 빠르게 변화하는 기능 및 프로비저닝, 프로토콜, 표준에 대응할 수 있는 유연성도 제공한다. 따라서 SDNet은 독자적으로 완벽한 차세대 기술이 될 수 있다.

요약

자일링스의 SDNet 사양 환경은 SDN 및 Softly Defined Networks 모두를 아우르는 새롭고 혁신적인 제품을 효율적으로 현실화하는 네트워킹 시스템 설계의 새로운 가능성을 제시하는 획기적인 기술이다. SDNet은 매우 높은 라인 레이트로 데이터를 수신 및 전송할 수 있는 자일링스의 방대한 올 프로그래머블 디바이스의 성능을 통해 탁월한 혜택을 얻을 수 있으며, 모든 레벨의 네트워크에서 요구되는 라인 카드 데이터 플레인 프로세싱 기능을 수행할 수 있다. SDNet의 혁신은 가공되지 않은 실리콘 기능을 어떻게 구현할 것인가 보다는 필요한 사양을 현실화해 주는 최상의 하이-레벨 디자인 방법론을 통해 보다 많은 사용자들이 손쉽게 이용할 수 있도록 해주는 것이다. 이러한 방법론은 새로운 시스템 컴포넌트를 위한 스마트 편집기능 및 표준 네트워킹 기능을 위한 최적화된 SmartCOREs 라이브러리를 모두 통합하고 있다. 히트리스 현장 업그레이드 수행능력 및 네트워크 인텔리전스 기반 소프트웨어 정의 제어 플레인, 그리고 콘텐트 인텔리전스 기반 소프트웨어 정의 데이터 플레인 기능을 모두 겸비하고 있는 SDNet은 위험요소를 줄이고, 마켓 출시시기를 단축할 수 있으며, 가용성 및 확장 가능성이 향상된다. 다시 말해, SDNet은 업계의 SDN 흐름에 대응할 수 있는 핵심 열쇠이며, 네트워킹 시스템 디자이너 및 설계자들의 생산성 또한 높일 수 있다.

SDNet에 대한 보다 자세한 정보는 자일링스 웹사이트(www.xilinx.com)나 한국지사를 통해 얻을 수 있다.

- 태그 :

- SDNET,SDN,OTT,Traversing,Content Addressable Memory,Longest-Prefix Match,Ternary Content Addressable Memory

- 적용분야 :

- Data Center, Smarter Networks

- 관련제품 :

- SDAccel, UltraScale, Vivado Design Suite, ZYNQ