Technical Article

제품 및 Tools

소프트웨어-정의(Software-Defined) 개발 방식, 신호 처리를 한 차원 향상 시키다

소프트웨어-정의(Software-Defined) 개발 방식, 신호 처리를 한 차원 향상 시키다

2016-09-21

디지털 신호처리는 오늘날 필수적으로 요구되는 장비 및 서비스에서 핵심적인 역할을 수행한다. 이러한 장비 및 서비스에는 통신 및 네트워킹, 모바일 통신, 디지털 오디오, 스트리밍 비디오, 산업용 모터제어, 머신 비전, 자동차 운전자 지원, 고성능 레이더, GSI(Government Signals Intelligence) 등 다양하다.

글/ 올리비에 트리무와(Olivier Tremois), DSP 스페셜리스트 FAE, 자일링스 유럽

보다 정교한 시스템 기능 요건에 부합하기 위해, 지연은 감소되고, 채널 용량은 증대된 전용 DSP(Digital Signal Processor)가 수십 GFLOPS 처리량을 제공하고, 단일 DSP나 대규모의 다중-DSP 보드에 사용이 가능한 멀티코어 디바이스로 진화하고 있다.

하지만 여전히 진화에 대한 요구는 계속해서 증가하고 있으며, 최신 장비 디자이너들은 보다 뛰어난 시스템 통합 및 적은 컴포넌트 수, 향상된 안정성, 낮은 비용을 실현하기 위해 고군분투하고 있다. 이러한 요구를 충족시키기 위해, ARM® Cortex™-M4 디바이스와 같은 소형 임베디드 마이크로컨트롤러에서 프로그래머블 SoC(Sytem-on-Chip) IC에 이르기까지 다양한 플랫폼에 DSP가 확장, 통합되고 있다. 이러한 고성능 컨피규러블 디바이스는 프로세싱 집약적 작업 요건에 직면해 있는 디자이너들에게 가장 우선적으로 선택되고 있으며, 이러한 디바이스는 고도의 병렬 처리는 물론, 고성능 인터페이스 및 맞춤형 가속기를 필요로 하는 시스템 요건을 만족시킬 수 있다.

최신 DSP 플랫폼

컨피규러블 SoC는 수많은 DSP 블록과 함께 프로세서 및 메모리, 주변장치, 프로그래머블 로직을 비롯한 시스템을 기능들을 통합하고 있다. 자일링스(Xilinx®) 징크-7000(Zynq®-7000) 올 프로그래머블(All Programmable) SoC는 각각 25x8 멀티플라이어와 48bit 어큐뮬레이터 및 관련 기능을 포함하고 있는 최고 2,020개의 DSP 슬라이스를 가지고 있다. 또한 온칩 듀얼-코어 ARM Cortex-A9 MPCore™ 애플리케이션 프로세싱 장치와 USB 2.0, 기가비트 이더넷과 같은 표준 고속 주변장치 및 LPDDR2, DDR3과 같은 다이나믹 메모리 인터페이스를 갖추고 있다.

반면, 다중-프로세서 징크 MPSoC™는 27x18 멀티플라이어를 내장한 최고 3,528개의 DSP 슬라이스와 더불어, 별도의 PCIe® Gen2, USB3.0, SATA 3.1, DisplayPort 주변장치 등의 추가적인 리소스를 갖추고 있으며, DDR4 다이나믹 메모리를 지원한다. 또한 이 MPSoC 아키테처는 듀얼-코어 ARM Cortex-R5 MPCore 실시간 프로세싱 코어와 쿼드-코어 A53는 물론, ARM Mali™-400 MP2 GPU(Graphics Processing Unit) 및 H.264/H.265 비디오 코덱을 통합하고 있다.

또한 징크-7000 및 MPSoC 고성능 ARM 프로세서는 멀티미디어 가속을 위한 NEON™ 기술뿐만 아니라, FPGA DSP 슬라이스, 통합 주변장치 및 최고 1,143,000개의 로직 셀(울트라스케일+(UltraScale+) MPSoC의 경우)이 긴밀하게 통합되어 있어 다양한 혜택을 제공한다. 이 디바이스는 이러한 리소스를 통해 기존의 멀티코어 DSP 성능 이상의 고도의 병렬 프로세싱 및 방대한 시스템 통합을 실현할 수 있다.

이제 디자인 팀은 기존의 DSP에서 올 프로그래머블 SoC 플랫폼으로 도약함으로써 대규모 다중-DSP 보드의 성능 한계를 넘어설 수 있는 최적의 시기를 맞이했다. 자일링스 엔지니어는 최근 이러한 기술을 활용해 한 고객이 기존의 32개 DSP 칩이 포함된 레이더 보드를 재디자인해, 단 2개의 필드-프로그래머블 디바이스 기반의 새로운 플랫폼으로 전환하는데 도움을 주었다.

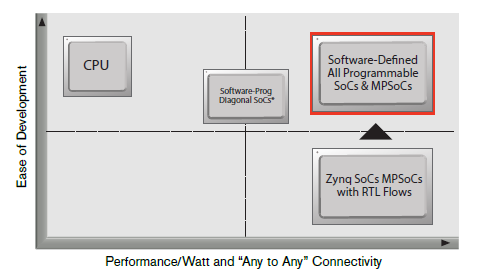

C/C++ 레벨에서 하드웨어 합성

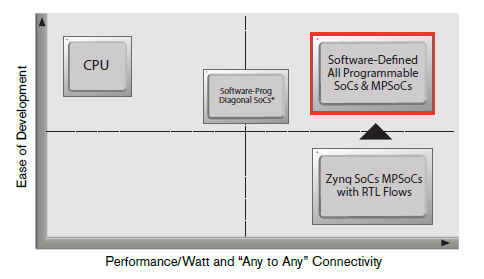

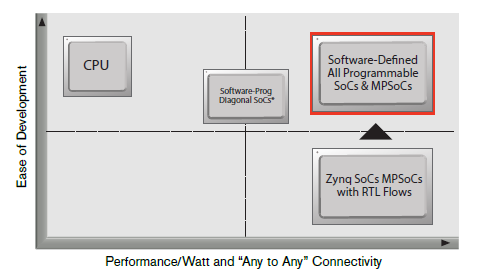

일반적으로 프로그래머블 FPGA 및 SoC 디자인을 위해서는 RTL(Register Transfer Level)로 디자인 작업을 처리할 수 있는 하드웨어 디자인 능력을 갖춘 엔지니어가 필요하다. 따라서 대부분 소프트웨어-설계 능력을 갖춘 팀은 이러한 제품을 통한 부가적인 기능 및 통합의 장점을 활용하기가 어려웠다. 그림 1은 소프트웨어 개발 편의성 대비 효율성 및 유연성 간의 트레이드-오프를 그래픽적으로 나타낸 것이다. 이 다이어그램은 기존 소프트웨어-프로그래머블 프로세서와 RTL레벨에서 프로그램하는 프로그래머블 디바이스 또는 소프트웨어-정의 디자인 플로우를 이용한 작업을 비교한 것이다.

그림 1. 소프트웨어-정의 플로우는 임베디드 소프트웨어 개발자들이

올 프로그래머블 SoC 디바이스의 성능 잠재성을 실현할 수 있도록 해준다.

기존의 DSP-기반 솔루션 디자인은 안전한 접근방법으로 여겨져 왔다. 하지만 높은 성능으로 실행되는 애플리케이션에 대한 요구가 계속해서 증가함에 따라, 고성능 DSP는 멀티코어 아키텍처로 인해 디자인이 갈수록 어려워지고 있다. 따라서 시스템 및 임베디드-소프트웨어 엔지니어들이 올 프로그래머블 SoC IC를 이용해 다중-프로세싱 시스템을 구현할 수 있도록 ASSP와 같은 C/C++ 디자인 환경에 대한 필요성이 대두되고 있다.

ASSP와 같은 프로그래밍 환경

이러한 개발환경을 제공하는 자일링스의 SDSoC™는, 소프트웨어 엔지니어들이 전통적인 FPGA 툴이나 HDL(Hardware Design Language)을 사용할 필요없이 프로그래머블 디바이스를 위한 C/C++ 애플리케이션을 개발할 수 있도록 해준다. 이는 시스템 성능을 극대화할 수 있도록 온칩 프로세싱 및 DSP 리소스는 물론, 프로그래머블 하드웨어와 메모리를 처리할 수 있다.

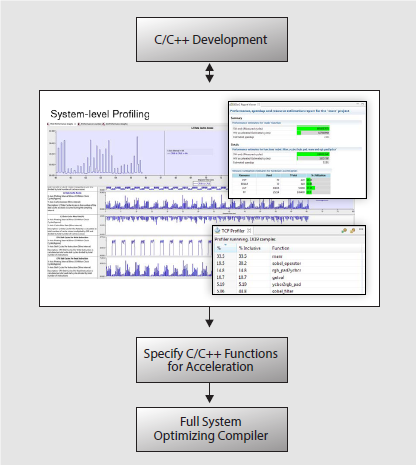

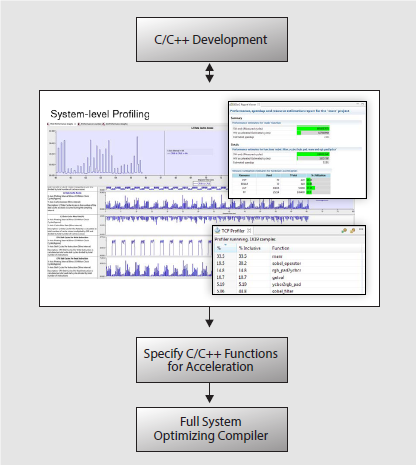

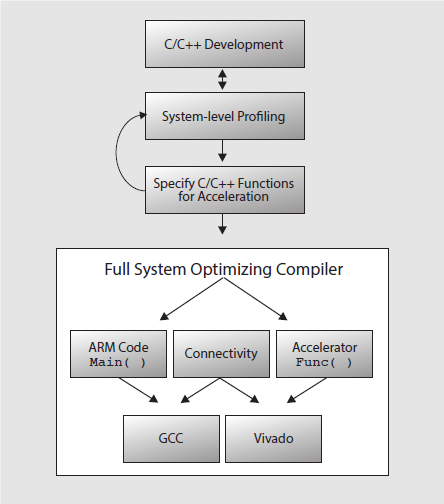

이 개발환경은 전반적인 시스템 성능 및 전력소모를 초기에 확인할 수 있도록 해주는 시스템-레벨 프로파일러를 포함하고 있다. 그림 2는 이 프로파일러가 SDSoC 플로우에 어떻게 적용되는지 보여주고 있다. 이 프로파일러는 프로그래머블 로직을 이용해 가속이 가능한 C/C++ 기능을 식별할 수 있도록 신속하게 시스템 성능을 예측한다. 그럼 다음, SDSoC는 소프트웨어 사이클을 리포트하기 위해 코드를 측정하고, 데이터-전송 시간을 예측하고, 캐시나 메모리, 버스 활용과 같은 하드웨어 활용도를 모니터링한다. 이러한 기능은 징크 플랫폼 상에서 구동되는 완성된 디자인의 소프트웨어-하드웨어 성능 측정을 수행하는 자일링스의 SDK에서 구현된 프로파일링 기능에 기반하고 있다. 고속 예측 툴은 사용자가 소프트웨어에서 하드웨어로 하나 이상의 기능을 이전함으로써 성능에 어떠한 영향을 미치는지 신속하게 예측할 수 있도록 해준다. 소프트웨어 개발자가 이러한 방법으로 독립적으로 C/C++ 기능을 가속할 수 있게 됨으로써 하드웨어 및 소프트웨어 팀간의 시간 소모적인 상호 조정작업을 간소화해 주며, 프로그래머블 로직의 장점을 충분히 활용하여 소프트웨어를 가속하기 위한 수많은 반복작업을 최소화할 수 있다. 일반적으로 실제 하드웨어를 생성하는데 수시간 이상이 소요되었던 것과 비교해, 모든 변경으로 인한 영향을 수분 내에 예측이 가능하다.

그림 2. 비-간섭 프로파일러는 PC 샘플링에 기반하고 있다.

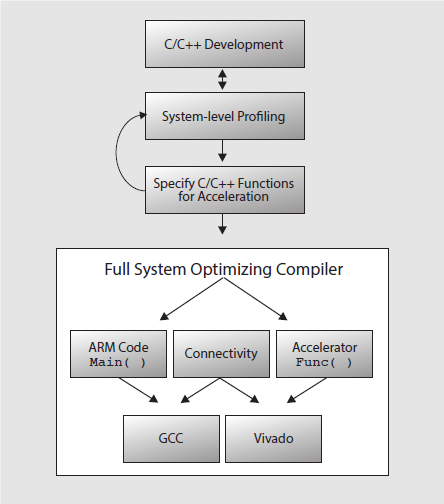

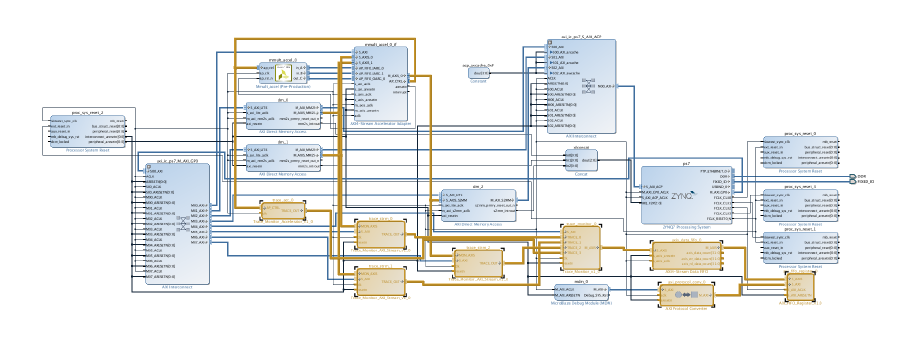

또한 C/C++ 풀-시스템 최적화 컴파일러가 포함되어 있는데, 이는 이러한 유형의 툴로서는 업계 최초이다. 그림 3에 나타낸 것처럼, 이는 SoC의 ARM 프로세서는 물론, 프로그래머블 로직 및 커넥티비티를 처리할 수 있다. 이 컴파일러는 지연, 대역폭, 하드웨어 활용도에 최적화된 HDL 코드를 생성한다. 시스템-레벨 프로파일러와 함께 시스템-최적화 컴파일러는 하드웨어 가속 기능이 없는 소프트웨어-중심 솔루션에 비해 최고 100배까지 전반적인 성능을 향상시킬 수 있다.

그림 3. 풀-시스템 컴파일러는 성능 및 처리량, 지연을 제어할 수 있으며,

디자인-반복 시간을 단축할 수 있다.

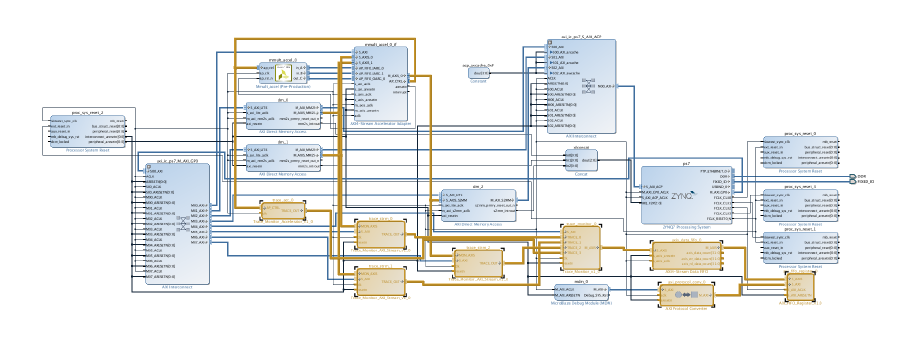

FPGA 디자인 경험을 갖춘 시스템 설계자 및 플랫폼 개발자는 SDSoC의 장점을 활용해 임베디드-소프트웨어 개발자에게 이관되는 최적화된 애플리케이션 플랫폼을 개발할 수 있다. 이 툴은 자동 시스템 커넥티비티 생성과 같은 기능을 통해 설계자가 징크 프로세싱 시스템 및 메모리, 프로그래머블 로직-기반 가속기 간의 최적화된 인터커넥트 아키텍처를 신속하게 작업할 수 있도록 해준다.

또한 설계자는 애플리케이션에 특화된 플랫폼을 개발하고, 기존 FPGA IP를 C로 호출 가능한 라이브러리처럼 RTL 디스크립션을 컨피규레이션하기 위해 자일링스의 비바도(Vivado®) 디자인 수트와 함께 SDSoC를 이용할 수 있어 재사용을 통한 디자인 생산성을 높일 수 있다.

하드웨어/소프트웨어 시스템-성능 분석

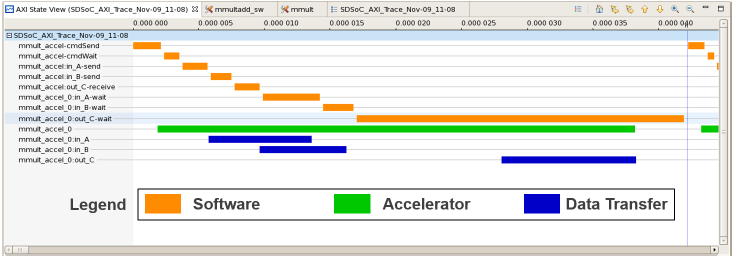

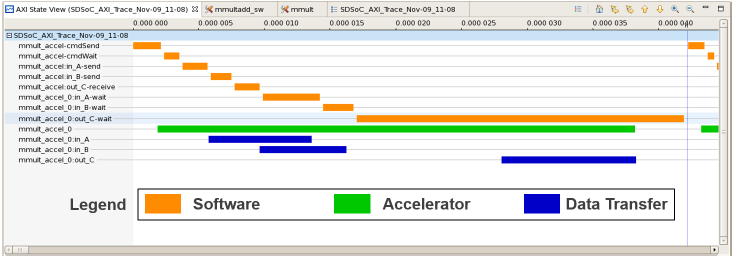

엔지니어는 SDSoC 추적 툴을 이용하여 자신의 디자인이 작업부하나 하드웨어/소프트웨어 파티셔닝, 시스템 디자인 선택과 관련하여 어떻게 실행되는지 확인할 수 있다. SDSoC Trace는 프로세서 및 하드웨어 가속기, 시스템의 데이터 전송링크 상에서 구동되는 추적 소프트웨어로 애플리케이션이 실행되면서 발생하는 시스템 이벤트를 상세하게 보여준다. 이 이벤트는 시간대로 그래픽으로 보여진다. 이벤트 로깅과 비교해 추적 툴은 해당 기간 동안 이벤트 간의 상호작용을 보여주기 때문에 하드웨어/소프트웨어 시스템의 애플리케이션 성능을 보다 자세히 파악할 수 있다. 그림 4는 SDSoC Trace가 어떻게 하드웨어 시스템에 자동으로 모니터링을 삽입하는지 보여준다. 또한 추적 장치는 소프트웨어 시스템에 자동으로 삽입된다. 그림 4b는 각기 다른 유형의 이벤트가 하이라이트된 하드웨어 및 소프트웨어 트레이스 스트림을 보여준다.

그림 4-a. Trace가 활성화 되면, SDSoC 트레이스는 자동으로 필요한 모니터링 및 장치를 삽입한다.

그림 4-b. 트레이스 시각화 도구는 하드웨어/소프트웨어 시스템에서 이벤트 간의 상호작용을 보여준다.

보드 디자인 지원

SDSoC는 ZC702 및 ZC706을 비롯한 징크 올 프로그래머블 SoC-기반 개발 보드와 Zedboard, MicroZed, ZYBO를 비롯한 협력업체 및 마켓별로 특화된 플랫폼은 물론, 비디오 및 이미징 개발 키트를 이용해 보드-디자인 작업과 동시에 소프트웨어 엔지니어링을 시작할 수 있도록 해준다. 각 보드를 위한 BSP(Board Support Package)가 지원되며, SDSoC로 임베디드 소프트웨어 개발자 및 시스템 설계자를 위한 플랫폼을 추상화할 수 있는 메타데이터가 포함되어 있어, 생산성을 보다 향상시키고, 제품 개발 시간을 단축할 수 있다.

결론

올 프로그래머블 SoC 및 MPSoC 디바이스는 ARM/NEON 애플리케이션 프로세싱 리소스와 수많은 DSP 슬라이스, FPGA 패브릭을 모두 갖추고 있어 현재 최상의 전용 프로세서의 성능을 훨씬 뛰어넘는 DSP 성능을 구현할 수 있도록 해준다. 새로운 최신 소프트웨어-정의 개발 환경은 소프트웨어 엔지니어들이 이러한 새로운 디바이스의 성능상의 장점을 독립적으로 활용할 수 있도록 해주며, 또한 시스템 설계자 및 플랫폼 개발자는 보다 전문적인 활용이 가능하다. 고성능 신호 처리 구현이 이보다 더 간단한 적은 없었을 것이다.

글/ 올리비에 트리무와(Olivier Tremois), DSP 스페셜리스트 FAE, 자일링스 유럽

보다 정교한 시스템 기능 요건에 부합하기 위해, 지연은 감소되고, 채널 용량은 증대된 전용 DSP(Digital Signal Processor)가 수십 GFLOPS 처리량을 제공하고, 단일 DSP나 대규모의 다중-DSP 보드에 사용이 가능한 멀티코어 디바이스로 진화하고 있다.

하지만 여전히 진화에 대한 요구는 계속해서 증가하고 있으며, 최신 장비 디자이너들은 보다 뛰어난 시스템 통합 및 적은 컴포넌트 수, 향상된 안정성, 낮은 비용을 실현하기 위해 고군분투하고 있다. 이러한 요구를 충족시키기 위해, ARM® Cortex™-M4 디바이스와 같은 소형 임베디드 마이크로컨트롤러에서 프로그래머블 SoC(Sytem-on-Chip) IC에 이르기까지 다양한 플랫폼에 DSP가 확장, 통합되고 있다. 이러한 고성능 컨피규러블 디바이스는 프로세싱 집약적 작업 요건에 직면해 있는 디자이너들에게 가장 우선적으로 선택되고 있으며, 이러한 디바이스는 고도의 병렬 처리는 물론, 고성능 인터페이스 및 맞춤형 가속기를 필요로 하는 시스템 요건을 만족시킬 수 있다.

최신 DSP 플랫폼

컨피규러블 SoC는 수많은 DSP 블록과 함께 프로세서 및 메모리, 주변장치, 프로그래머블 로직을 비롯한 시스템을 기능들을 통합하고 있다. 자일링스(Xilinx®) 징크-7000(Zynq®-7000) 올 프로그래머블(All Programmable) SoC는 각각 25x8 멀티플라이어와 48bit 어큐뮬레이터 및 관련 기능을 포함하고 있는 최고 2,020개의 DSP 슬라이스를 가지고 있다. 또한 온칩 듀얼-코어 ARM Cortex-A9 MPCore™ 애플리케이션 프로세싱 장치와 USB 2.0, 기가비트 이더넷과 같은 표준 고속 주변장치 및 LPDDR2, DDR3과 같은 다이나믹 메모리 인터페이스를 갖추고 있다.

반면, 다중-프로세서 징크 MPSoC™는 27x18 멀티플라이어를 내장한 최고 3,528개의 DSP 슬라이스와 더불어, 별도의 PCIe® Gen2, USB3.0, SATA 3.1, DisplayPort 주변장치 등의 추가적인 리소스를 갖추고 있으며, DDR4 다이나믹 메모리를 지원한다. 또한 이 MPSoC 아키테처는 듀얼-코어 ARM Cortex-R5 MPCore 실시간 프로세싱 코어와 쿼드-코어 A53는 물론, ARM Mali™-400 MP2 GPU(Graphics Processing Unit) 및 H.264/H.265 비디오 코덱을 통합하고 있다.

또한 징크-7000 및 MPSoC 고성능 ARM 프로세서는 멀티미디어 가속을 위한 NEON™ 기술뿐만 아니라, FPGA DSP 슬라이스, 통합 주변장치 및 최고 1,143,000개의 로직 셀(울트라스케일+(UltraScale+) MPSoC의 경우)이 긴밀하게 통합되어 있어 다양한 혜택을 제공한다. 이 디바이스는 이러한 리소스를 통해 기존의 멀티코어 DSP 성능 이상의 고도의 병렬 프로세싱 및 방대한 시스템 통합을 실현할 수 있다.

이제 디자인 팀은 기존의 DSP에서 올 프로그래머블 SoC 플랫폼으로 도약함으로써 대규모 다중-DSP 보드의 성능 한계를 넘어설 수 있는 최적의 시기를 맞이했다. 자일링스 엔지니어는 최근 이러한 기술을 활용해 한 고객이 기존의 32개 DSP 칩이 포함된 레이더 보드를 재디자인해, 단 2개의 필드-프로그래머블 디바이스 기반의 새로운 플랫폼으로 전환하는데 도움을 주었다.

C/C++ 레벨에서 하드웨어 합성

일반적으로 프로그래머블 FPGA 및 SoC 디자인을 위해서는 RTL(Register Transfer Level)로 디자인 작업을 처리할 수 있는 하드웨어 디자인 능력을 갖춘 엔지니어가 필요하다. 따라서 대부분 소프트웨어-설계 능력을 갖춘 팀은 이러한 제품을 통한 부가적인 기능 및 통합의 장점을 활용하기가 어려웠다. 그림 1은 소프트웨어 개발 편의성 대비 효율성 및 유연성 간의 트레이드-오프를 그래픽적으로 나타낸 것이다. 이 다이어그램은 기존 소프트웨어-프로그래머블 프로세서와 RTL레벨에서 프로그램하는 프로그래머블 디바이스 또는 소프트웨어-정의 디자인 플로우를 이용한 작업을 비교한 것이다.

그림 1. 소프트웨어-정의 플로우는 임베디드 소프트웨어 개발자들이

올 프로그래머블 SoC 디바이스의 성능 잠재성을 실현할 수 있도록 해준다.

기존의 DSP-기반 솔루션 디자인은 안전한 접근방법으로 여겨져 왔다. 하지만 높은 성능으로 실행되는 애플리케이션에 대한 요구가 계속해서 증가함에 따라, 고성능 DSP는 멀티코어 아키텍처로 인해 디자인이 갈수록 어려워지고 있다. 따라서 시스템 및 임베디드-소프트웨어 엔지니어들이 올 프로그래머블 SoC IC를 이용해 다중-프로세싱 시스템을 구현할 수 있도록 ASSP와 같은 C/C++ 디자인 환경에 대한 필요성이 대두되고 있다.

ASSP와 같은 프로그래밍 환경

이러한 개발환경을 제공하는 자일링스의 SDSoC™는, 소프트웨어 엔지니어들이 전통적인 FPGA 툴이나 HDL(Hardware Design Language)을 사용할 필요없이 프로그래머블 디바이스를 위한 C/C++ 애플리케이션을 개발할 수 있도록 해준다. 이는 시스템 성능을 극대화할 수 있도록 온칩 프로세싱 및 DSP 리소스는 물론, 프로그래머블 하드웨어와 메모리를 처리할 수 있다.

이 개발환경은 전반적인 시스템 성능 및 전력소모를 초기에 확인할 수 있도록 해주는 시스템-레벨 프로파일러를 포함하고 있다. 그림 2는 이 프로파일러가 SDSoC 플로우에 어떻게 적용되는지 보여주고 있다. 이 프로파일러는 프로그래머블 로직을 이용해 가속이 가능한 C/C++ 기능을 식별할 수 있도록 신속하게 시스템 성능을 예측한다. 그럼 다음, SDSoC는 소프트웨어 사이클을 리포트하기 위해 코드를 측정하고, 데이터-전송 시간을 예측하고, 캐시나 메모리, 버스 활용과 같은 하드웨어 활용도를 모니터링한다. 이러한 기능은 징크 플랫폼 상에서 구동되는 완성된 디자인의 소프트웨어-하드웨어 성능 측정을 수행하는 자일링스의 SDK에서 구현된 프로파일링 기능에 기반하고 있다. 고속 예측 툴은 사용자가 소프트웨어에서 하드웨어로 하나 이상의 기능을 이전함으로써 성능에 어떠한 영향을 미치는지 신속하게 예측할 수 있도록 해준다. 소프트웨어 개발자가 이러한 방법으로 독립적으로 C/C++ 기능을 가속할 수 있게 됨으로써 하드웨어 및 소프트웨어 팀간의 시간 소모적인 상호 조정작업을 간소화해 주며, 프로그래머블 로직의 장점을 충분히 활용하여 소프트웨어를 가속하기 위한 수많은 반복작업을 최소화할 수 있다. 일반적으로 실제 하드웨어를 생성하는데 수시간 이상이 소요되었던 것과 비교해, 모든 변경으로 인한 영향을 수분 내에 예측이 가능하다.

그림 2. 비-간섭 프로파일러는 PC 샘플링에 기반하고 있다.

또한 C/C++ 풀-시스템 최적화 컴파일러가 포함되어 있는데, 이는 이러한 유형의 툴로서는 업계 최초이다. 그림 3에 나타낸 것처럼, 이는 SoC의 ARM 프로세서는 물론, 프로그래머블 로직 및 커넥티비티를 처리할 수 있다. 이 컴파일러는 지연, 대역폭, 하드웨어 활용도에 최적화된 HDL 코드를 생성한다. 시스템-레벨 프로파일러와 함께 시스템-최적화 컴파일러는 하드웨어 가속 기능이 없는 소프트웨어-중심 솔루션에 비해 최고 100배까지 전반적인 성능을 향상시킬 수 있다.

그림 3. 풀-시스템 컴파일러는 성능 및 처리량, 지연을 제어할 수 있으며,

디자인-반복 시간을 단축할 수 있다.

FPGA 디자인 경험을 갖춘 시스템 설계자 및 플랫폼 개발자는 SDSoC의 장점을 활용해 임베디드-소프트웨어 개발자에게 이관되는 최적화된 애플리케이션 플랫폼을 개발할 수 있다. 이 툴은 자동 시스템 커넥티비티 생성과 같은 기능을 통해 설계자가 징크 프로세싱 시스템 및 메모리, 프로그래머블 로직-기반 가속기 간의 최적화된 인터커넥트 아키텍처를 신속하게 작업할 수 있도록 해준다.

또한 설계자는 애플리케이션에 특화된 플랫폼을 개발하고, 기존 FPGA IP를 C로 호출 가능한 라이브러리처럼 RTL 디스크립션을 컨피규레이션하기 위해 자일링스의 비바도(Vivado®) 디자인 수트와 함께 SDSoC를 이용할 수 있어 재사용을 통한 디자인 생산성을 높일 수 있다.

하드웨어/소프트웨어 시스템-성능 분석

엔지니어는 SDSoC 추적 툴을 이용하여 자신의 디자인이 작업부하나 하드웨어/소프트웨어 파티셔닝, 시스템 디자인 선택과 관련하여 어떻게 실행되는지 확인할 수 있다. SDSoC Trace는 프로세서 및 하드웨어 가속기, 시스템의 데이터 전송링크 상에서 구동되는 추적 소프트웨어로 애플리케이션이 실행되면서 발생하는 시스템 이벤트를 상세하게 보여준다. 이 이벤트는 시간대로 그래픽으로 보여진다. 이벤트 로깅과 비교해 추적 툴은 해당 기간 동안 이벤트 간의 상호작용을 보여주기 때문에 하드웨어/소프트웨어 시스템의 애플리케이션 성능을 보다 자세히 파악할 수 있다. 그림 4는 SDSoC Trace가 어떻게 하드웨어 시스템에 자동으로 모니터링을 삽입하는지 보여준다. 또한 추적 장치는 소프트웨어 시스템에 자동으로 삽입된다. 그림 4b는 각기 다른 유형의 이벤트가 하이라이트된 하드웨어 및 소프트웨어 트레이스 스트림을 보여준다.

그림 4-a. Trace가 활성화 되면, SDSoC 트레이스는 자동으로 필요한 모니터링 및 장치를 삽입한다.

그림 4-b. 트레이스 시각화 도구는 하드웨어/소프트웨어 시스템에서 이벤트 간의 상호작용을 보여준다.

보드 디자인 지원

SDSoC는 ZC702 및 ZC706을 비롯한 징크 올 프로그래머블 SoC-기반 개발 보드와 Zedboard, MicroZed, ZYBO를 비롯한 협력업체 및 마켓별로 특화된 플랫폼은 물론, 비디오 및 이미징 개발 키트를 이용해 보드-디자인 작업과 동시에 소프트웨어 엔지니어링을 시작할 수 있도록 해준다. 각 보드를 위한 BSP(Board Support Package)가 지원되며, SDSoC로 임베디드 소프트웨어 개발자 및 시스템 설계자를 위한 플랫폼을 추상화할 수 있는 메타데이터가 포함되어 있어, 생산성을 보다 향상시키고, 제품 개발 시간을 단축할 수 있다.

결론

올 프로그래머블 SoC 및 MPSoC 디바이스는 ARM/NEON 애플리케이션 프로세싱 리소스와 수많은 DSP 슬라이스, FPGA 패브릭을 모두 갖추고 있어 현재 최상의 전용 프로세서의 성능을 훨씬 뛰어넘는 DSP 성능을 구현할 수 있도록 해준다. 새로운 최신 소프트웨어-정의 개발 환경은 소프트웨어 엔지니어들이 이러한 새로운 디바이스의 성능상의 장점을 독립적으로 활용할 수 있도록 해주며, 또한 시스템 설계자 및 플랫폼 개발자는 보다 전문적인 활용이 가능하다. 고성능 신호 처리 구현이 이보다 더 간단한 적은 없었을 것이다.

- 적용분야 :

- Automotive, Audio, Industrial, Smarter Networks, Wireless Communications

- 관련제품 :

- ZYNQ