Technical Article

제품 및 Tools

FPGA 디자인, 타이밍 만족이 모든 것!

FPGA 디자인, 타이밍 만족이 모든 것!

2014-11-01

툴이나 디자인 기법은 타이밍 성능 목표를 효율적으로 달성하기 위해 존재하는 것이다.

글 / 앤젤라셔튼(Angela Sutton) 제품 마케팅 매니저 (sutton@synopsys.com)

폴 오웬스(Paul Owens) 기업 애플리케이션 엔지니어 (powens@synopsys.com)

FPGA 디자인에서 타이밍 성능 목표를 달성하지 못한 경우, 원인을 명확히 밝히는 것은 상당히 어려운 일이다. 솔루션은 타이밍에 부합하도록 디자인을 최적화하기 위한 FPGA 구현 툴의 성능뿐만 아니라, 목표를 미리 규정하고,타이밍 문제를 진단하고 분리하는디자이너의 능력에 따라서 달라지기 때문이다. 디자이너는 클럭을 설정하는데 도움을 주는 특정 팁이나 트릭에액세스할 수 있다. 즉 시놉시스(Synopsys)의Synplify Premier와 같은 툴을 이용해 타이밍 제약조건(timing constraints)을 올바르게 설정한 다음, 자일링스(Xilinx®)FPGA 디자인 상에서 성능 목표를 달성할 수 있도록 파라미터를 조정할 수 있다.

다음과 같은 다양한 측면의 접근이 가능하다:

• 정확하고 완벽한 타이밍 제약조건(timing constraints) 및 클럭 사양과 같은 향상된 디자인 설정;

• 성능을 향상시키기 위해 세심한 RTL 코딩과 같은 시간을 단축하는 디자인 기법과 추후 디자인을 조정할 때 반복적인 런타임을 줄이기 위해 성능상 문제 발생 소지가 있는 부분에 대한 그룹핑;

• 향상된 QoR(Quality of Results) 및 타이밍 클로저를 제공하기 위해 합성 및 P&R(Place and Route) 타이밍 상관 관계 고려

위 3가지 범주에 해당하는 몇 가지 기법들을 자세히 살펴보고, 타이밍 목표를 달성하는데 어떻게 이용할 수 있는지 검토해 보도록 하자.

1 단계: 향상된 디자인 설정

가장 최선의 방법은 올바르고 완벽하게 디자인 제약조건(design constraints)을 설정하는 것이다. 제약조건은 합성 툴에 디자인의 목적 및 디자인의 성능 목표를 제시하는 것이다. 디자인이 합성되고 나면, 이러한 제약조건과 중요 경로 정보는 계속해서 타이밍에 부합하도록 자동으로 비바도 디자인 수트(Vivado® Design Suite)의 P&R 툴에 부가된다.

합성 툴은 사전 합성된 제약조건으로 복잡한 설정 작업을 지원할 수 있다. 여러분이 해야 할 일은 다음과 같다:

1. 클럭 확인

2. 클럭 그룹화 및 클럭간 상관관계 확인 및 생성

3. 클럭 제한

4. 디자인 입력 및 출력 제한

5. 다중 사이클 경로 및 불필요 경로(false path) 정의

여러분은 과도한 제약조건(over-constraint) 없이 디자인을 적절하고 완벽하게 제한했는지 확인하고자 할 것이다. 과도한 제약조건(over-constraint) 은 런타임을 길어지게 하고, 불필요 경로에 대한 보고를 유발하게 된다. 따라서 다중 사이클 및 불필요 경로를 명확히 하고, 파생 클럭의 제약조건을 확인해야 한다.(define_path_delay,define_false_path)

비바도플로우를 위한 초기 제약조건(constraints) 파일 설정

제약조건 설정은 쉽지 않은 작업이기 때문에, 합성 소프트웨어는 출발점이 되어주는 기본적인 제약조건 및 구문(Syntax)을 갖춘 초기 제약조건 탬플릿을 제공함으로써 도움을 준다. 예를 들어, Synplify 합성 소프트웨어는 특정 디자인을 위한 초기 FDC 파일을 생성하기 위해 TCL 유틸리티를 구동한다:

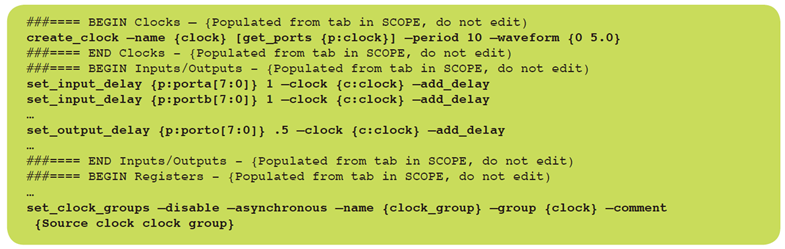

TCL: create_fdc_template

그림 1은 이 프로세스가 생성하게 되는 제약조건(.fdc) 파일 사례를 보여주고 있다. 이 예제에서, 클럭 및 클럭 그룹(클럭 간의 연관관계), 입력/출력 지연에 대한 언문을 비롯해 주의가 필요한 핵심 아이템들을 확인할 수 있다.

비바도 디자인 수트플로우에서 제약조건(constraints) 설정을 위한 모범사례

비바도 디자인 수트플로우에서 제약조건을 설정할 때, 다음과 같은 내용을 명확히 해야 한다:

• 입력 포트 또는 입력 포트와 연결된 넷트 상의 모든 주요 클럭 정의

• 블랙박스 출력 핀 상의 클럭 정의

•넷트 상에서 생성된 클럭 정의

•게이트클럭은 정의하지 않는다.

• 올바른 클럭 제약조건 제공: 과도하게 제약조건이 설정되지 않도록 하고, 다른 클럭 그룹에 관련없는(혹은 비동기화된) 클럭이 배치되었는지 확인

•불필요 경로 및 다중 사이클 경로와 같은 타이밍 예외사항 정의

힌트: 비바도 디자인 수트에서클럭 제약조건은 자일링스 ISE® 디자인 수트플로우에서 그랬던 것처럼 BUFG가 아닌, 가능한 소스 클럭에 가깝게 적용해야 한다.

제약조건이 올바른지 확인

우리는 디자인 설정 단계 동안 사용할 수 있는 4가지 제약조건 검증 기법을 추천하고 있다. 검토할만한 가치가 있는 제약조건 점검 방식에 대한 아이디어를 제공하기 위해 Synplify 소프트웨어가 수행하고 있는 점검 방식을 살펴보자.

그림 1. 초기 Synplify 합성 입력 제약조건 파일은 기본적인 클럭 설정 및 I/O 제약조건 요건을 해결한다. 제약조건은 비바도 P&R 툴에도 명기되어진다.

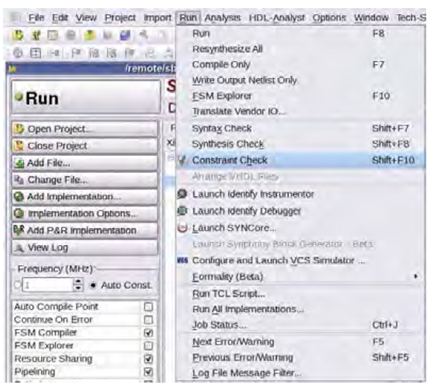

그림 2. 구문(Syntax)을 실행하고, 합성한 다음, 제약조건 검사를 통해 제약조건 및 클럭-설정의 파일럿 오류를 찾아내고, 타이밍 QoR을 신속하게 달성할 수 있다.

먼저, ‘syntax check’을 구동한다. 이는 제약조건의 구문 에러를 찾고 제거하기 위해 ‘get_XX’ 및 ‘all_XX’ 명령어를 포함하는 빠른 제약조건 확인 방법이다.

오류는 로그 파일에서 확인할 수 있으며, 오류를 설명하고, 해결방법을 제안하는오류 매뉴얼과 다시 하이퍼링크가 가능하다. Tcl명령어 check_fdc_query를 사용한다.

두 번째로 ‘synthesis check’를 구동한다. 이는 잘못 코딩된플립-플롭과 같은 하드웨어와 관련된 오류를 검출한다. 이러한 오류는 다른 별도의 로그 파일에서 리포트된다.

세 번째로 ‘fast synthesis’를 구동한다. 이는 명기된, 파생된, 추론된 클럭을 비롯해 클럭-설정 문제를 확인한다. 고속 합성은 클럭-설정 문제를 명확하게 만들어주는 클럭 리포트 및 타이밍 리포트를 생성하기 때문에 클럭-설정 확인을 수행할 수 있다.

특정 합성 툴은 고속 런타임을 위해 합성 최적화를 일부 중단시키는 ‘fast’ 모드로 합성을 실행할 수 있도록 해준다. Synplify Premier 합성 소프트웨어서는 다음과 같은 명령어를 이용하여 이를 실행할 수 있다:

set_option –fast_synthesis 1

합성 컴파일러는 클럭을 식별하고, 정의하고 제한하는데 사용할 수 있는 추론된 클럭 상의 정보를 포함하는 합성 단계의 클럭 리포트를 생성한다

네 번째로 풀 ‘constraints check’를 실행한다. 이 검사는 클럭 연관관계, 제약조건이 없는 시작/종료 포인트, lock되지 않은 I/O 및 제약조건이 없는 I/O에 대한 제약조건 설정 문제를 찾아낸다.

또한 풀 제약조건 검사는 올바른 애플리케이션 제약조건 및 예제의 이름을 확인한다. 예를 들어, 존재하지 않거나 실효성이 없는 타입의 인수나 객체에 적용된 타이밍 제약조건을 표시한다. 그런 다음, 툴은 제약조건 파일을 올바르게 정정하기 위해 발견되지 않은 예제나 적용할 수 없는 제약조건에 대한 상세한 검사 보고서를 생성한다. Synplify합성 툴은 합성의 사전 매핑 단계에서 이러한 종류의 검사를 자동으로 수행하거나, 다음과 같은 TCL 명령어를 이용해 합성의 시작 단계에서 제약조건 검사를 수행할 수 있다:

TCL: project -run constraint_check

이러한 기본 종류의 검사를 수행함으로써 합성 사이클의 초기 단계에서 오류를 확인하고, 품질 결과를 향상시킬 수 있다(그림 2 참조).

합성이 실행되고 나면, 합성 이후 타이밍 리포트를 반드시 분석해야 하는데, 이는 중요한 정보를 확인할 수 있기 때문이다. 예를 들어, Synplify 소프트웨어를 이용하는 경우, 타이밍 리포트의 시동-클럭 섹션 하의 ‘System Clock’은 제약조건이 설정되지 않은 일부 I/O들을 보여준다. 이 리포트의 인터페이스 정보를 통해 사실인지 아닌지를 확인할 수 있다.

2 단계: RTL 코딩 스타일 및 중요-경로 조정

타이밍을 더욱 향상시킬 수 있도록, 우리는 FSM(Finite State Machines)이나 RAM, 연산/DSP 기능, 클럭 트리, 쉬프트 레지스터를 위해 특정 코딩 스타일을 사용할 것을 권장한다 결과는 합성 툴이 FPGA 기본 빌딩 블록을 이용한 구현을 보다 뛰어나게 추론할 수 있기 때문에 타이밍 QoR을 향상시킨다.

또한 이러한 코딩 스타일은 추론된래치나 RAM용 읽기/쓰기 체크 로직, 그리고 DSP 요소 안으로 통합 가능한 로직과 같은 불필요한 로직 생성을 방지해 준다. 이러한 주제를 다룬 글들이 많은데, 고려할 만한 핵심 요지는 합성 툴 내의 코어-제너레이터기능을 이용하는 것이다. 예를 들어, Synplify 소프트웨어는 바이트-인에이블 RAM을 위해 필요한 RTL 코딩 스타일을 자동으로 생성하는 SynCore IP 위자드를 포함하고 있다. 또한 자일링스의 IP Catalog나 시놉시스의Synphony Model Compiler 및 DesignWarecoreTools, 그리고 DesignWare Building Blocks과 같은 다른 IP 제너레이터도 IP를 컨피규레이션하고, 여러 DSP 및 연산 기능을 수행하고, 뛰어난 RTL 코딩 스타일을 생성하는데 도움을 줄 수 있다. 만약 직접 코딩하는 경우라면, 다음과 같은 내용을 유의해야 한다:

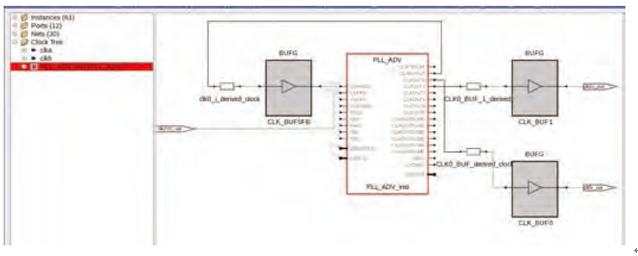

그림 3. 클럭트리를 정확하게 보여주는 스케매틱뷰어를 이용한 클럭 트리 및 클럭 제한조건 디버깅.

FSM(Finite State Machines)

•자일링스플로우의 경우, 동작 중에 하드웨어를 리셋하거나 전원을 켠 후 유효 상태로 하드웨어를 설정하기 위해 동기식리셋을 이용한다.

• 순차 블록을 조합식(Combinational-Always) 블록과 분리한다.

•모든 가능한 (현재의) 상태를 위해 차기-상태 변수를 할당한다.

블록 RAM

•일반적으로 보다 높은 클럭 주파수에서 동작하기 때문에 가능한 부분에서는 동기식 RAM을코딩

•넷리스트 레벨에서 보다 쉽게 디버깅할 수 있도록 RAM 코드를 별도의 모듈에 배치

• 특정 리셋 조건 및 듀얼 포트, 바이트-인에이블 RAM이나 비대칭 RAM이 포함된 RAM 사용을 결정하기 전에, 추천된 코딩 스타일을 검토하고, 추론화가 지원되는지를 확인한다. 만약 그렇지 않다면, 넷리스트는 결국 더 많은 제어 로직을 생성하게 될 것이다.

• 동일한 클럭 사이클로 쓰는동일한 어드레스에서 읽어오지 말자.

• 다른 모든 방법으로도 안된다면, 소형 RAM을 레지스터 안에 구현하도록 하는 속성(Synplify소프트웨어의 syn_ramstyle)을 이용한다. 이는 RAM 리소스를 보다 타이밍에 민감하고 더 큰 RAM에 사용할 수 있도록 해준다.

DSP 블록

아래 언급한 내용을 비롯해 카운터, 가산기, 곱셈기, 감산기와 같은 연산 기능들과 필터를 구현하기 위해 이러한 기초요소들을 사용할 수 있다.

•넷리스트 레벨에서 보다 쉽게 디버깅할 수 있도록 DSP 코드를 별도의 모듈에 배치

• 다른 모든 방법으로도 안된다면, 구현을 강제하도록 attribute(비바도 디자인 수트플로우에서Synplify를 위한 syn_dspstyle)을 이용한다.

SRL

쉬프트 레지스터를 자일링스 SRL primitive인 select_SRL 통합하거나 이를 레지스터에 구현할 수 있다.

•패킹은 자동으로 이뤄진다. 쉬프트 레지스터 체인의 경우, Synplify 소프트웨어는 타이밍QoR을 최적화기 위해 통합 외의 select_srl의 체인 상에 마지막 레지스터를 항상 남겨둔다.

• 다른 모든 방법으로도 안된다면, SRL 구현 방법을 제어하기 위해 syn_srlstyleattribute를 사용한다.

클럭 트리

• 이는 합성 중에 자동으로 추론화되지 않기 때문에, PLL(Phase Locked Loops), 클럭제너레이터, 클럭먹스를 RTL 안에 예시하는 것이 좋다.

• PLL의 입력 클럭 상의 타이밍 제약조건은 PLL 출력 핀 상의 파생 클럭 제약조건을 자동으로 생성한다.

클럭 제약조건을 보다 잘 검토하기 위해, 스케매틱뷰어에서 이를 확인한다. 예를 들어, Synplify의 HDL Analyst 툴은 클럭 트리 상에서 필터를 구동할 수 있으며, 이를 통해 클럭 트리 및 클럭 제약조건을 관찰하고 디버깅할 수 있다.

중요-경로의 성능을 향상시키기 위해 모듈 방식 사용

디자인 상의 특정 부분은 다른 부분에 비해 타이밍이 더욱 중요할 수 있으며, 실행되지 않는 부분들을 점진적으로 개선시키고 조정해야만 한다. RTL 및 넷리스트 단계에서 보다 빠르게 조정이 가능하도록 적용할 수 있는 한 가지 기법은 단일 블록 혹은 서브 프로젝트 내부에 중요 경로를 분리시키는 것이며, 그런 다음 이를 점진적으로 개선하기 위해 반복할 수 있다. 또한 비바도 P&R 툴을 이용해 타이밍 QoR을 유지할 수 있도록 가장 근접한 요소를 배치할 수 있다. 이러한 모듈 방식을 가능케 하는 합성 중에 여러분이 사용할 수 있는 기능들은 다음과 같다:

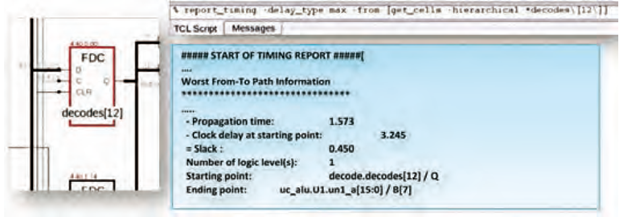

그림 4. 디자인의 특정 노드 상에서 타이밍 리포트를 생성할 수 있다.

• 합성 이전에 RTL 파티션을 명시(Synplify소프트웨어에서 이는 ‘compile point’라고 불린다)하거나 계층적으로 서브 프로젝트를 생성한다.

• 합성 후에 계층적 프로그램-관리 플로우를 이용해 실행되지 않는, 디자인의 한 부분에 해당하는 서브 프로젝트를 분리(내보냄)시킨다.

•합성 소프트웨어와 비바도 P&R 툴과 통신함으로써 크로스-SLR 지연을 피하기 위해 버텍스-7(Virtex®-7) 2000T FPGA와 같은 다중-SLR 디바이스의 동일한 다이 상에 중요 경로를 배치한다.

3 단계: 최종 타이밍 클로저 획득

대략적인 타이밍은 합성 후와 P&R 이후에 리포트가 가능하다.(그림 4 참조) 예를 들어, Synplify 소프트웨어는 TCL 명령어(report_timing)를 이용해 관심있는 디자인의 특정 부분에 대한 리포트가 가능하다.

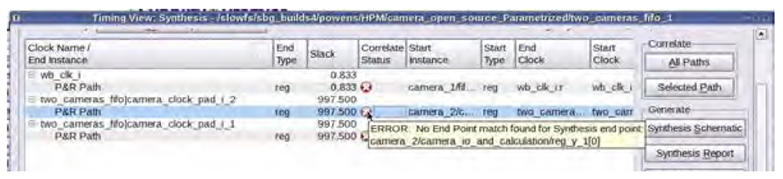

타이밍 QoR을 더욱 향상시키기 위해, 합성 후 및 P&R 후 타이밍 결과에 대한 연관성을 검토할 것을 권장하며, 타이밍이 중요한 경로 상의 특정 시작 포인트 및 엔드 포인트에 대한 슬랙 마진 또한 명확하게 하는 것이 좋다. 예를 들어, Synplify Premier 합성 소프트웨어에서 타이밍 결과를 판독하기 위해 합성 후 및 P&R 타이밍 리포트를 나란히 디스플레이 할 수 있다.

상관관계 툴은 엔드 포인트 및 시작 포인트, 그리고 필요한 period에 대한 상태를 나란히 비교한다. 경로는 엔드클럭 대비하여리포트된다. 사전 및 사후 P&R 타이밍이 명시된 ‘slack margin’ 기준 내에서 타당한 연관성이 없는 경로는 이에 대한 조치를 취할 수 있도록 ‘correlation mismatches’로 표시된다. 일반적인 조치로는 합성 단계에서만 타이밍-경로 제약조건을 더욱 엄격하게 하는 이른바 ‘-route’제약조건을 합성 툴에 규정하는 것이다.

합성을 위한 FDC 제약조건 입력 파일은 다음과 같다:

set_clock_route_delay {c:clka} 1.4

이러한 제약조건은 해당 경로에서 타이밍 성능을 달성하기 위해 합성을 더욱 자세하게 하여 보다 향상된 연관성 및 QoR을 달성한다.

타이밍 연관성 기능의 좋은 점은 문제를 유발하는 정확한 경로를 검토하기 위해 드릴 다운이 가능하다는 것이며, 예를 들어, 엔드 포인트마다 디스플레이되는 경로의 수를 변경할 수 있다. 또한 관심있는 특정 클럭이나 예제를 검색할 수 있으며, 이에 대한 타이밍 경로를 디스플레이할 수 있다. 클럭은 타이밍 연관성을 추가로 지원하기 위해 비교 및 디스플레이된다.

지금까지 살펴본 것처럼, 비바도 디자인 수트플로우에서 합리적인 시간으로 향상된 타이밍 성능을 달성하기 위해 취해야 할 여러 단계들이 있다. 우리가 개략적으로 설명한 방법론은 클럭이나 제약조건 설정 문제를 조기에 포착할 수 있으며, 또한 고속 타이밍 클로저를 얻기 위해 해당 디자인 및 RTL에서 타이밍을 조정하고, 연관성을 확인하기 위한 다양한 기법을 제공한다.

보다 자세한 정보 및 사례는 http://www.synopsys.com/fpga에서 확인할 수 있다.

그림 5. 타이밍 연관성 리포트는 합성 후 및 P&R 이후 타이밍 비매칭 여부를 비교할 수 있도록 해주며, 경로의 타이밍 결과와 클럭을 나란히 디스플레이하고 필터링한다.

- 적용분야 :

- Wireless Communications

- 관련제품 :

- EasyPath