Technical Article

제품 및 Tools

킨텍스 울트라스케일 FPGA로 다중-안테나 광대역 무선통신 과제 해결

킨텍스 울트라스케일 FPGA로 다중-안테나 광대역 무선통신 과제 해결

2014-09-01

글 : 데이비드 호크(David Hawke) / 무선 제품 마케팅 디렉터

이동통신 네트워크 사업자는 대역폭 확장과 MIMO 안테나 수 증가, 더 많은 셀 사이트와 새로운 전송 주파수를 통해 네트워크 커버리지 및 용량을 증대시킴으로써 상당한 장비 비용을 절감하고자 한다. 동시에 이러한 네트워크 사업자는 향상된 효율과 집적도를 제공하는 무선 장비를 채택함으로써 운영비용 절감을 추진하고 있다. 이러한 네트워크 사업자에게 무선 인프라 장비를 제공하는 제조업체들은 뛰어난 집적도와 높은 성능, 향상된 유연성을 제공하는 것은 물론, 낮은 전력소모와 저렴한 취득비용의 시스템-레벨 디자인 솔루션을 찾고 있다. 장비 제조업체는 이러한 모든 목표를 달성하는 것은 물론, 시장출시 시기도 단축할 수 있어야 한다.

전세계 여러 지역에서 진행 중인 TDD-LTE 및 FDD-LTE가 공개되면서, 이전에 발표된 무선 인터페이스와 비교해 요구되는 장비의 특성 및 성능 요건이 달라지고 있다.

CDMA2000 및 WCDMA 3G에 사용되었던 가장 일반적인 컨피규레이션은 20MHz 2x2 무선이었지만, 이 컨피규레이션은 오래 전에 더 넓은 광대역을 제공하고, 보다 많은 주파수 대역을 지원하는 컨피규레이션으로 진화했다. 제조업체들은 이제 100MHz의 사용 가능한 대역폭을 제공할 수 있는 MIMO 무선 통신을 일반적으로 개발하고 있다. 이러한 새로운 컨피규레이션은 보통 4x4 및 8x8 MIMO 안테나 어레이를 채택하고 있다.

초광대역 무선 통신이 개발되면서 네트워크 사업자는 하나의 무선으로 여러 관심 주파수 대역, 즉 1800MHz, 1900MHz, 혹은 미래의 2100MHz까지도 지원할 수 있게 되었으며, 이로 인해 타워의 꼭대기에 탑재되는 원격 무선 수도 줄이고, 비용도 절감할 수 있게 되었다. 이러한 발전은 더 적은 무선을 사용함으로써 자본설비 비용을 상당히 절감시켜줄 뿐만 아니라, 풍력하중 감소 및 타워의 총 중량하중 감소로 운영비용 및 사이트-렌탈 비용도 크게 줄일 수 있다.

100MHz 8x8 무선은 20MHz 2x2 무선에 비해 20배 이상의 신호 처리가 필요하다. 이러한 무선 장비의 디지털 및 아날로그 프로세싱 요건을 고려할 때, 수동적으로 냉각되는 원격 무선에서 요구되는 기계적, 열적 및 비용 제한조건에 부합하면서도, 이를 실현할 수 있는 제품을 찾는다는 것은 쉬운 일이 아니다. 다시 말해, 차세대 디지털 및 아날로그 IC의 지속적인 발전이 요구된다.

예를 들어, 100MHz 8x8 무선 구현을 위한 시스템 레벨의 요건을 생각해보자.

8x8 셀룰러 무선에서 필요한 FPGA 디바이스 규모를 정의하기 위해서는 안테나 수와 무선 인터페이스, 캐리어 수 및 순시 대역폭(Instantaneous Bandwidth) 등이 고려되어야 한다. 안테나 수는 필요한 DAC 및 ADC 커넥션 수를 규정하게 된다. 무선 순시 대역폭은 샘플 레이트를 규정하기 때문에 FPGA의 디지털 신호 처리 블록과 DAC 및 ADC를 연결하기 위해 필요한 SerDes 포트의 속도 및 수를 정하게 된다.

데이터 컨버터는 여러 제조업체를 통해 지난 수년 동안 획기적으로 발전해 왔으며, 이제는 JESD2 04B를 통해 디지털 무선 프로세싱 회로와 연결된 다중 DAC 및 ADC를 단일 패키지 안에 제공할 수 있게 되었다. JESD204B 인터페이스 표준은 이전에 사용되었던 LVDS 병렬 인터페이스를 12.5Gbps로 구동할 수 있는 고속 SerDes 포트로 대체하고 있다.

JESD204B 인터페이스는 DAC 및 ADC와 디지털 프론트 엔드 프로세싱 회로 간의 필요한 커넥션 수를 상당히 줄여준다. 그 결과 PCB 레이어가 줄어들고, 인터페이스 전력소모도 절감되었다. 또한 이러한 JESD204B 컨버터는 이전 보다 더 많은 집적도를 보이면서, 업링크 및 다운링크 RF-프로세싱 서브시스템 전반을 처리하고 있으며, 고도로 집적된 고성능 AFE(Analog Front End)를 구현하는데 필요한 모듈레이터 및 DAC, ADC, 필터링을 포함한 고성능 RF IC가 되어가고 있다.

또한 필요한 SerDes 트랜시버의 수를 결정하는 것과 더불어, 셀룰러 무선 대역폭 및 안테나 수는 DUC(Digital Up Conversion) 및 DDC(Digital Down Converter)를 비롯한 프로세싱 알고리즘에 필요한 로직 및 DSP의 양을 좌우한다. DUC 및 DDC 알고리즘은 네트워크 사업자들이 필요에 따라 하드웨어를 변경하지 않고도 알고리즘을 수정할 수 있기 때문에 FPGA 구현에 매우 적합하다. 이외의 범용으로 사용되고 있는 두 가지 알고리즘은 CFR(Crest Factor Reduction) 및 DPD(Digital Pre-Distortion)로, 무선 출력 파워 앰프의 효율을 향상시킨다.

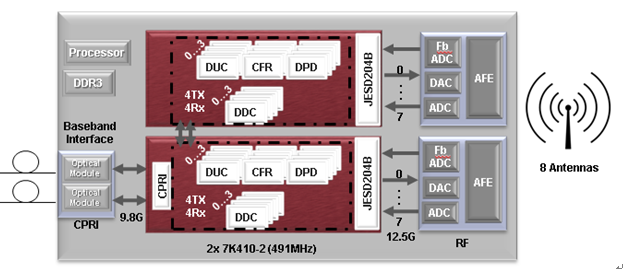

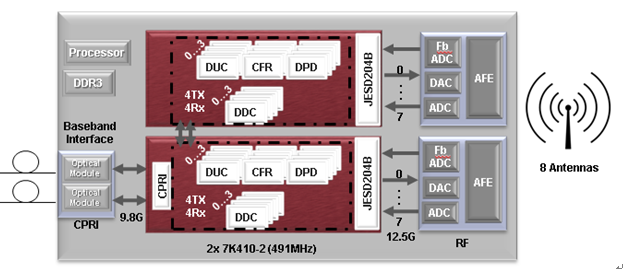

8개의 안테나와 통신하는데 필요한 SerDes 수와 광대역 무선을 구현하는데 필요한 DSP 리소스 기반의 현 세대 자일링스 FPGA를 이용한 셀룰러 무선 구현의 비용 효과적인 방법은 두 디바이스 간의 알고리즘 프로세싱을 분리하는 것이다(그림 1 참조). 이러한 시스템 파티셔닝은 2개의 4x4 100MHz 무선을 효과적으로 만들 수 있다. 이러한 파티셔닝이 이뤄진 제품은 두 개의 디지털 디바이스 전반에 동작 전압을 균등하게 분산시키고, 열 제한조건을 용이하게 하며, 디자인 메커니즘을 간소화할 수 있다.

그림 1 .두 개의 킨텍스-7 FPGA를 이용한 100MHz 8x8 무선 구현의 예

하지만 이러한 시스템 레벨의 파티셔닝은 보다 뛰어난 DSP 성능과 훨씬 많은 SerDes 포트 수를 가지고 있고, 전력소모는 획기적으로 낮아진 자일링스 킨텍스(Kintex) 울트라스케일(UltraScale) 디바이스를 사용하면 더 이상 필요하지 않다.

실제로 울트라스케일 아키텍처는 이러한 형태의 무선 디자인 요건에 잘 부합한다. 울트라스케일 아키텍처의 매우 효율적인 블록 RAM 및 LUT(Look Up Table) RAM, 그리고 최적화된 DSP48E2 DSP 블록은 DUC, DDC, CFR, DPD 신호 처리를 위해 필요한 수많은 형태의 필터를 생성할 수 있도록 효율적으로 결합되어 있다. 울트라스케일 아키텍처의 프로그래머블 로직 패브릭 및 온칩 메모리는 DPD 프로세싱을 위한 매우 확장성이 있으면서 로직을 적게 사용하는 계수 연산용 하드웨어 가속기와 함께 사용이 가능한 고성능의 소프트 마이크로프로세서를 구현할 수 있다.

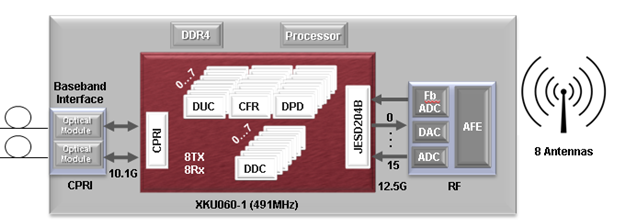

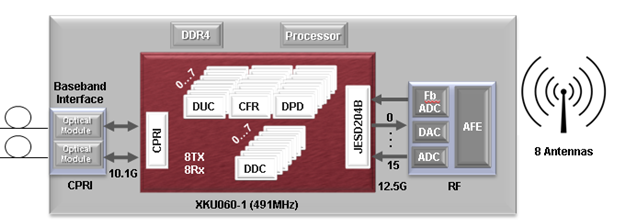

울트라스케일 FPGA는 491MHz를 초과하는 클럭 레이트를 달성할 수 있으며, FPGA 기반 무선 디자인의 낮은 전력소모를 유지하면서도 신호 처리에 소요되는 온칩 영역을 더욱 줄이기 위해 TDM(Time-Division Multiplexing)을 활용할 수 있도록 해준다. 따라서 100MHz 8x8 무선은 하나의 킨텍스 울트라스케일 FPGA 만으로도 구현이 가능하다(그림 2 참조).

그림 2.하나의 킨텍스 울트라스케일 FPGA로 구현된 뛰어난 100MHz 8x8 무선

이러한 복잡한 무선을 단일 디바이스에 구현하기 위해서는 열 발생이 감소되도록 전반적인 동작전압을 크게 낮춰야 한다. 자일링스 울트라스케일 아키텍처 기반 FPGA는 여러 방법을 통해 저전력 동작에 최적화되어 있다. 먼저, 두 개의 28nm FPGA의 정적 전력소모는 단 하나의 20nm FPGA로 대체 가능하다. 그림 2에 나타낸 하나의 FPGA 디바이스는 동일한 채널 수를 구현하면서도 그림 1에 나타낸 두 개의 FPGA보다 전력소모가 더 적다.

또한 세밀한 디자인을 통해 디바이스의 프로그래머블 로직 패브릭 및 SerDes 트랜시버의 동적 전력소모를 상당히 줄일 수 있다. 복잡한 MAC(Multiply/Accumulate) 연산을 기반으로 한 디지털 필터 구현을 위해 필요한 DSP 블록들을 줄일 수 있다. 필요한 DSP 블록 수를 줄임으로써 DUC, DDC, CFR, DPD 알고리즘을 구현하는데 필요한 공간 및 동적 전력소모를 줄일 수 있다.

이러한 시스템 레벨 디자인은 이전 세대의 디바이스에 비해 송수신 페어 당 8%의 비용 절감이 가능하고, 전력소모는 31% 이상 줄일 수 있다. 또한 필요한 PCB 레이어 수가 감소되고, 전력망의 복잡도가 줄어들면서 추가로 시스템 레벨 비용을 절감할 수 있다. 이와 더불어 보다 적은 전력망과 쿨링 하드웨어의 복잡도 감소 및 소형화는 원격 무선 시스템의 무게 및 필요한 인클로저 사이즈를 줄일 수 있으며, 이를 통해 BOM 및 운영비용을 추가로 절감할 수 있다.

요약

네트워크 사업자는 점점 더 낮은 동작전압과 높은 안정성을 갖춘 저비용의 뛰어난 성능의 무선 인프라 장비를 요구하고 있다. 이러한 모든 목표를 달성할 수 있는 핵심은 통합이다. 위의 사례에서 보았듯이, 더 큰 보드 공간과 더 많은 동작전압을 소모하는 다중 디바이스로만 구현이 가능한 최신의 초광대역 MIMO 무선은 이제 보다 새로워진 FPGA 디바이스 제품군을 통해 보다 효율적으로 구현할 수 있게 되었다.

이동통신 네트워크 사업자는 대역폭 확장과 MIMO 안테나 수 증가, 더 많은 셀 사이트와 새로운 전송 주파수를 통해 네트워크 커버리지 및 용량을 증대시킴으로써 상당한 장비 비용을 절감하고자 한다. 동시에 이러한 네트워크 사업자는 향상된 효율과 집적도를 제공하는 무선 장비를 채택함으로써 운영비용 절감을 추진하고 있다. 이러한 네트워크 사업자에게 무선 인프라 장비를 제공하는 제조업체들은 뛰어난 집적도와 높은 성능, 향상된 유연성을 제공하는 것은 물론, 낮은 전력소모와 저렴한 취득비용의 시스템-레벨 디자인 솔루션을 찾고 있다. 장비 제조업체는 이러한 모든 목표를 달성하는 것은 물론, 시장출시 시기도 단축할 수 있어야 한다.

전세계 여러 지역에서 진행 중인 TDD-LTE 및 FDD-LTE가 공개되면서, 이전에 발표된 무선 인터페이스와 비교해 요구되는 장비의 특성 및 성능 요건이 달라지고 있다.

CDMA2000 및 WCDMA 3G에 사용되었던 가장 일반적인 컨피규레이션은 20MHz 2x2 무선이었지만, 이 컨피규레이션은 오래 전에 더 넓은 광대역을 제공하고, 보다 많은 주파수 대역을 지원하는 컨피규레이션으로 진화했다. 제조업체들은 이제 100MHz의 사용 가능한 대역폭을 제공할 수 있는 MIMO 무선 통신을 일반적으로 개발하고 있다. 이러한 새로운 컨피규레이션은 보통 4x4 및 8x8 MIMO 안테나 어레이를 채택하고 있다.

초광대역 무선 통신이 개발되면서 네트워크 사업자는 하나의 무선으로 여러 관심 주파수 대역, 즉 1800MHz, 1900MHz, 혹은 미래의 2100MHz까지도 지원할 수 있게 되었으며, 이로 인해 타워의 꼭대기에 탑재되는 원격 무선 수도 줄이고, 비용도 절감할 수 있게 되었다. 이러한 발전은 더 적은 무선을 사용함으로써 자본설비 비용을 상당히 절감시켜줄 뿐만 아니라, 풍력하중 감소 및 타워의 총 중량하중 감소로 운영비용 및 사이트-렌탈 비용도 크게 줄일 수 있다.

100MHz 8x8 무선은 20MHz 2x2 무선에 비해 20배 이상의 신호 처리가 필요하다. 이러한 무선 장비의 디지털 및 아날로그 프로세싱 요건을 고려할 때, 수동적으로 냉각되는 원격 무선에서 요구되는 기계적, 열적 및 비용 제한조건에 부합하면서도, 이를 실현할 수 있는 제품을 찾는다는 것은 쉬운 일이 아니다. 다시 말해, 차세대 디지털 및 아날로그 IC의 지속적인 발전이 요구된다.

예를 들어, 100MHz 8x8 무선 구현을 위한 시스템 레벨의 요건을 생각해보자.

8x8 셀룰러 무선에서 필요한 FPGA 디바이스 규모를 정의하기 위해서는 안테나 수와 무선 인터페이스, 캐리어 수 및 순시 대역폭(Instantaneous Bandwidth) 등이 고려되어야 한다. 안테나 수는 필요한 DAC 및 ADC 커넥션 수를 규정하게 된다. 무선 순시 대역폭은 샘플 레이트를 규정하기 때문에 FPGA의 디지털 신호 처리 블록과 DAC 및 ADC를 연결하기 위해 필요한 SerDes 포트의 속도 및 수를 정하게 된다.

데이터 컨버터는 여러 제조업체를 통해 지난 수년 동안 획기적으로 발전해 왔으며, 이제는 JESD2 04B를 통해 디지털 무선 프로세싱 회로와 연결된 다중 DAC 및 ADC를 단일 패키지 안에 제공할 수 있게 되었다. JESD204B 인터페이스 표준은 이전에 사용되었던 LVDS 병렬 인터페이스를 12.5Gbps로 구동할 수 있는 고속 SerDes 포트로 대체하고 있다.

JESD204B 인터페이스는 DAC 및 ADC와 디지털 프론트 엔드 프로세싱 회로 간의 필요한 커넥션 수를 상당히 줄여준다. 그 결과 PCB 레이어가 줄어들고, 인터페이스 전력소모도 절감되었다. 또한 이러한 JESD204B 컨버터는 이전 보다 더 많은 집적도를 보이면서, 업링크 및 다운링크 RF-프로세싱 서브시스템 전반을 처리하고 있으며, 고도로 집적된 고성능 AFE(Analog Front End)를 구현하는데 필요한 모듈레이터 및 DAC, ADC, 필터링을 포함한 고성능 RF IC가 되어가고 있다.

또한 필요한 SerDes 트랜시버의 수를 결정하는 것과 더불어, 셀룰러 무선 대역폭 및 안테나 수는 DUC(Digital Up Conversion) 및 DDC(Digital Down Converter)를 비롯한 프로세싱 알고리즘에 필요한 로직 및 DSP의 양을 좌우한다. DUC 및 DDC 알고리즘은 네트워크 사업자들이 필요에 따라 하드웨어를 변경하지 않고도 알고리즘을 수정할 수 있기 때문에 FPGA 구현에 매우 적합하다. 이외의 범용으로 사용되고 있는 두 가지 알고리즘은 CFR(Crest Factor Reduction) 및 DPD(Digital Pre-Distortion)로, 무선 출력 파워 앰프의 효율을 향상시킨다.

8개의 안테나와 통신하는데 필요한 SerDes 수와 광대역 무선을 구현하는데 필요한 DSP 리소스 기반의 현 세대 자일링스 FPGA를 이용한 셀룰러 무선 구현의 비용 효과적인 방법은 두 디바이스 간의 알고리즘 프로세싱을 분리하는 것이다(그림 1 참조). 이러한 시스템 파티셔닝은 2개의 4x4 100MHz 무선을 효과적으로 만들 수 있다. 이러한 파티셔닝이 이뤄진 제품은 두 개의 디지털 디바이스 전반에 동작 전압을 균등하게 분산시키고, 열 제한조건을 용이하게 하며, 디자인 메커니즘을 간소화할 수 있다.

그림 1 .두 개의 킨텍스-7 FPGA를 이용한 100MHz 8x8 무선 구현의 예

하지만 이러한 시스템 레벨의 파티셔닝은 보다 뛰어난 DSP 성능과 훨씬 많은 SerDes 포트 수를 가지고 있고, 전력소모는 획기적으로 낮아진 자일링스 킨텍스(Kintex) 울트라스케일(UltraScale) 디바이스를 사용하면 더 이상 필요하지 않다.

실제로 울트라스케일 아키텍처는 이러한 형태의 무선 디자인 요건에 잘 부합한다. 울트라스케일 아키텍처의 매우 효율적인 블록 RAM 및 LUT(Look Up Table) RAM, 그리고 최적화된 DSP48E2 DSP 블록은 DUC, DDC, CFR, DPD 신호 처리를 위해 필요한 수많은 형태의 필터를 생성할 수 있도록 효율적으로 결합되어 있다. 울트라스케일 아키텍처의 프로그래머블 로직 패브릭 및 온칩 메모리는 DPD 프로세싱을 위한 매우 확장성이 있으면서 로직을 적게 사용하는 계수 연산용 하드웨어 가속기와 함께 사용이 가능한 고성능의 소프트 마이크로프로세서를 구현할 수 있다.

울트라스케일 FPGA는 491MHz를 초과하는 클럭 레이트를 달성할 수 있으며, FPGA 기반 무선 디자인의 낮은 전력소모를 유지하면서도 신호 처리에 소요되는 온칩 영역을 더욱 줄이기 위해 TDM(Time-Division Multiplexing)을 활용할 수 있도록 해준다. 따라서 100MHz 8x8 무선은 하나의 킨텍스 울트라스케일 FPGA 만으로도 구현이 가능하다(그림 2 참조).

그림 2.하나의 킨텍스 울트라스케일 FPGA로 구현된 뛰어난 100MHz 8x8 무선

이러한 복잡한 무선을 단일 디바이스에 구현하기 위해서는 열 발생이 감소되도록 전반적인 동작전압을 크게 낮춰야 한다. 자일링스 울트라스케일 아키텍처 기반 FPGA는 여러 방법을 통해 저전력 동작에 최적화되어 있다. 먼저, 두 개의 28nm FPGA의 정적 전력소모는 단 하나의 20nm FPGA로 대체 가능하다. 그림 2에 나타낸 하나의 FPGA 디바이스는 동일한 채널 수를 구현하면서도 그림 1에 나타낸 두 개의 FPGA보다 전력소모가 더 적다.

또한 세밀한 디자인을 통해 디바이스의 프로그래머블 로직 패브릭 및 SerDes 트랜시버의 동적 전력소모를 상당히 줄일 수 있다. 복잡한 MAC(Multiply/Accumulate) 연산을 기반으로 한 디지털 필터 구현을 위해 필요한 DSP 블록들을 줄일 수 있다. 필요한 DSP 블록 수를 줄임으로써 DUC, DDC, CFR, DPD 알고리즘을 구현하는데 필요한 공간 및 동적 전력소모를 줄일 수 있다.

이러한 시스템 레벨 디자인은 이전 세대의 디바이스에 비해 송수신 페어 당 8%의 비용 절감이 가능하고, 전력소모는 31% 이상 줄일 수 있다. 또한 필요한 PCB 레이어 수가 감소되고, 전력망의 복잡도가 줄어들면서 추가로 시스템 레벨 비용을 절감할 수 있다. 이와 더불어 보다 적은 전력망과 쿨링 하드웨어의 복잡도 감소 및 소형화는 원격 무선 시스템의 무게 및 필요한 인클로저 사이즈를 줄일 수 있으며, 이를 통해 BOM 및 운영비용을 추가로 절감할 수 있다.

요약

네트워크 사업자는 점점 더 낮은 동작전압과 높은 안정성을 갖춘 저비용의 뛰어난 성능의 무선 인프라 장비를 요구하고 있다. 이러한 모든 목표를 달성할 수 있는 핵심은 통합이다. 위의 사례에서 보았듯이, 더 큰 보드 공간과 더 많은 동작전압을 소모하는 다중 디바이스로만 구현이 가능한 최신의 초광대역 MIMO 무선은 이제 보다 새로워진 FPGA 디바이스 제품군을 통해 보다 효율적으로 구현할 수 있게 되었다.

- 태그 :

- TDD-LTE,MIMO,Kintex,Virtex,Ultrascale

- 적용분야 :

- Wireless Communications

- 관련제품 :

- MicroBlaze, UltraScale, Kintex-7