Technical Article

제품 및 Tools

자일링스의 울트라패스트(UltraFast) 디자인 방법론: 차세대 디자인 혁신을 실현하는 새로운 생산성 공식

자일링스의 울트라패스트(UltraFast) 디자인 방법론: 차세대 디자인 혁신을 실현하는 새로운 생산성 공식

2014-02-01

글/ 마이크 산타리니(Mike Santarini), 자일링스 Xcell 저널 발행인

지난 40년동안 IC 공정 기술의 지속적인 발전은 오늘날 우리 모두가 향유하고 있는 수많은 전자 제품들을 현실화하는데 기여했다. 하지만 이러한 실리콘 공정 기술의 진화가 전자제품의 혁신에 결정적으로 기여한 반면, 동시에 툴을 발전시키기 위한 학계 및 EDA 업계의 노력이 없었다면 불가능했을 것이다. 1970년대의 트랜지스터-레벨 SPICE 시뮬레이션에서 오늘날의 수십억-게이트 시스템 레벨의 첨단 통합 디자인 환경에 이르기까지의 진화는 정말 놀라운 일이다. 또한 이와 더불어 주목할 것은 전자산업의 혁신에 본질적으로 기여하고 있지만 종종 간과되기 쉬운 디자인 방법론이다.

디자인 팀은 세계에서 가장 진보된 실리콘과 세계에서 가장 뛰어난 툴을 활용할 수 있게 되었지만, 이 그룹이 견고한 방법론을 수립하지 못한다면, 제품을 적기에 출시하고, 이를 사업적 성공으로 이끌기는 어려울 것이다. 뛰어난 디자인 방법론은 디자인 팀이 고품질의 제품을 적시에 출시할 수 있도록 개발시간을 단축하는 것은 물론, 장기적인 사업 성공에 있어 매우 중요한 예측 가능하고 안정적인 방법으로 이를 수행할 수 있도록 해준다. 이는 곧, 진화하는 실리콘과 디자인 툴의 혜택을 얻기 위해서는 방법론을 지속적으로 발전시켜야 함을 의미한다.

디자인 플로우 초반에 클로저 시작

- 반복 작업 감소

- QoR(Quality of Results)에 대한 상당한 영향

- 반복 작업 감소

- QoR(Quality of Results)에 대한 상당한 영향

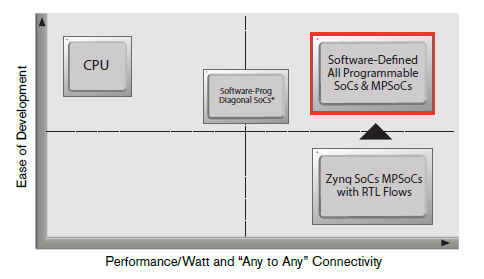

그림 1. 플로우 초반에 클로저를 달성함으로써 획기적으로 QoR(Quality of Results)을 향상시키고 디자인 시간을 단축할 수 있다.

자일링스는 자일링스의 28nm 7시리즈 및 20/16nm 울트라스케일(UtraScale™) 제품군의 디자인을 구현하기 위해 수상 경력이 있는 비바도(Vivado®) 디자인 수트를 사용하는 디자인 팀들이 차세대 혁신을 달성하는데 있어 보다 생산적이고 성공적으로 수행할 수 있도록 울트라패스트(UltraFast™) 디자인 방법론을 출시했다.

자일링스의 비바도 디자인 수트 제품 마케팅 디렉터인 라민 론(Ramine Roane)은 “이 새로운 방법론은 근본적인 변화를 의미하는 것은 아니며, 오히려 울트라패스트는 업계 전문가들로부터 최상의 실행 사례들을 신중하게 선택한 것으로, 디자인 팀이 예측 가능한 성과를 보다 빠르게 구현할 수 있도록 이러한 실행 사례들을 강력한 방법론으로 응축한 것”이라고 설명했다. 또한 “이러한 최상의 실행 사례들은 보드 플래닝, 디자인 생성, 디자인 구현 및 클로저, 프로그래밍 및 하드웨어 디버깅의 모든 측면을 커버하고 있다.”고 덧붙였다.

라민 론 디렉터는 “울트라패스트 디자인 방법론은 디자인 팀이 생산성을 가속화하고, 디자인을 안정적으로 보다 빠르게 구현하고, 스케쥴을 예측함으로써 제품 출시시기를 앞당길 수 있도록 비바도 디자인 수트 및 자일링스 올 프로그래머블(All Programmable) 디바이스의 최신 기술의 혜택을 온전히 활용할 수 있도록 해줄 것이다.”고 밝혔다.

울트라패스트 방법론은 자일링스가 경쟁사 대비 어떻게 세대를 앞서나가고 있는지를 보여주는 또 다른 사례이다. 자일링스는 최상의 디바이스와 최신 툴 수트는 물론, 업계에서 가장 포괄적인 방법론을 보유하고 있다.

울트라패스트 디자인 방법론의 적용을 보다 빠르게 확산시키기 위해, 자일링스는 무료 방법론 매뉴얼을 출간했다. ‘비바도 디자인 수트를 위한 울트라패스트 방법론 가이드(The UltraFast Methodology Guide for the Vivado Design Suite (UG949))’는 보드 선택 및 RTL 디자인에서 구현 및 최종 디버깅에 이르기까지 전반적인 방법론을 단계별로 설명하고 있다. 이 문서에는 디자인 플로우 전반에 걸쳐 엔지니어를 가이드하기 위해 설계된 포괄적인 체크리스트가 포함되어 있다. 또한 비바도 디자인 수트 2013.3 릴리스는 린팅(Linting)을 비롯한 이 방법론의 상당 부분을 자동화하고 있으며, ‘방법론(Methodology)’ 및 ‘타이밍(Timing)’이라는 타이틀로 새로운 DRC 룰 체크가 추가되었다. 또한 비바도 디자인 수트의 새로운 버전은 합성 및 구현을 위한 구조적 최적화로 QoR(Quality of Results)을 가능하게 하는 HDL 및 XDC 탬플릿을 포함하고 있다. 한편 자일링스는 셀프-트레이닝을 위한 무료 온라인 비디오 시리즈를 비롯해 전세계 여러 지역에서 공식 트레이닝 과정을 제공하고 있다.

빠른 컨버전스를 위한 디자인 방법론

론은 울트라패스트 방법론의 주요 과제는 결과 품질에 상당한 영향을 미치는 디자인 플로우 전반에서 디자인 클로저를 제공하는 것이라고 밝혔다.(그림 1 참조) 또한 이 방법을 통해 디자인 팀은 구조적으로 오류를 제거한 디자인에 신속하게 컨버전스를 할 수 있다. 론은 “플로우 레벨 초기에 의사결정을 할 수 있다면, 구현 단계의 상당히 많은 사이클을 효과적으로 제거할 수 있을 것”이라고 설명했다.

론은 이 프로세스는 비바도 디자인 수트를 통해 가능하다며, 비바도 디자인 수트는 프로그래머블 업계에서 유일하게 각 플로우 단계 및 디자인 엔트리의 시작에서 IP 통합, 그리고 RTL 합성 및 구현(최적화, 배치, 물리층 최적화, 라우팅)에 이르기까지 계속해서 소스에 대한 인터랙티브 디자인 분석 및 크로스-프로빙(Cross-Probing)이 가능한 툴이라고 설명했다. 또한 론은 “기존 툴은 오직 완벽하게 구현된 플로어플랜의 프로세스 마지막에 문제를 발견할 수 있을 뿐”이라고 지적하고, “만약 이 디자인이 예상대로 동작하지 않는다면, 문제원인에 대한 최소한의 단서만을 가지고 다시 처음 디자인 단계로 돌아가는 것 말고는 다른 선택이 없으며, 길고 지루한 루프가 반복되게 될 것”이라고 언급했다.

이 크로스-프로빙 및 분석 기능을 가능하게 하는 것은 비바도 디자인 수트의 통일된 데이터 모델이다. 론은 “통일된 데이터 모델은 디자인 팀이 전체 플로우 전반에 걸쳐 동일한 분석 및 클로저 루틴을 사용할 수 있게 해준다.”며, “기존 디자인 수트 대비 가장 큰 장점은 엔지니어들이 어떠한 문제 지점이라도 원래의 소스나 다른 디자인 뷰와의 크로스-프로브를 하거나, 심지어 인-메모리를 비롯한 여러 단계에서 디자인을 수정할 수 있다는 점이다. 자일링스는 이 통일된 데이터 모델이 수백만 로직 셀의 하이-엔드 디바이스까지 확장되도록 설계한 반면, 경쟁사 툴은 미드레인지 디바이스에서도 이미 오류가 나기 시작했다.”고 언급했다.

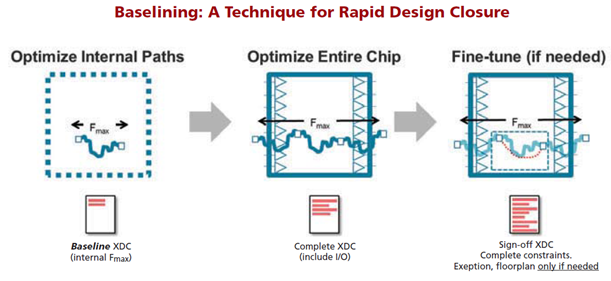

울트라패스트 방법론의 고속 디자인 컨버전스를 가장 잘 보여주는 사례는 아마도 ‘기준설정(Baselining)’ 컨셉일 것이다.

이밍 클로저에서 신속한 컨버전스를 위한 기준설정

론은 ‘기준설정(Baselining)’은 10번 중 9번은 가장 큰 문제가 되는 내부의 Fmax에 초점을 두어 디자인 컨버전스를 가속화하는데 사용하는 기법이라며, “이는 사용자나 툴을 잘못된 방향으로 유도하는 복잡하고 오류 발생이 매우 심한 I/O 제약 및 타이밍 예외조건으로 낭비되는 시간을 방지할 수 있다.”고 설명했다. 또한 “기준설정을 통해 디자인 팀은 매우 간단한 제약조건 및 플립-플롭 경로에 초점을 두어 컨버전스 프로세스를 시작할 수 있다. 그런 다음 문제가 클럭 경로 혹은 데이터 경로이든, 인터커넥트 지연 혹은 로직 지연이든 상관없이 문서화된 해결방안을 적용하고, 다시 분석을 수행할 수 있다.”고 말했다.

디자인 팀이 기준이 되는 XDC로 타이밍을 클로징하고 나면, 거의 완료된 것이다. 그런 다음 I/O 인터페이스 제약조건을 추가해야 한다. 론은 “잘못된 타이밍 문제가 생성되지 않도록 하기 위해서는 이러한 제약조건이 올바르게 유지되도록 하는 것이 중요하다.”고 지적했다.

론은 “이는 우리가 소스-동기화, 중앙집중형 DDR I/O 제약조건과 같은 XDC 탬플릿을 제공하는 이유다. 필요하면 제약조건은 타이밍 예외조건으로 미세조정이 가능하며, 약간의 플로어플래닝도 가능하다. 하지만 해당 경로가 중요하지 않다면, 예외조건이 유용하지 않다는 점도 주의해야 한다. 이와 비슷하게 오버플로어플래닝 디자인은 오히려 더 해가 될 수 있다.”고 언급했다.

론은 하지만 기준설정은 사인-오프 제약조건을 대체하는 것은 아니라며, “완벽한 제약조건에 따른 디자인 검증은 반드시 필요하다.”고 밝혔다.

또한 울트라패스트 방법론은 온전한 최종 constraints에 이르는 단계를 상세하게 묘사하고 있다. 비바도는 타이밍 경로 및 클럭 네트워크, 클럭들 간의 상호작용 등을 분석하기 위해 수많은 배치(Batch) 및 그래픽 루틴으로 이러한 작업을 자동화하고 있다. 또한 새로운 타이밍 DRC 룰 데크는 디자인의 제약조건 및 클럭 네트워크 린팅을 위해 사용될 수 있다.

기준설정(Baselining): 고속 디자인 클로저 기법

그림 2. 기준설정(Baselining)으로 디자인 팀은 타이밍 클로저를 신속하게 달성할 수 있다.

비바도 디자인 수트를 위한 울트라패스트 방법론 가이드

울트라패스트 방법론에 익숙해지기 위해 가장 먼저 시작할 것은 ‘비바도 디자인 수트를 위한 울트라패스트 방법론 가이드’를 읽는 것이다. 이 가이드는 6장으로 구성되어 있으며, 첫 번째와 두 번째 장은 가이드 목차 및 추천 디자인 수트 플로우가 소개되어 있다. 3장에서 6장까지는 울트라패스트 방법론의 가장 뛰어난 사례들을 심도 깊게 설명하고 있다.

3장은 보드 및 디바이스 플래닝을 다루고 있으며, PCB 레이아웃과 클럭 리소스 플래닝 및 할당, I/O 플래닝 디자인 플로우, FPGA 전력 측면 및 시스템 의존성 등에 대한 적절한 권고사항을 제공하고 있다. 보드 리스핀을 피하기 위해, 이 방법론은 할당된 전력 한계치에 부합하는 아키텍처를 분석하고 찾기 위해 자일링스의 PE(Power Estimator) 사용법 개요를 설명하고 있다.

또한 이 장에서는 뛰어난 I/O 플래닝으로 디자인 프로젝트를 시작하는 것이 얼마나 중요한지를 강조하고 있으며, 보드 플래닝과 함께, 혹은 최소한 보조를 맞춰 수행하도록 권고하고 있다. I/O 및 보드 플래닝 조정이 실패하면, 프로세스 후반의 시스템 레벨에서 타이밍 및 전력 분배 문제가 발생할 수 있다. 이 장은 또한 다양한 전력 모드와 전력 및 열 분석을 위한 권고사항은 물론, PCB 냉각에 대한 고려사항을 다루고 있다. 또한 디자인 프로젝트에서 자일링스 올 프로그래머블 3D IC를 구현하는 경우, 이러한 멀티다이 디바이스와 연결되는 인터포저는 고유의 요구조건을 가지고 있기 때문에 I/O 권고사항을 제시하고 있다.

4장은 ‘디자인 생성(Design Creation)’으로, 견고한 디자인 계층 생성 및 해당 디자인에 적합한 IP 선택을 위한 전략 및 팁을 제시하며, 실용적인 RTL 코딩 가이드라인을 여러 섹션에 걸쳐 소개하고 있다. 신호 및 세트 제어, RAM 및 ROM 추론, 적절한 DSP 및 연산 추론 코딩, 쉬프트 레지스터 및 지연 라인 코딩, 모든 추론된 레지스터 및 SRL, 메모리에 대한 초기화 섹션이 포함되어 있다. 이 장은 파라미터 특성 및 제약조건에 대한 섹션은 물론, 클럭킹 및 예시, 추론에 대한 섹션도 포함하고 있다.

론은 “여러분이 HDL을 작성하는 방법은 합성으로 로직을 추론하는 방법과 크게 다를 수 있다.”며, “좋은 코딩 방법은 해당 디자인을 아키텍처의 하드 블록에 적용할 수 있기 때문에 보다 높은 주파수로 동작이 가능하다. 고객들이 이러한 리소스를 최대한 활용하고, 전반적인 디자인을 가속화할 수 있도록, 특히 RAM 및 쉬프트 레지스터, DSP 리소스의 컴포넌트를 추론할 수 있는 탬플릿을 포함하고 있다. 이러한 탬플릿은 비바도 디자인 수트 2013.3에 통합되어 있다.”고 설명했다.

이 장에서 주목해야 할 또 다른 항목은 높은 안정성과 향상된 성능, 전력 최적화를 위한 개별 코딩 기법을 다루고 있는 3개의 섹션이다. 각 섹션은 비바도 디자인 수트의 통일된 데이터 모델의 장점을 충분히 활용할 수 있도록 추천 제약조건이 제공된다.

‘높은 안정성을 위한 코딩 방법(Coding Styles for High Reliability)’ 섹션에서는 CDC(Clock Domain Crossing; 클럭 영역 교차) 및 시간이 정해지지 않은 리셋, 결합 루프 방지에 대한 추천사항이 포함되어 있다. ‘향상된 성능(Improved Performance)’ 섹션은 중요 경로 및 레지스터에서의 높은 팬-아웃(Fan-Out)을 위한 권고사항 및 디자인의 파이프라이닝 구현을 위한 권고사항 등을 포함하고 있다. ‘전력 향상을 위한 코딩 스타일(Coding Styles to Improve Power)’ 섹션은 신뢰할 수 있는 데이터 경로 및 클럭 게이팅에서, 제어 세트 억제 및 게이팅 요소 극대화와 같은 보다 절묘한 권고사항들에 이르기까지 해당 디자인에 적용할 수 있는 다양한 전력 절감 기법을 확인할 수 있다.

5장은 합성에서 라우팅까지 구현 플로우에 초점을 두고 있으며, 구현 및 합성 속성, 상향식(Bottom-Up) 플로우의 장점으로 시작한다. 앞에서 논의된 것처럼, 이 장에서는 매우 심도 깊은 타이밍 분석을 포함하고 있으며, 타이밍 클로저를 위한 기준설정 컨셉을 소개하고 있다. 이외에도 타이밍 클로저 섹션은 여러분이 직면하게 될 다양한 타이밍 문제에 대해 무엇을 하고, 무엇을 하지 말아야 할지 여러 탁월한 권고사항을 제시하고 있다. 또한 동작 중의 타이밍 고려사항들을 다루고 있다.

이 가이드의 마지막 장인 6장은 컨피규레이션 및 디버깅을 다루고 있다. 앞 절반은 자일링스 올 프로그래머블 디바이스를 기반으로 비트스트림 생성 및 비트스트림 프로그래밍을 위한 최상의 방법을 단계별로 설명하고 있다. 나머지 절반은 플로우의 여러 단계에서 주로 디자인 디버깅을 위한 뛰어난 사례들을 보여주고 있다. 이 섹션은 HDL 예시 디버깅 검증 플로우를 어떻게 구현할 것인지, 넷리스트 삽입 디버깅 검증 플로우를 어떻게 사용할 것인지를 다루고 있다. 또한 타겟 디바이스에 로드된 디자인의 디버깅 전략을 소개하고 있다.

이 가이드의 부록에서는 울트라패스트 디자인 방법론 체크리스트에서 가장 중요하다고 보여지는 여러 부가적인 리소스를 제공하고 있는데, 디자인 팀이 디자인 플래닝에서 하드웨어 디버깅에 이르기까지 전 사이클의 각 단계별로 고려해야 하는 것들을 하이라이트하고 있다. 론은 “디자인 결정이 후속적인 영향을 야기하는 전형적인 영역들에 대한 수많은 질문들을 포함하고 있다.”고 언급했다. 체크리스트 링크는 가이드 내 혹은 특정 디자인 문제를 가장 잘 묘사하고 있는 외부 링크와 연결시켜준다. 또한 자일링스는 다운로드 가능한 스프레드시트 형태의 체크리스트도 제공한다.

울트라패스트 방법론 지원

이러한 모든 뛰어난 사례들을 ‘비바도 디자인 수트를 위한 울트라패스트 방법론 가이드’에 수록한 것과 더불어, 자일링스는 비바도 디자인 수트 2013.3 릴리스에 울트라패스트 방법론에 대한 수많은 권고사항을 포함시켰다. 2013.3 릴리스에서 비바도 디자인 수트는 디자인 사이클 전반에 걸쳐 이용자들을 효과적으로 가이드하기 위해 방법론 및 타이밍 DRC 룰 데크를 지원하고 있으며, 구조적 오류정정 기능을 갖춘 디자인을 위해 매우 유용한 HDL 및 제약조건 탬플릿을 포함하고 있다.

한편 자일링스의 전세계 트레이닝 스태프와 얼라이언스 맴버 에코시스템 또한 적극적으로 울트라패스트 방법론을 지원하고 있다.

예를 들어, BPS(Blue Pearl Software)는 자일링스 울트라패스트 디자인 룰을 자사의 Analyze RTL 린팅 툴에 추가했다. 론은 “BPS는 울트라패스트 방법론에서 서술된 RTL 가이드라인을 자동화했다.”며, “언어 린팅 수행과 더불어, 통합 블록을 추론하는 최적의 방법으로 적합한 형태의 리셋이나 RAM 및 MAC 코딩 사용과 같은 자일링스 디바이스를 위한 최적의 QoR을 제공하는 코딩 스타일을 시행하고 있다.”고 설명했다.

써드파티 EDA 지원과 더불어, 자일링스는 자사의 IP가 울트라패스트 방법론 및 DRC에 부응하도록 활발한 테스트를 진행하고 있으며, 또한 이러한 동일한 가이드라인을 얼라이언스 멤버 IP 벤더들이 따를 수 있도록 적극적으로 추동하고 있다.

한편 자일링스 및 전세계 파트너사들에 의해 트레이닝 등급의 시리즈들이 출시되고 있으며, 새로운 울트라패스트 방법론 QuickTake 비디오도 발표되었다. 또한 새로운 모든 자일링스 비디오는 울트라패스트 가이드라인을 포함하게 된다.

‘비바도 디자인 수트를 위한 울트라패스트 디자인 방법론(UG949)’ PDF 버전 다운로드 및 울트라패스트 방법론에 대한 추가 상세정보는 www.xilinx.com/ultrafast에서 확인할 수 있다.

- 태그 :

- timing,ultrafast,28nm,ultrascale

- 적용분야 :

- Industrial

- 관련제품 :

- Vivado Design Suite