Technical Article

제품 및 Tools

자일링스의 울트라스케일(UltraScale) 아키텍처로 생산성 급등

자일링스의 울트라스케일(UltraScale) 아키텍처로 생산성 급등

2015-02-01

자일링스의 울트라스케일(UltraScale) 아키텍처로 생산성 급등

글/ 닉 메타(Nick Mehta), 자일링스 수석 테크니컬 마케팅 매니저

다양한 마켓 및 애플리케이션에서는 상당한 수준의 시스템 대역폭 및 프로세싱 성능 증가가 요구되고 있다. 유선 혹은 무선 통신, 또는 디지털 비디오 및 이미지 프로세싱이든 상관없이 모두 증가하는 데이터 처리량으로 인해 모든 시스템 컴포넌트 상에서 트래픽 및 부담이 증가되고 있다. 따라서 더 많은 데이터들이 병렬 및 직렬 I/O를 통해 온칩 상으로 입력되게 되는데, 이 데이터는 DDR 메모리 형태의 병렬 I/O나 HMC(Hybrid Memory Cube) 및 MoSys 대역폭 엔진과 같은 직렬 메모리 표준 형태의 직렬 I/O를 통해 다시 버퍼링되어야 한다. 그런 다음, 이 데이터는 병렬 및 직렬 I/O를 통해 다시 다음 목적지로 전송되기 전에 로직 및 DSP에서 프로세싱 되어야 한다.

시스템 프로세싱 요건은 더 넓은 병렬 데이터 버스로 인해 증가된 데이터 전송속도와 증가된 주파수에서 이동하는 더 큰 데이터 패킷처럼 여러 이유로 인해 갈수록 더욱 복잡해지고 있다. 이러한 데이터를 효율적으로 처리하기 위해서는 단일 디바이스 상에 전체 시스템을 구현할 필요가 있으며, 이는 두 FPGA 간의 대규모 데이터 전송으로 인해 발생하는 지연이나 전력소모를 제거할 수 있다. 이를 위해서는 더 많은 기능을 갖춘 전례없는 고밀도의 FPGA가 필요하다. 이러한 고성능 FPGA는 보다 밀도있게 활용되기 때문에 가능한 최대 성능으로 동작이 유지되도록 하고, 디바이스가 가득 차면서 성능이 저하되지 않도록 방지하는 것이 중요하다.

복잡한 고성능 디바이스의 활용도를 극대화하는 것은 디자이너에게 어려운 작업처럼 들릴 수도 있을 것이다. 이를 위해 자일링스는 특히 설계시간을 단축하고, 디자이너가 마켓에서 제품을 차별화하는데 보다 주력할 수 있도록 다양한 솔루션을 공급하고 있다.

울트라스케일 아키텍처

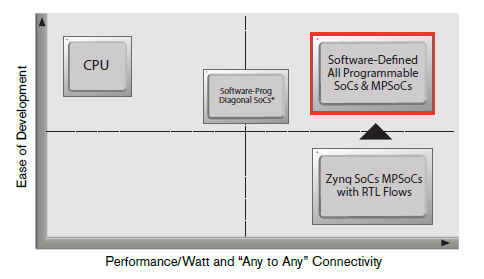

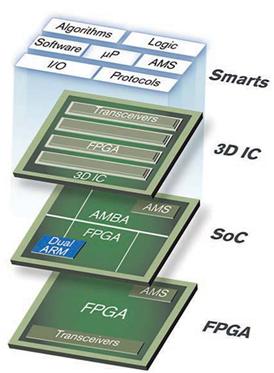

이러한 마켓의 주된 도전과제들을 해결하기 위해 자일링스는 최근 유례없는 시스템 집적도와 성능, 기능을 제공하는 울트라스케일(UltraScale™) 아키텍처(그림 1)를 발표했다. 자일링스는 이 새로운 아키텍처를 기반으로 2개의 고성능 FPGA 제품군을 구현했다. 자일링스(Xilinx®) 버텍스(Virtex®) 울트라스케일 및 킨텍스(Virtex®) 울트라스케일 제품군은 수많은 혁신적인 기술 발전을 통해 전체 전력소모를 낮추면서도, 여러 다양한 시스템 요건을 모두 해결할 수 있다. 많은 빌딩 블록들을 공유하는 울트라스케일 기술은 확장 가능한 아키텍처로, 서로 다른 마켓의 요구를 최적화할 수 있다.

증가하는 시스템 대역폭

어떠한 시그널 프로세싱이나 데이터 처리가 수행되기 이전에 데이터는 해당 목적지에 도달해야 한다. 오늘날 존재하는 수많은 직렬 및 병렬 프로토콜이나 표준은 타깃 애플리케이션의 특정 요구에 맞춰져 있다. 대다수 표준들의 보편적인 테마는 필요로 하는 전체 데이터 처리량의 증가이며, 시스템을 통해 방대한 양의 정보를 향상된 데이터 전송속도로 이동시키는 것이다.

울트라스케일 아키텍처 기반의 FPGA는 고성능 병렬 SelectIO™ 및 고속 시리얼 트랜시버 커넥티비티를 통해 상호 데이터를 전송한다. I/O 블록은 유연한 I/O 표준 및 전압 지원을 통해 네트워크 프로토콜 및 첨단 메모리 인터페이스가 가능하다. 울트라스케일 아키텍처 상의 각기 다른 시리얼 트랜시버는 최고 16.3Gbps의 속도로 데이터를 전송하며, 주요 시리얼 프로토콜에서 요구되는 모든 성능을 제공하는 것은 물론, 최고 32.75Gbps에서 기존 세대 트랜시버 보다 비트당 전력소모를 획기적으로 낮춘 25G+ 백플레인 디자인이 가능하다. 울트라스케일 FPGA 상의 모든 트랜시버는 PCI Express® Gen3 및 Gen4에서 요구되는 데이터 전송속도를 지원하며, PCI Express를 위한 통합 블록은 울트라스케일 아키텍처 기반 FPGA를 통해 최고 x8 Gen3 엔드포인트(Endpoint) 및 루트 포트(Root Port) 디자인이 가능하도록 해준다.

그림 1. 울트라스케일 아키텍처의 주요 혜택은 속도 및 대역폭이다.

데이터 클럭킹 및 버퍼링

모든 동기식 시스템은 회로 동기화를 위해 하나 이상의 클럭 신호에 의존하고 있다. 시스템 성능이 증가하면서 더 큰 디바이스 용량과 함께 더 높은 클럭 주파수가 필요하게 되었으며, 향상된 클럭 유연성 및 보다 낮은 전체 클럭 전력소모 등이 모두 요구되고 있다.

울트라스케일 아키텍처는 디자인 요건에 부합하는 매우 뛰어난 프레임워크를 제공하는 클럭 합성, 컴포넌트 라우팅 및 버퍼링을 비롯해 새롭게 구현된 강력한 클럭-관리 회로를 포함하고 있다. 이 클럭 네트워크는 클럭 신호와 관련된 스큐 및 전력소모, 지연을 최소화하도록 FPGA 내에서 매우 유연한 클럭 분배를 가능하게 해준다. 또한 이 클럭-관리 기술은 DDR4와 같은 고성능 외부 메모리를 지원할 수 있도록 전용 메모리-인터페이스 회로와 긴밀하게 통합되어 있다. 클럭 분할 및 새로운 클럭-게이팅 단위는 기존 FPGA와 비교해 추가로 클럭 전력소모를 제어할 수 있도록 해준다.

기존 제품 및 경쟁사 FPGA와 비교해 글로벌-지원가능 클럭 버퍼 수의 획기적인 증가는 디자이너의 생산성에 상당한 혜택을 제공한다. 사실상 글로벌 버퍼는 FPGA 중앙에 위치한 32개의 글로벌 클럭 버퍼 만으로 지금까지는 사용이 제한적이었다. 울트라스케일 아키텍처는 글로벌-지원가능 클럭 버퍼가 아키텍처 전반에 걸쳐 풍부하게 분산되어 있으며, 필요한 곳에 리소스를 제공하고, 제한적으로 사용할 필요가 없어졌다. 또한 자일링스는 모든 클럭-스위칭 및 클럭-분할, 클럭-활성화 기능을 유지하면서도 이전 FPGA 세대에 비해 클럭 버퍼 형태를 상당히 간소화했다. 이로써 필요한 지점에서만 모든 기능으로 구동 가능한 클럭 버퍼를 제공함으로써 뛰어난 유연성을 달성했다.

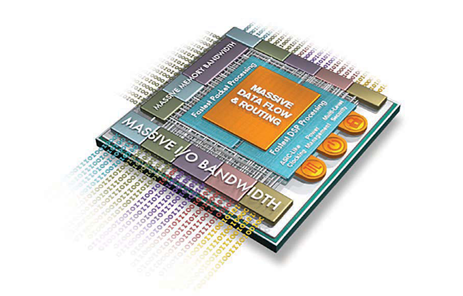

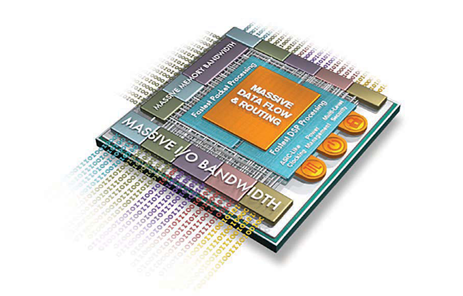

그림 2. 울트라스케일 아키텍처는 방대한 양의 데이터를 처리할 수 있다.

데이터 저장, 프로세싱, 라우팅

모든 시스템의 핵심은 수신된 데이터를 프로세싱하고, 처리 및 변환하는 능력이라 할 수 있다.(그림 2) 시스템 복잡도가 증가함에 따라 범용 패브릭과 더불어 특정 데이터 프로세싱 타입에 부합하는 보다 전문적인 기능이 요구되고 있다.

최신 FPGA 패브릭에는 여러 요소들이 있는데, 6-입력 LUT(Lookup Table)를 포함한 CLB(Configurable Logic Block)를 비롯해 플립-플롭(Flip-Flop), 27x18 곱셈기를 갖춘 DSP 슬라이스, 통합 FIFO 및 ECC 지원 36kbit 블록 RAM 등이 있다. 이러한 리소스는 모두 풍부한 고성능, 저-지연 인터커넥트와 함께 연결되어 있다.

로직 기능과 더불어, CLB는 위상 레지스터 및 멀티플렉서, 캐리-로직 기능은 물론, 매우 유용하고 컨피규레이션이 가능한 블록 RAM을 보완하는 분산 메모리처럼 LUT를 컨피규레이션할 수 있는 기능을 제공한다. 새로운 96bit 폭의 XOR 기능과 더 넓은 27bit 프리-애더(Pre-Adder) 및 30bit 입력을 갖춘 DSP 슬라이스는 MAC(Multiply-Accumulate), 곱셈-덧셈 연산, 패턴 감지를 비롯한 수많은 독립적인 기능을 수행한다. 디바이스 인터커넥트와 더불어, 2세대 SSI 3DIC 기술을 통해 구현된 디바이스들의 시그널은 전용 저-지연 인터페이스 타일을 이용해 수퍼-로직 영역 간을 교차할 수 있다. 이러한 혼성 라우팅 리소스는 차세대 데이터 버스 폭을 손쉽게 지원할 수 있으며, 디바이스 활용도를 90% 이상 높일 수 있다.

디자인 도전과제 해결 용이성

울트라스케일 아키텍처를 통해 실현된 아키텍처 측면의 발전은 디자이너가 더 많은 디자인을 동일한 공간 안에 구현할 수 있도록 했지만, 디바이스 크기는 증가한다. 더 많은 디자인을 단일 디바이스 상에 구현할 수 있다는 것은 상당한 혜택인 반면, 이와 더불어 디자인 팀은 최종 제품을 가능한 빨리 시장에 출시하기 위해 특정 디자인을 신속하게 구현할 수 있어야 한다. 울트라스케일 아키텍처와 이에 최적화된 비바도(Vivado®) 디자인 수트와 더불어, 자일링스는 시간 절감이 가능하고 생산성을 향상시키는 여러 솔루션을 제공하고 있다.

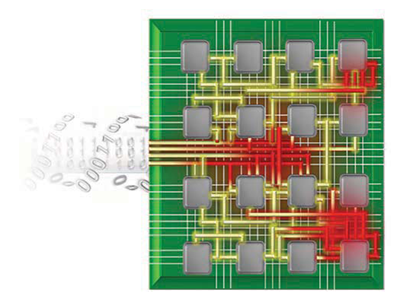

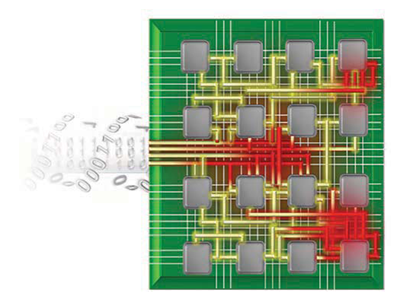

그림 3. 울트라스케일 디바이스는 업계 선도적인 기술에 범용 기능을 추가했다.

핵심 기능 통합

다른 많은 것들과 더불어 프로그램 가능성의 유연함은 소중한 자산이지만, 구속이 없는 것은 아니다. 프로그래머블 리소스로 구현한 기능은 동일한 기능을 전용 블록으로 구현한 경우보다 더 크거나 간혹 느릴 수도 있다. 물론 본래의 특성상 FPGA는 대부분 프로그래머블이다. 하지만 자일링스 FPGA는 사용자가 일반적으로 사용하는 기능을 신속하게 구현할 수 있도록 전용 기능과 통합 IP를 적절하게 조합하여 구현하고 있다.(그림 3 참조) 울트라스케일 아키텍처는 여러 범용 통신 프로토콜을 위한 통합 블록을 포함하고 있다. 킨텍스 울트라스케일 및 버텍스 울트라스케일 디바이스에는 PCI Express 및 100G 이더넷, 150G 인터라켄(Interlaken)을 위한 여러 통합 블록이 있으며, 모두 테스트 및 검증이 완료되어 확실한 기능을 제공한다.

통신 프로토콜과 더불어, 모든 I/O 뱅크는 MIG(Memory Interface Generator) 툴로 컨피규레이션이 가능한 프로그래머블 메모리 PHY를 포함하고 있다. 이는 필요한 경우 뛰어난 집적도를 보여줄 수 있다. 이 메모리 PHY 및 일부 제어 로직은 프로그래머블 전용 기능처럼 구현되지만, 메모리 인터페이스의 디지털 부분은 디바이스 패브릭으로 만들어지며, 모든 필요한 커스터마이제이션을 제공하고, 전용 회로로 제공하기 어려운 각기 다른 모드를 지원한다.

디바이스 패브릭 내에는 다른 수많은 블록들이 있으며, 이는 프로그래머블 특성을 유지하면서도 특정 기능을 수행하도록 구현되어 있다. 디자이너는 여러 깊이 및 폭으로 블록 메모리를 컨피규레이션할 수 있으며, 더 큰 저전력 어레이로 만들 수도 있다. DSP 슬라이스는 사용자가 선택한 기능에 따라 여러 블록 컴포넌트에 액세스할 수 있는 다양한 모드를 갖추고 있다. 따라서 게이트나 레지스터 수준을 넘어 울트라스케일 아키텍처 전반에 걸쳐 뛰어난 유연성이 제공된다.

사용자가 조정할 수 있고, 반복 사용이 가능한 IP로 생산성 향상

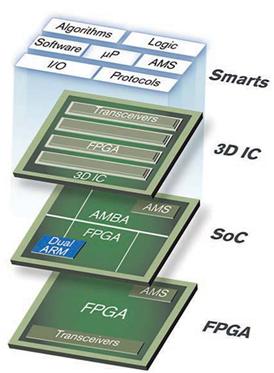

모든 디자인은 시스템을 구현하기 위해 함께 연결된 여러 다양한 구조적 빌딩 블록으로 구성된다. 일부 기능은 이미 업계에서 확실히 인정받은 것으로, 기능이 고정된 전용 블록으로 제공되어 매우 경제적이다. 하지만 최적의 방법은 프로그래머블 로직에 구현되도록 기능을 설계하고, 이 기능을 검증한 다음, 필요할 때마다 이 기능을 재사용하는 것이다. 이러한 형태의 IP 컨셉은 여러 세대에 걸쳐 있어왔지만, 자일링스는 최근 여러 면에서 생산성을 향상시켰다.(그림 4 참조)

그림 4. 비바도 툴은 복잡한 디자인 구현 및 개발을 가속화한다.

플러그 & 플레이 IP

2012년에 자일링스는 플러그&플레이(Plug-and-Play) IP를 위한 표준 인터페이스로 ARM® AMBA® AXI4 인터페이스를 채택했다. 단일의 표준 인터페이스를 이용함으로써 이전보다 훨씬 쉽게 IP를 통합할 수 있게 되었으며, 광범위한 인터페이스 어레이를 하나로 통합함으로써 디자이너가 더 이상 수많은 서로 다른 인터페이스를 이해할 필요가 없어졌다. 울트라스케일 아키텍처는 AXI4 인터커넥트의 유연성 및 확장성을 통해 디자이너가 시장 출시시기를 단축할 수 있도록 해주는 동시에, AXI4-Lite 및 AXI4-Stream을 비롯한 각기 다른 AXI4 인터커넥트 프로토콜을 통해 성능 및 공간, 전력소모에 최적화된 IP를 구현할 수 있도록 함으로써 계속해서 혜택을 제공하게 될 것이다.

비바도 IP Packager 및 IP Catalog는 원래 SPIRIT Consortium이 툴 플로우 내에서 IP 패키징 및 통합, 재사용을 위한 표준 구조로 개발한 IP-XACT 표준을 활용하고 있다. IPXACT는 IEEE 표준((IEEE1685-2009)으로 현재 승인을 받았다. 비바도 IP Packager는 확장 가능한 IP 카탈로그에서 제공되는 디자인 제약조건(Constraints) 및 테스트벤치, 문서를 통해 로컬 또는 공유 드라이브 상에서 디자인을 구현한다. 비바도 IP Catalog는 여러 디자인 팀들이 간단한 사용방법으로 일관되게 모든 IP를 공유할 수 있도록 사용자들이 자체 IP와 자일링스 및 써드파티 IP를 통합할 수 있도록 해준다.

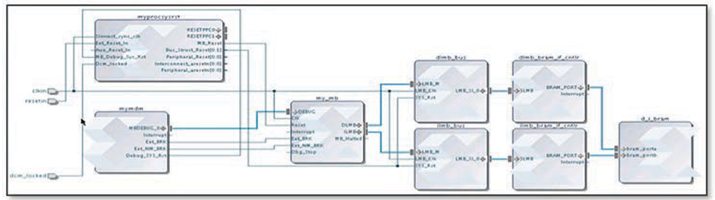

비바도 IP Integrator

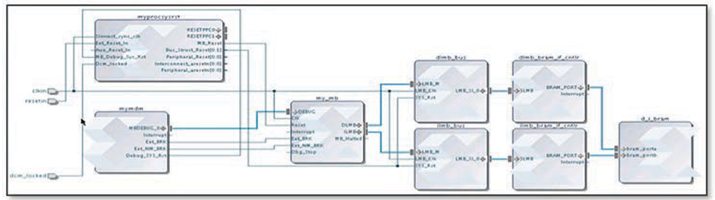

비바도 IP Integrator(그림 5)는 IP-중심의 디자인 플로우로 시스템 통합을 가속화하고, 구성 부품들로 보다 쉽고 빠르게 시스템을 구현할 수 있도록 해준다. 쌍방향 그래픽 기반 유저 인터페이스를 갖춘 IPI는 지능형 자동연결 IP 인터페이스와 원클릭 IP 서브시스템 생성, 강력한 디버깅 기능을 제공하며, 디자이너가 빠르고 쉽게 IP 카탈로그의 어떠한 IP라도 연결할 수 있도록 해준다. 이러한 기능은 디자이너가 모든 빌딩 블록들이 올바르게 컨피규레이션되어 있는, 무료로 제공되거나 구매 혹은 자체 개발한 여러 다양한 디자인 소스로 구성된 복잡한 시스템을 신속하게 구성할 수 있도록 해준다. 이를 통해 컨셉에서 디버깅까지 유례없이 훨씬 빨라졌다.

그림 5. IP Integrator를 이용해 디자인을 구현하면, IP 블록 연결이 간단해진다.

요약하면, 울트라스케일 아키텍처는 차세대 고성능 디자인에서 필요로 하는 핵심 요건에 성공적으로 부합할 수 있도록 여러 중요한 부분에서 구조적인 혁신을 달성했다. 울트라스케일이 실현한 것처럼, 유례없이 증가하는 시스템 주파수에서 넓은 데이터 버스로 디자인을 구현할 수 있는 능력을 갖추는 것은 퍼즐의 중요한 부분이다. 하지만 디바이스 크기 및 복잡성의 증가로 인해, 디자이너가 생산성을 지속적으로 증대시킬 수 있도록 하는 것이 중요하다. 자일링스는 통합 블록과 사전 검증된 IP를 함께 제공함으로써 보다 빠르게 최상의 솔루션을 구현하는데 필요한 모든 툴을 디자이너에게 공급하고 있다.

글/ 닉 메타(Nick Mehta), 자일링스 수석 테크니컬 마케팅 매니저

다양한 마켓 및 애플리케이션에서는 상당한 수준의 시스템 대역폭 및 프로세싱 성능 증가가 요구되고 있다. 유선 혹은 무선 통신, 또는 디지털 비디오 및 이미지 프로세싱이든 상관없이 모두 증가하는 데이터 처리량으로 인해 모든 시스템 컴포넌트 상에서 트래픽 및 부담이 증가되고 있다. 따라서 더 많은 데이터들이 병렬 및 직렬 I/O를 통해 온칩 상으로 입력되게 되는데, 이 데이터는 DDR 메모리 형태의 병렬 I/O나 HMC(Hybrid Memory Cube) 및 MoSys 대역폭 엔진과 같은 직렬 메모리 표준 형태의 직렬 I/O를 통해 다시 버퍼링되어야 한다. 그런 다음, 이 데이터는 병렬 및 직렬 I/O를 통해 다시 다음 목적지로 전송되기 전에 로직 및 DSP에서 프로세싱 되어야 한다.

시스템 프로세싱 요건은 더 넓은 병렬 데이터 버스로 인해 증가된 데이터 전송속도와 증가된 주파수에서 이동하는 더 큰 데이터 패킷처럼 여러 이유로 인해 갈수록 더욱 복잡해지고 있다. 이러한 데이터를 효율적으로 처리하기 위해서는 단일 디바이스 상에 전체 시스템을 구현할 필요가 있으며, 이는 두 FPGA 간의 대규모 데이터 전송으로 인해 발생하는 지연이나 전력소모를 제거할 수 있다. 이를 위해서는 더 많은 기능을 갖춘 전례없는 고밀도의 FPGA가 필요하다. 이러한 고성능 FPGA는 보다 밀도있게 활용되기 때문에 가능한 최대 성능으로 동작이 유지되도록 하고, 디바이스가 가득 차면서 성능이 저하되지 않도록 방지하는 것이 중요하다.

복잡한 고성능 디바이스의 활용도를 극대화하는 것은 디자이너에게 어려운 작업처럼 들릴 수도 있을 것이다. 이를 위해 자일링스는 특히 설계시간을 단축하고, 디자이너가 마켓에서 제품을 차별화하는데 보다 주력할 수 있도록 다양한 솔루션을 공급하고 있다.

울트라스케일 아키텍처

이러한 마켓의 주된 도전과제들을 해결하기 위해 자일링스는 최근 유례없는 시스템 집적도와 성능, 기능을 제공하는 울트라스케일(UltraScale™) 아키텍처(그림 1)를 발표했다. 자일링스는 이 새로운 아키텍처를 기반으로 2개의 고성능 FPGA 제품군을 구현했다. 자일링스(Xilinx®) 버텍스(Virtex®) 울트라스케일 및 킨텍스(Virtex®) 울트라스케일 제품군은 수많은 혁신적인 기술 발전을 통해 전체 전력소모를 낮추면서도, 여러 다양한 시스템 요건을 모두 해결할 수 있다. 많은 빌딩 블록들을 공유하는 울트라스케일 기술은 확장 가능한 아키텍처로, 서로 다른 마켓의 요구를 최적화할 수 있다.

증가하는 시스템 대역폭

어떠한 시그널 프로세싱이나 데이터 처리가 수행되기 이전에 데이터는 해당 목적지에 도달해야 한다. 오늘날 존재하는 수많은 직렬 및 병렬 프로토콜이나 표준은 타깃 애플리케이션의 특정 요구에 맞춰져 있다. 대다수 표준들의 보편적인 테마는 필요로 하는 전체 데이터 처리량의 증가이며, 시스템을 통해 방대한 양의 정보를 향상된 데이터 전송속도로 이동시키는 것이다.

울트라스케일 아키텍처 기반의 FPGA는 고성능 병렬 SelectIO™ 및 고속 시리얼 트랜시버 커넥티비티를 통해 상호 데이터를 전송한다. I/O 블록은 유연한 I/O 표준 및 전압 지원을 통해 네트워크 프로토콜 및 첨단 메모리 인터페이스가 가능하다. 울트라스케일 아키텍처 상의 각기 다른 시리얼 트랜시버는 최고 16.3Gbps의 속도로 데이터를 전송하며, 주요 시리얼 프로토콜에서 요구되는 모든 성능을 제공하는 것은 물론, 최고 32.75Gbps에서 기존 세대 트랜시버 보다 비트당 전력소모를 획기적으로 낮춘 25G+ 백플레인 디자인이 가능하다. 울트라스케일 FPGA 상의 모든 트랜시버는 PCI Express® Gen3 및 Gen4에서 요구되는 데이터 전송속도를 지원하며, PCI Express를 위한 통합 블록은 울트라스케일 아키텍처 기반 FPGA를 통해 최고 x8 Gen3 엔드포인트(Endpoint) 및 루트 포트(Root Port) 디자인이 가능하도록 해준다.

그림 1. 울트라스케일 아키텍처의 주요 혜택은 속도 및 대역폭이다.

데이터 클럭킹 및 버퍼링

모든 동기식 시스템은 회로 동기화를 위해 하나 이상의 클럭 신호에 의존하고 있다. 시스템 성능이 증가하면서 더 큰 디바이스 용량과 함께 더 높은 클럭 주파수가 필요하게 되었으며, 향상된 클럭 유연성 및 보다 낮은 전체 클럭 전력소모 등이 모두 요구되고 있다.

울트라스케일 아키텍처는 디자인 요건에 부합하는 매우 뛰어난 프레임워크를 제공하는 클럭 합성, 컴포넌트 라우팅 및 버퍼링을 비롯해 새롭게 구현된 강력한 클럭-관리 회로를 포함하고 있다. 이 클럭 네트워크는 클럭 신호와 관련된 스큐 및 전력소모, 지연을 최소화하도록 FPGA 내에서 매우 유연한 클럭 분배를 가능하게 해준다. 또한 이 클럭-관리 기술은 DDR4와 같은 고성능 외부 메모리를 지원할 수 있도록 전용 메모리-인터페이스 회로와 긴밀하게 통합되어 있다. 클럭 분할 및 새로운 클럭-게이팅 단위는 기존 FPGA와 비교해 추가로 클럭 전력소모를 제어할 수 있도록 해준다.

기존 제품 및 경쟁사 FPGA와 비교해 글로벌-지원가능 클럭 버퍼 수의 획기적인 증가는 디자이너의 생산성에 상당한 혜택을 제공한다. 사실상 글로벌 버퍼는 FPGA 중앙에 위치한 32개의 글로벌 클럭 버퍼 만으로 지금까지는 사용이 제한적이었다. 울트라스케일 아키텍처는 글로벌-지원가능 클럭 버퍼가 아키텍처 전반에 걸쳐 풍부하게 분산되어 있으며, 필요한 곳에 리소스를 제공하고, 제한적으로 사용할 필요가 없어졌다. 또한 자일링스는 모든 클럭-스위칭 및 클럭-분할, 클럭-활성화 기능을 유지하면서도 이전 FPGA 세대에 비해 클럭 버퍼 형태를 상당히 간소화했다. 이로써 필요한 지점에서만 모든 기능으로 구동 가능한 클럭 버퍼를 제공함으로써 뛰어난 유연성을 달성했다.

그림 2. 울트라스케일 아키텍처는 방대한 양의 데이터를 처리할 수 있다.

데이터 저장, 프로세싱, 라우팅

모든 시스템의 핵심은 수신된 데이터를 프로세싱하고, 처리 및 변환하는 능력이라 할 수 있다.(그림 2) 시스템 복잡도가 증가함에 따라 범용 패브릭과 더불어 특정 데이터 프로세싱 타입에 부합하는 보다 전문적인 기능이 요구되고 있다.

최신 FPGA 패브릭에는 여러 요소들이 있는데, 6-입력 LUT(Lookup Table)를 포함한 CLB(Configurable Logic Block)를 비롯해 플립-플롭(Flip-Flop), 27x18 곱셈기를 갖춘 DSP 슬라이스, 통합 FIFO 및 ECC 지원 36kbit 블록 RAM 등이 있다. 이러한 리소스는 모두 풍부한 고성능, 저-지연 인터커넥트와 함께 연결되어 있다.

로직 기능과 더불어, CLB는 위상 레지스터 및 멀티플렉서, 캐리-로직 기능은 물론, 매우 유용하고 컨피규레이션이 가능한 블록 RAM을 보완하는 분산 메모리처럼 LUT를 컨피규레이션할 수 있는 기능을 제공한다. 새로운 96bit 폭의 XOR 기능과 더 넓은 27bit 프리-애더(Pre-Adder) 및 30bit 입력을 갖춘 DSP 슬라이스는 MAC(Multiply-Accumulate), 곱셈-덧셈 연산, 패턴 감지를 비롯한 수많은 독립적인 기능을 수행한다. 디바이스 인터커넥트와 더불어, 2세대 SSI 3DIC 기술을 통해 구현된 디바이스들의 시그널은 전용 저-지연 인터페이스 타일을 이용해 수퍼-로직 영역 간을 교차할 수 있다. 이러한 혼성 라우팅 리소스는 차세대 데이터 버스 폭을 손쉽게 지원할 수 있으며, 디바이스 활용도를 90% 이상 높일 수 있다.

디자인 도전과제 해결 용이성

울트라스케일 아키텍처를 통해 실현된 아키텍처 측면의 발전은 디자이너가 더 많은 디자인을 동일한 공간 안에 구현할 수 있도록 했지만, 디바이스 크기는 증가한다. 더 많은 디자인을 단일 디바이스 상에 구현할 수 있다는 것은 상당한 혜택인 반면, 이와 더불어 디자인 팀은 최종 제품을 가능한 빨리 시장에 출시하기 위해 특정 디자인을 신속하게 구현할 수 있어야 한다. 울트라스케일 아키텍처와 이에 최적화된 비바도(Vivado®) 디자인 수트와 더불어, 자일링스는 시간 절감이 가능하고 생산성을 향상시키는 여러 솔루션을 제공하고 있다.

그림 3. 울트라스케일 디바이스는 업계 선도적인 기술에 범용 기능을 추가했다.

핵심 기능 통합

다른 많은 것들과 더불어 프로그램 가능성의 유연함은 소중한 자산이지만, 구속이 없는 것은 아니다. 프로그래머블 리소스로 구현한 기능은 동일한 기능을 전용 블록으로 구현한 경우보다 더 크거나 간혹 느릴 수도 있다. 물론 본래의 특성상 FPGA는 대부분 프로그래머블이다. 하지만 자일링스 FPGA는 사용자가 일반적으로 사용하는 기능을 신속하게 구현할 수 있도록 전용 기능과 통합 IP를 적절하게 조합하여 구현하고 있다.(그림 3 참조) 울트라스케일 아키텍처는 여러 범용 통신 프로토콜을 위한 통합 블록을 포함하고 있다. 킨텍스 울트라스케일 및 버텍스 울트라스케일 디바이스에는 PCI Express 및 100G 이더넷, 150G 인터라켄(Interlaken)을 위한 여러 통합 블록이 있으며, 모두 테스트 및 검증이 완료되어 확실한 기능을 제공한다.

통신 프로토콜과 더불어, 모든 I/O 뱅크는 MIG(Memory Interface Generator) 툴로 컨피규레이션이 가능한 프로그래머블 메모리 PHY를 포함하고 있다. 이는 필요한 경우 뛰어난 집적도를 보여줄 수 있다. 이 메모리 PHY 및 일부 제어 로직은 프로그래머블 전용 기능처럼 구현되지만, 메모리 인터페이스의 디지털 부분은 디바이스 패브릭으로 만들어지며, 모든 필요한 커스터마이제이션을 제공하고, 전용 회로로 제공하기 어려운 각기 다른 모드를 지원한다.

디바이스 패브릭 내에는 다른 수많은 블록들이 있으며, 이는 프로그래머블 특성을 유지하면서도 특정 기능을 수행하도록 구현되어 있다. 디자이너는 여러 깊이 및 폭으로 블록 메모리를 컨피규레이션할 수 있으며, 더 큰 저전력 어레이로 만들 수도 있다. DSP 슬라이스는 사용자가 선택한 기능에 따라 여러 블록 컴포넌트에 액세스할 수 있는 다양한 모드를 갖추고 있다. 따라서 게이트나 레지스터 수준을 넘어 울트라스케일 아키텍처 전반에 걸쳐 뛰어난 유연성이 제공된다.

사용자가 조정할 수 있고, 반복 사용이 가능한 IP로 생산성 향상

모든 디자인은 시스템을 구현하기 위해 함께 연결된 여러 다양한 구조적 빌딩 블록으로 구성된다. 일부 기능은 이미 업계에서 확실히 인정받은 것으로, 기능이 고정된 전용 블록으로 제공되어 매우 경제적이다. 하지만 최적의 방법은 프로그래머블 로직에 구현되도록 기능을 설계하고, 이 기능을 검증한 다음, 필요할 때마다 이 기능을 재사용하는 것이다. 이러한 형태의 IP 컨셉은 여러 세대에 걸쳐 있어왔지만, 자일링스는 최근 여러 면에서 생산성을 향상시켰다.(그림 4 참조)

그림 4. 비바도 툴은 복잡한 디자인 구현 및 개발을 가속화한다.

플러그 & 플레이 IP

2012년에 자일링스는 플러그&플레이(Plug-and-Play) IP를 위한 표준 인터페이스로 ARM® AMBA® AXI4 인터페이스를 채택했다. 단일의 표준 인터페이스를 이용함으로써 이전보다 훨씬 쉽게 IP를 통합할 수 있게 되었으며, 광범위한 인터페이스 어레이를 하나로 통합함으로써 디자이너가 더 이상 수많은 서로 다른 인터페이스를 이해할 필요가 없어졌다. 울트라스케일 아키텍처는 AXI4 인터커넥트의 유연성 및 확장성을 통해 디자이너가 시장 출시시기를 단축할 수 있도록 해주는 동시에, AXI4-Lite 및 AXI4-Stream을 비롯한 각기 다른 AXI4 인터커넥트 프로토콜을 통해 성능 및 공간, 전력소모에 최적화된 IP를 구현할 수 있도록 함으로써 계속해서 혜택을 제공하게 될 것이다.

비바도 IP Packager 및 IP Catalog는 원래 SPIRIT Consortium이 툴 플로우 내에서 IP 패키징 및 통합, 재사용을 위한 표준 구조로 개발한 IP-XACT 표준을 활용하고 있다. IPXACT는 IEEE 표준((IEEE1685-2009)으로 현재 승인을 받았다. 비바도 IP Packager는 확장 가능한 IP 카탈로그에서 제공되는 디자인 제약조건(Constraints) 및 테스트벤치, 문서를 통해 로컬 또는 공유 드라이브 상에서 디자인을 구현한다. 비바도 IP Catalog는 여러 디자인 팀들이 간단한 사용방법으로 일관되게 모든 IP를 공유할 수 있도록 사용자들이 자체 IP와 자일링스 및 써드파티 IP를 통합할 수 있도록 해준다.

비바도 IP Integrator

비바도 IP Integrator(그림 5)는 IP-중심의 디자인 플로우로 시스템 통합을 가속화하고, 구성 부품들로 보다 쉽고 빠르게 시스템을 구현할 수 있도록 해준다. 쌍방향 그래픽 기반 유저 인터페이스를 갖춘 IPI는 지능형 자동연결 IP 인터페이스와 원클릭 IP 서브시스템 생성, 강력한 디버깅 기능을 제공하며, 디자이너가 빠르고 쉽게 IP 카탈로그의 어떠한 IP라도 연결할 수 있도록 해준다. 이러한 기능은 디자이너가 모든 빌딩 블록들이 올바르게 컨피규레이션되어 있는, 무료로 제공되거나 구매 혹은 자체 개발한 여러 다양한 디자인 소스로 구성된 복잡한 시스템을 신속하게 구성할 수 있도록 해준다. 이를 통해 컨셉에서 디버깅까지 유례없이 훨씬 빨라졌다.

그림 5. IP Integrator를 이용해 디자인을 구현하면, IP 블록 연결이 간단해진다.

요약하면, 울트라스케일 아키텍처는 차세대 고성능 디자인에서 필요로 하는 핵심 요건에 성공적으로 부합할 수 있도록 여러 중요한 부분에서 구조적인 혁신을 달성했다. 울트라스케일이 실현한 것처럼, 유례없이 증가하는 시스템 주파수에서 넓은 데이터 버스로 디자인을 구현할 수 있는 능력을 갖추는 것은 퍼즐의 중요한 부분이다. 하지만 디바이스 크기 및 복잡성의 증가로 인해, 디자이너가 생산성을 지속적으로 증대시킬 수 있도록 하는 것이 중요하다. 자일링스는 통합 블록과 사전 검증된 IP를 함께 제공함으로써 보다 빠르게 최상의 솔루션을 구현하는데 필요한 모든 툴을 디자이너에게 공급하고 있다.

- 적용분야 :

- Industrial

- 관련제품 :

- UltraScale