-

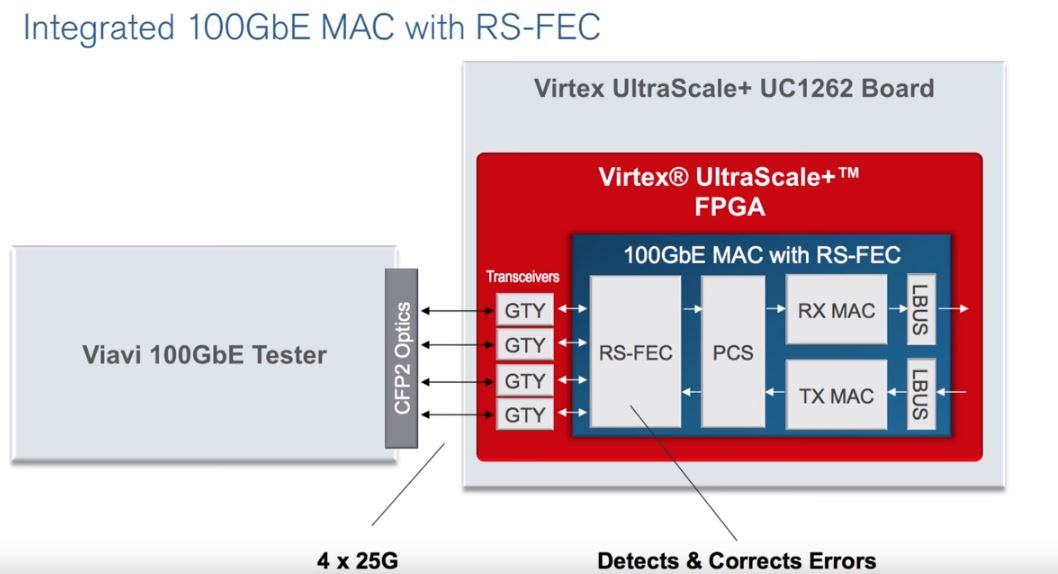

- 16nm UltraScale+™ 위한 100G 이더넷 솔루션의 성능, 통합 RS-FEC 모듈로 향상

- 16nm UltraScale+ FPGA 및 MPSoC를 위한 Xilinx 통합 100G 이더넷 솔루..

-

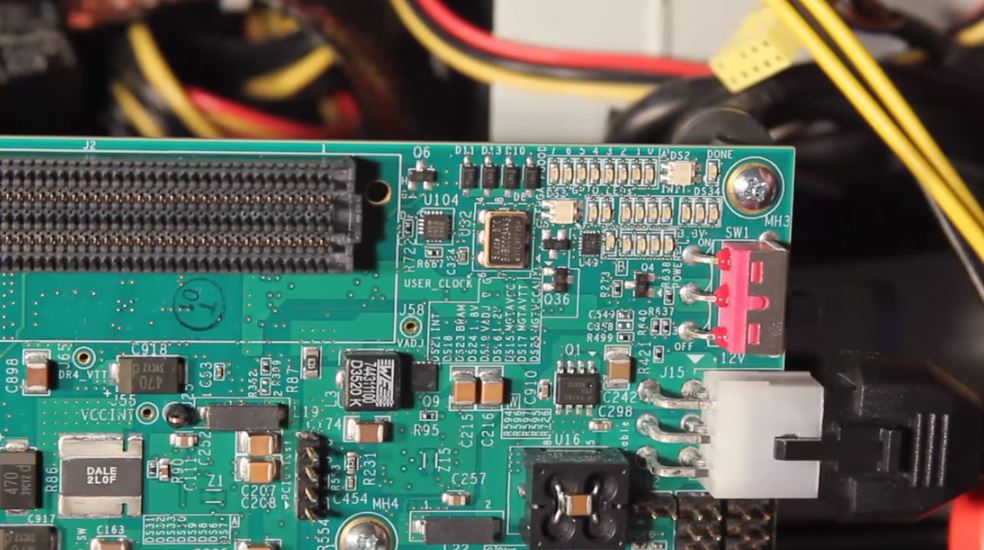

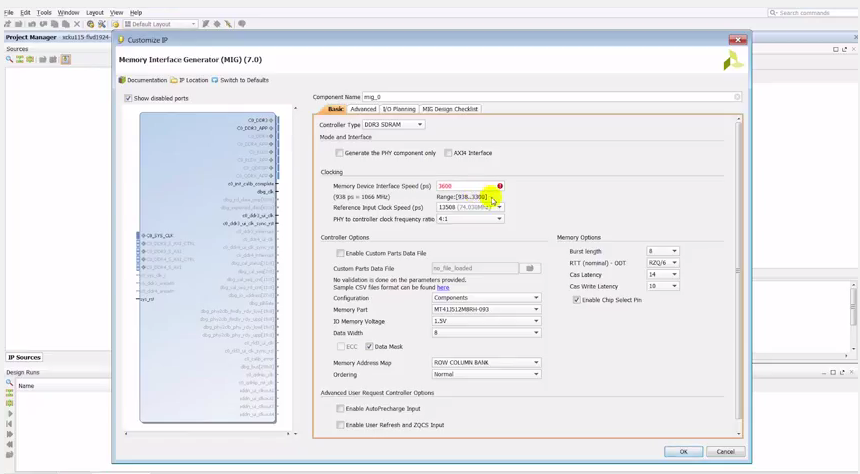

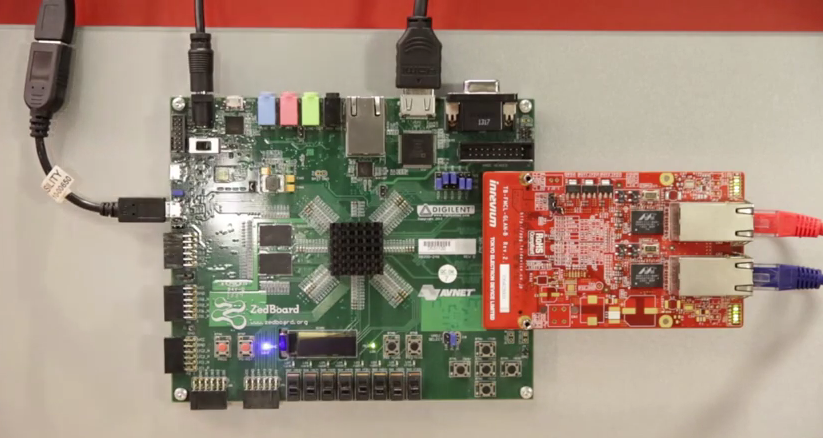

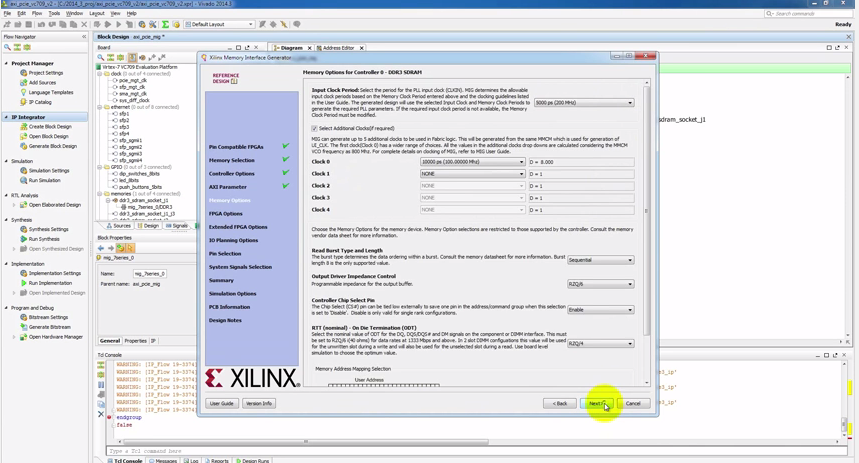

- MIG를 갖춘 AXI PCIe®, Jungo Connectivity사의 WinDriver를 이용하여 KCU105 평가 키트에 구현

- IP Integrator(IPI)를 이용하여 간단한 하드웨어 디자인을 개발하는 과정을 배우십시오. ..

-

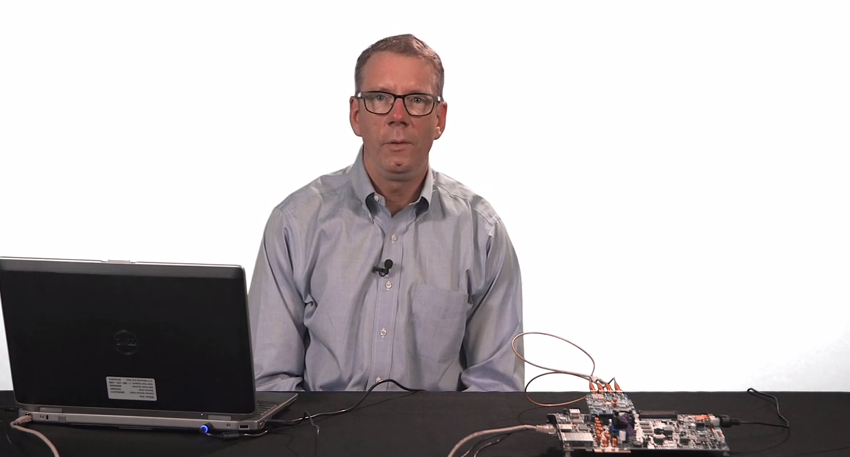

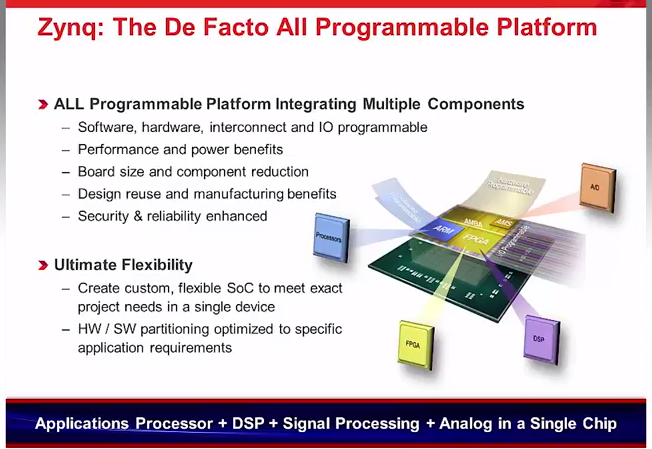

- 자일링스의 최신 전략과 포트폴리오 소개

- 마케팅 전문인 Steve Glaser가 이야기하는 자일링스의 최신 전력과 포트폴리오를 알아..

-

- 데이터센터용의 25Gb 구리 인터커넥트 규격 준수하는 Virtex UltraScale

- 본 비디오는 Xilinx Virtex UltraScale 30Gig GTY Transceiver가 ..

-

- 미래를 여는 기술을 소개합니다

- 자일링스가 차세대의 올 프로그래머블 디바이스와 개발 환경을 소개합니다. 자일링스의 소프트웨어 정의되..

-

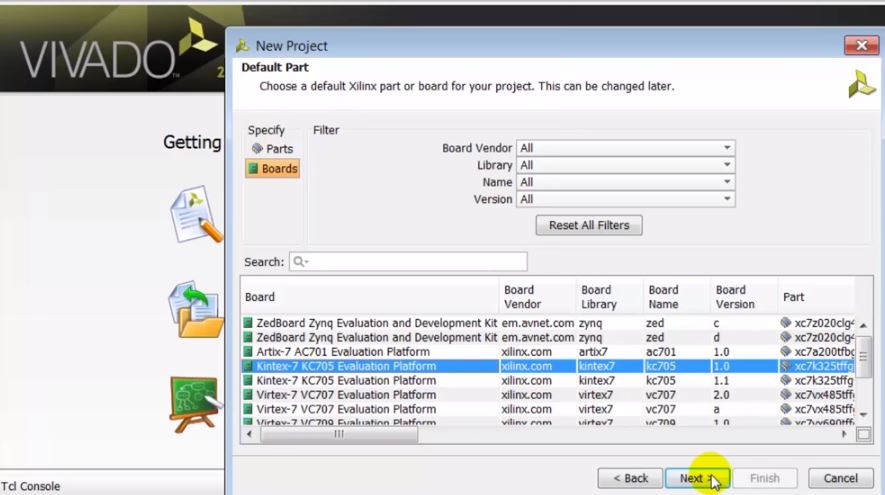

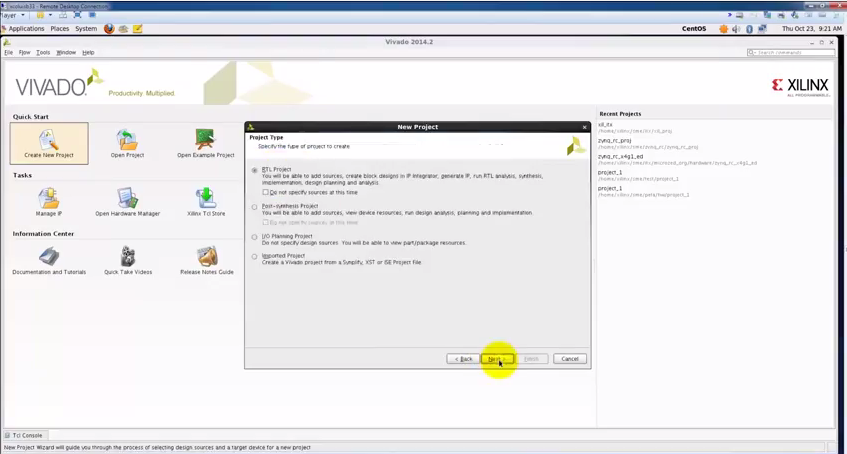

- IP Integrator에서 작성하는 간단한 MicroBlaze 디자인

- 간단한 MicroBlaze 디자인을 IP Integrator에서 작성하고, KC705 타겟 보드에서..

-

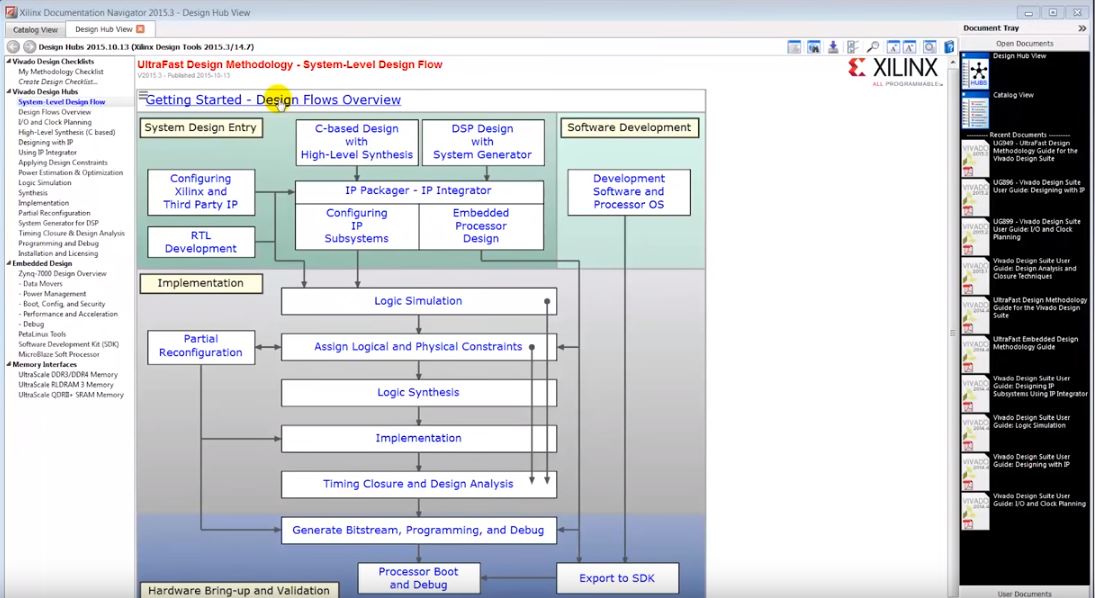

- Vivado 설계 흐름에 대한 개요

- Vivado 통합 설계 환경(IDE)에 대한 소개, 합성과 그리고 시뮬레이션으로부터 구현에 이르는 ..

-

- FAST 영상 특징 추출 알고리즘

- 자일링스 회원사인 ArrayFire사가 SC15에서 FAST 영상 특징 추출 알고리즘의 구현을 시연..

-

- PCIe NIC 카드 폼팩터로 400G의 처리량 구현

- SC15에서 16 채널의 25G 구리선 이더넷 통신(EoC: Ethernet over copper)..

-

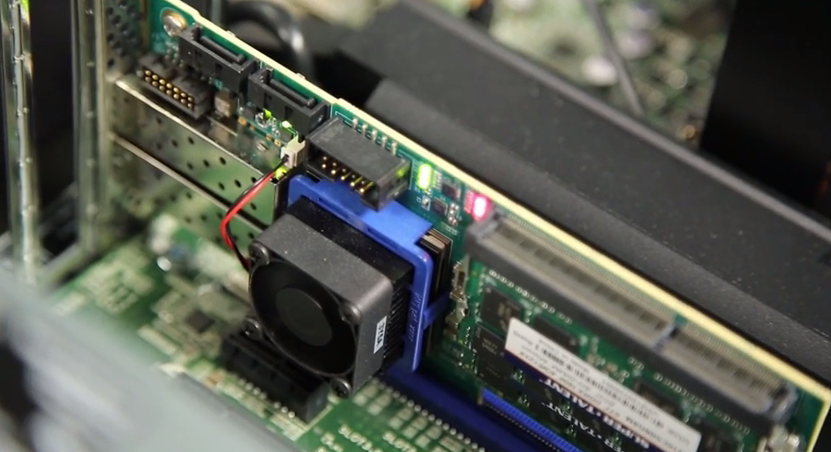

- Xilinx FPGA 가속기 보드

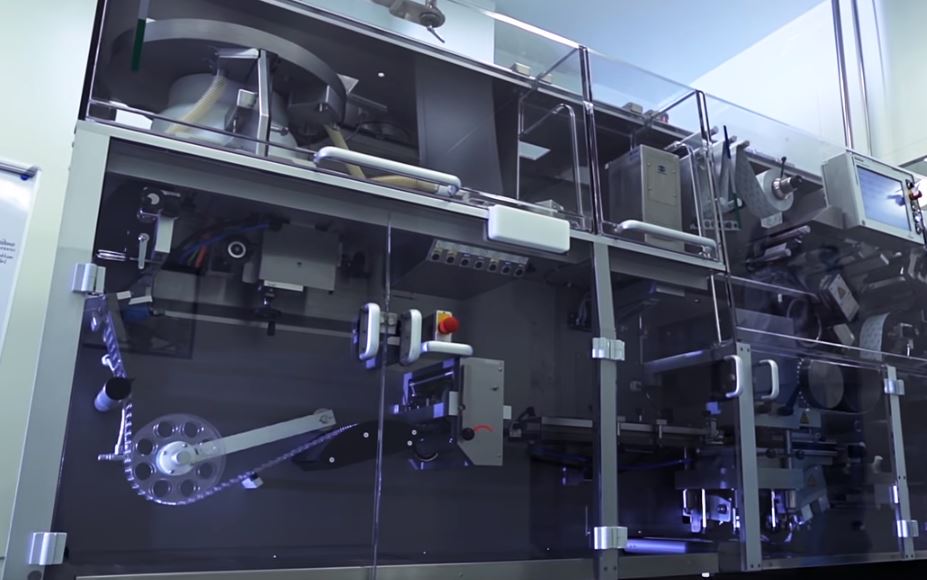

- 자일링스의 회원사인 Alpha Data사가 슈퍼컴퓨팅 컨퍼런스 2015(SC15)에서 생산현장에 투..

-

- Zynq® UltraScale+™ MPSoC: 강력한 비디오 프로세싱 시스템

- Zynq® UltraScale+™ MPSoC의 비디오 프로세싱의 장점을..

-

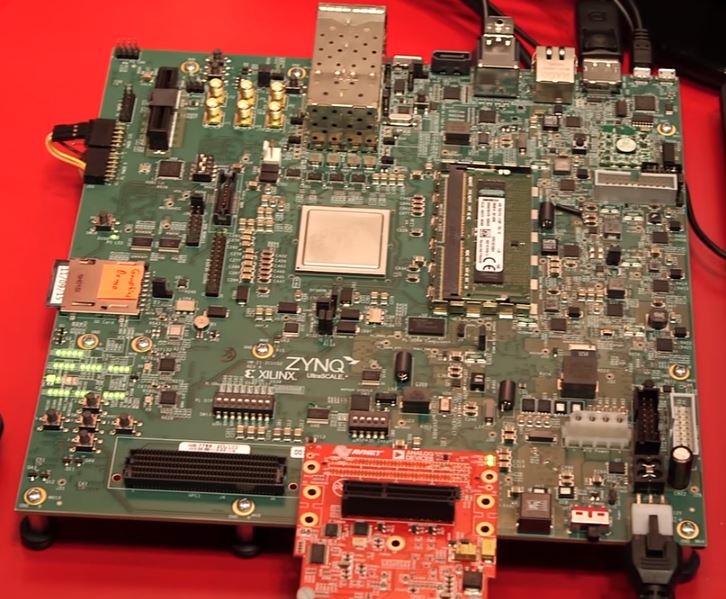

- SDSoC을 이용한 Zynq UltraScale+ MPSoC 개발 플로우

- 본 비디오에서 Zynq® UltraScale+™ MPSoC를 위한 ZCU102 개..

-

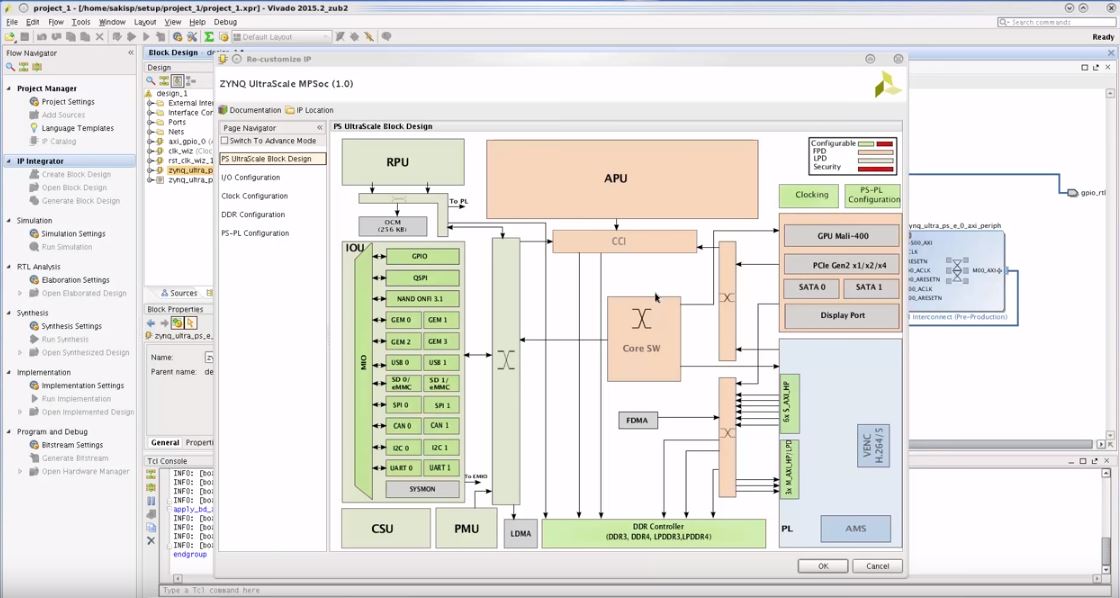

- Vivado PS 구성 위저드의 개요

- 새로운 Zynq Ultrascale+ MPSoC를 위한 Vivado Design Suite를 이용한..

-

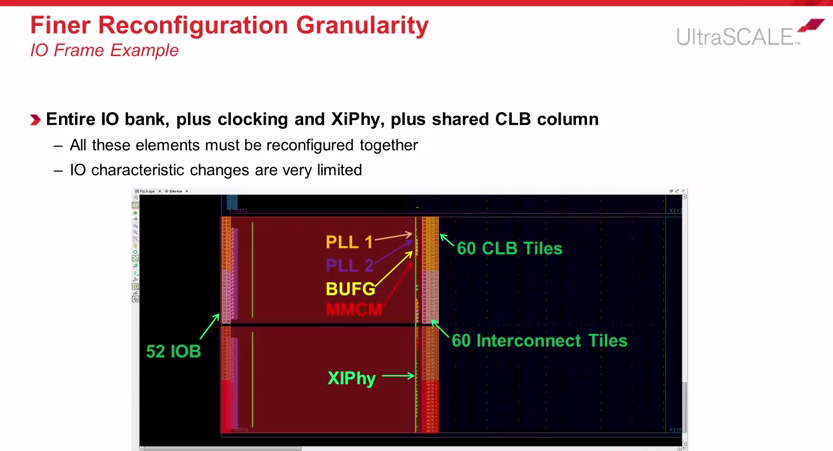

- KCU105를 위한 Tandem PCle 디자인을 개발하세요

- KCU105 평가 키트를 겨냥한 Tandem 디자인 개발 방법을 배우십시오. Tandem 방법론은 ..

-

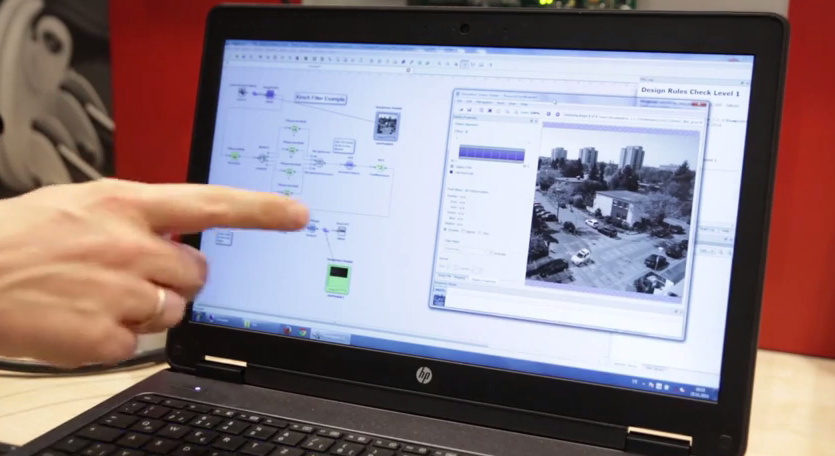

- SDSoC를 이용한 이미지 프로세싱 알고리즘의 하드웨어 최적화 기법

- 대표적인 이미지 프로세싱 알고리즘인 소벨(sobel) 필터를 최적화하기 위한 전형적인 사용자 플로우..

-

- LPDDR4 메모리를 2.4Gbps 속도로 실행시키는 Zynq UltraScale+ 프로세싱 시스템

- Zynq® UltraScale+™ MPSoC의 프로세싱 시스템에 내장된 강화된 컨..

-

- Vivado 2015.3의 점진적인 컴파일 업데이트

- Vivado 2015.3 구현 제품이 새로 제공하는 점진적 컴파일(Incremental Compil..

-

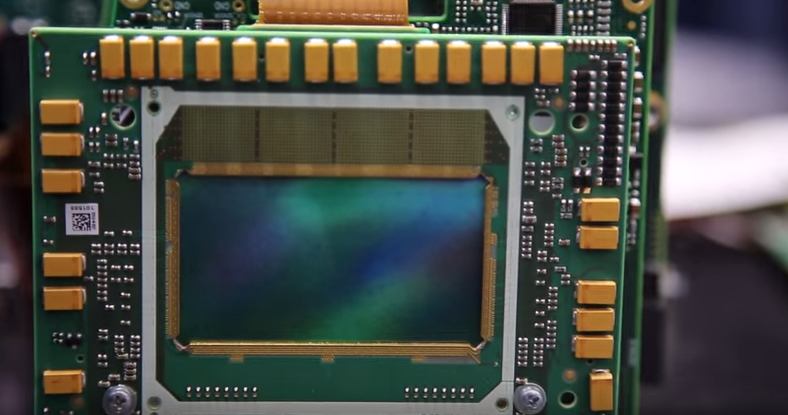

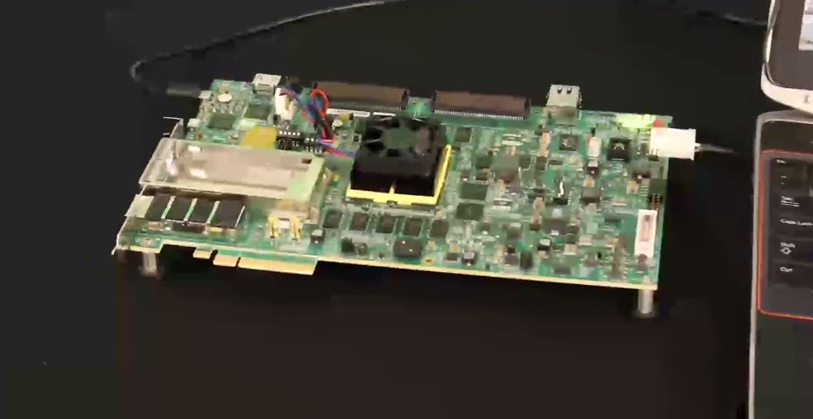

- Zynq UltraScale+ 트랜시버 데모

- UltraScale+ 포트폴리오의 첫번째 주인공,Zynq® UltraSCale+™..

-

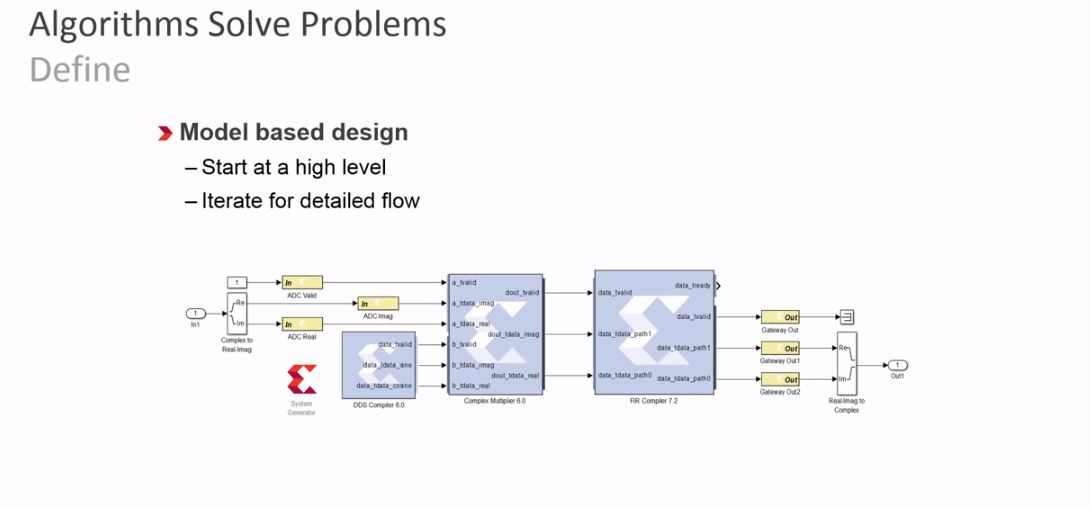

- 시스템 제네레이터를 만나보세요

- 자일링스® 올 프로그래머블 디바이스를 이용해 고성능 DSP 시스템을 디자인할 수 있는 고급툴..

-

- 퀄컴, 자일링스, 멜라녹스 기자 간담회

- 퀄컴은 FPGA 업체인 자일링스, 서버 및 스토리지 통싱 인터페이스 전문 업체인 멜라녹스와 협력관계..

-

- DDR4-2667 SDRAM 인터페이스를 프로그래머블 로직으로 제작할 수 있을까?

- 새로운 비디오는 'Zynq UltraScale+ MPSoC'가 내장된 프로그래머블 로..

-

- Virtex UltraScale VCU108 FPGA 개발 키트

- 이것은 업계 최초의 하이엔드 20nm 키트입니다. 비디오에서 소개하는 VCU108 FPG..

-

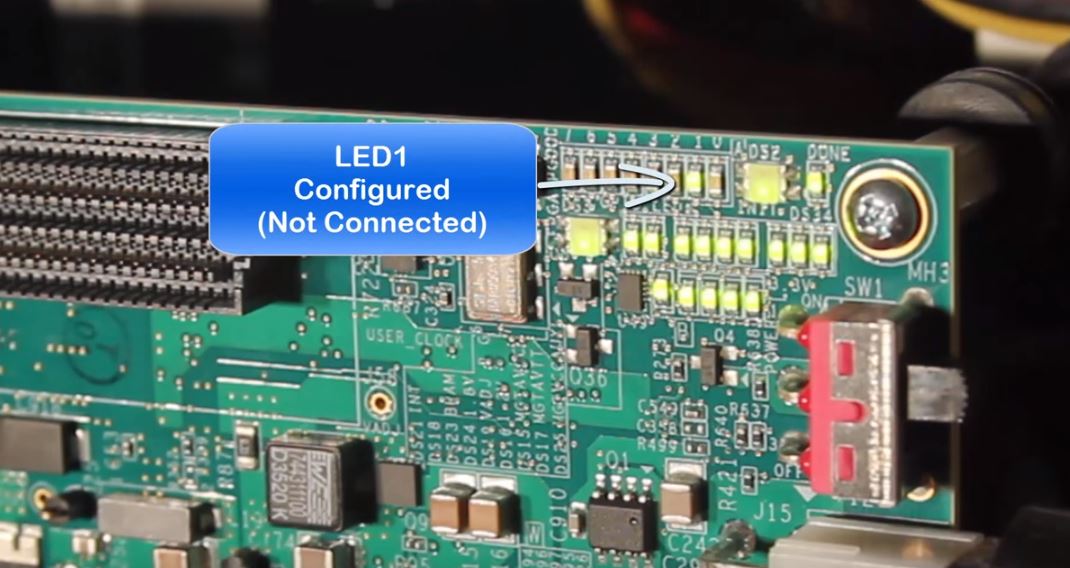

- Zynq UltraScale+ says, “Hello World!”

- UltraScale+ portfolio에서의 첫번째 타자인 the Zynq® UltraSCa..

-

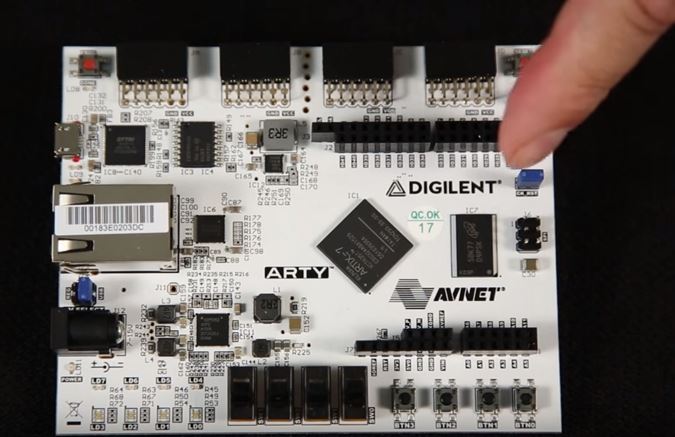

- Artix-7 35T 기반 평가 키트인 ARTY

- ARTY는 Artix-7 FPGA의 융통성과 와트당 성능, 비용절감이라는 이점들을 제공하는 제품입니..

-

- 자일링스가 정의하는 미래 전략과 목표

- 자일링스가 '올 프로그래머블' 업체임을 천명하며 새로운 기업 전략 방향과 향후의 목표..

-

- xilinx와 의료 개발 플랫폼

- 최근에는 의료 기기 개발에 대해 저렴한 비용이지만 더 많은 기능들에 대한 요구가 증가하고 있습니다...

-

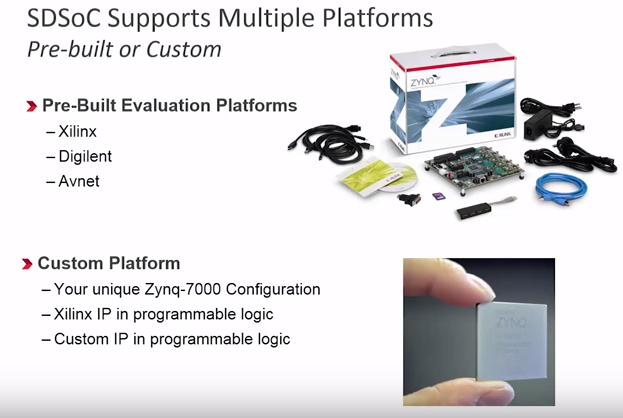

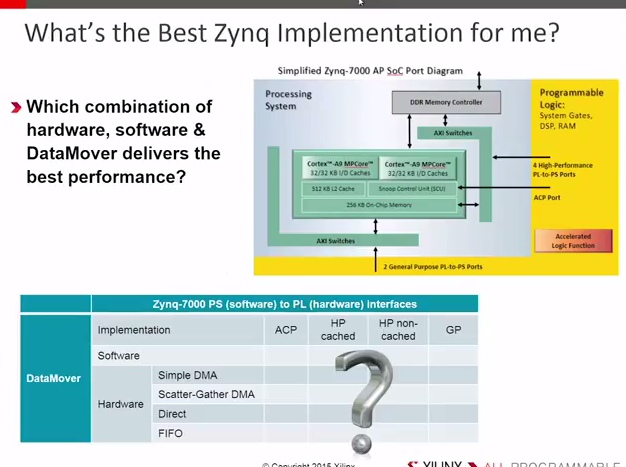

- SDSoC 커스텀 플랫폼

- SDSoC는 Zynq-7000 SoC 애플리케이션을 개발하기에 이상적인 툴로서, 독자적인..

-

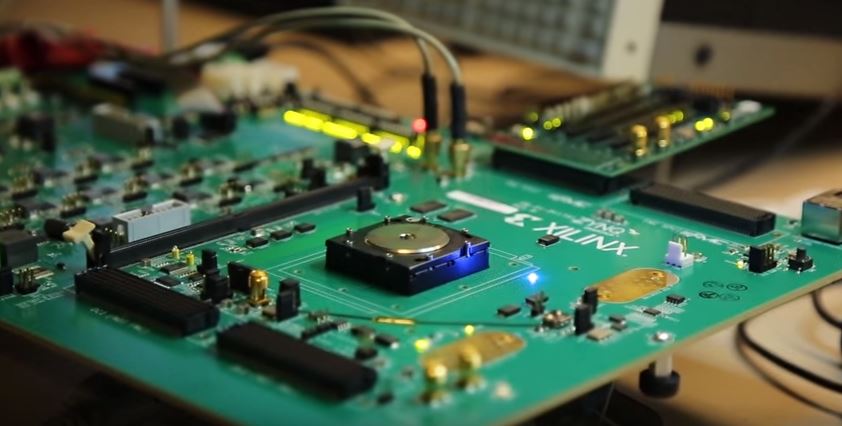

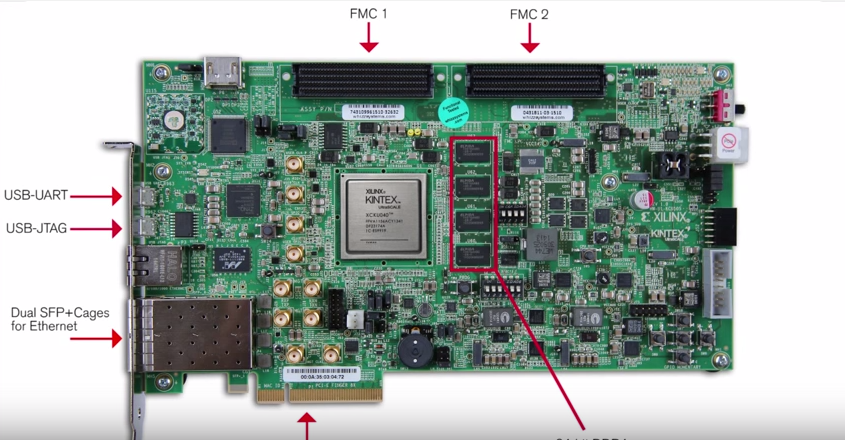

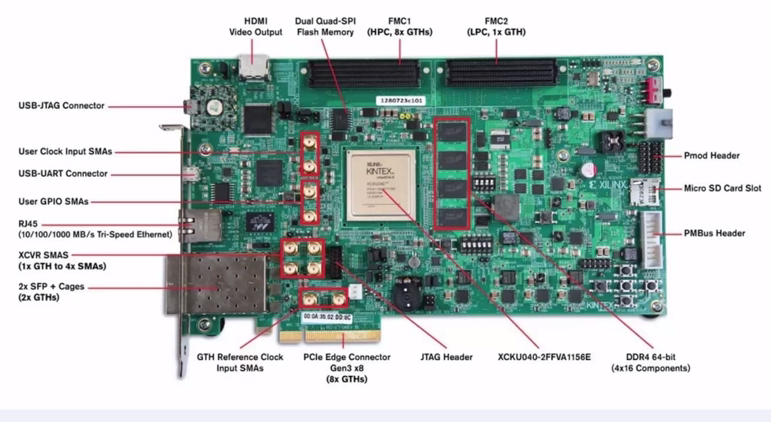

- 킨텍스 울트라 스케일 FPGA KCU105 평가 키트

- 최첨단의 킨텍스 울트라스케일 올 프로그래머블 FPGA를 평가하기 위한 완벽한 개발 환경을 제공하는 ..

-

- Shaping the Future of Video and Vision based Systems

- Aaron Behman, Director of the Broadcast and Pro A/V Bus..

-

- Shaping the Future of 5G Wireless Networks

- Harpinder Matharu, Senior Product Manager at Xilinx, ex..

-

- Shaping the Future of ADAS Systems

- Kevin Tanaka, Senior Manager of the Automotive Business..

-

- Shaping the Future of Industrial IoT ? Smarter Factories, Cities, Medical, and Energy

- Dan Isaacs, Director of Connected Control, Xilinx, disc..

-

- Shaping the Future of Next Generation Cloud Computing

- Ralph Witig, Distinguished Engineer at Xilinx, explains..

-

- Xilinx Annual Global Day of Giving 2015

- On June 11, 2015 our 3rd Annual Global Day of Giving ki..

-

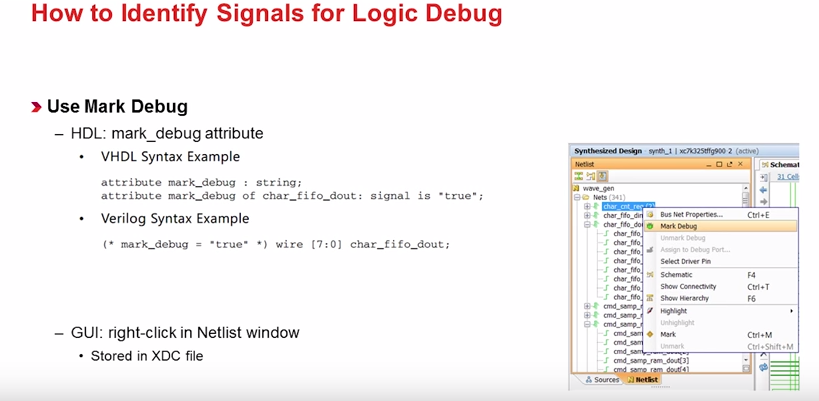

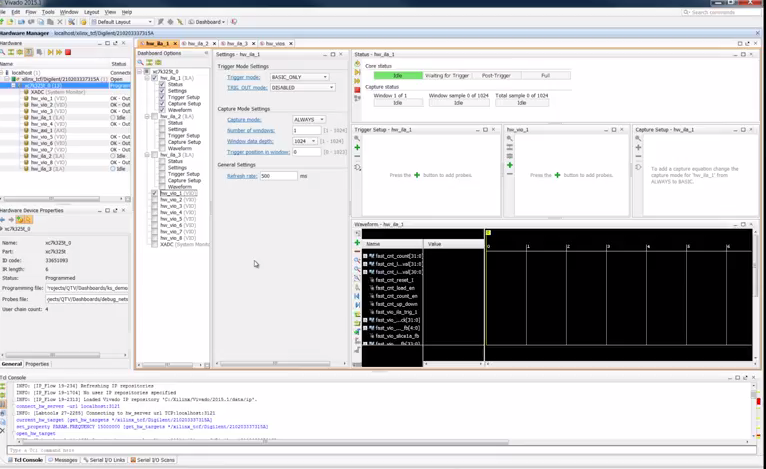

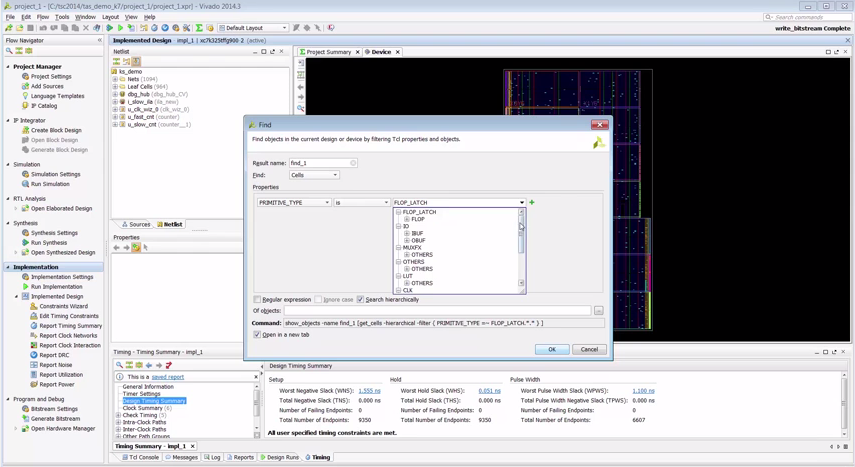

- Logic Debug in Vivado

- Learn about Logic Debug features in Vivado, how to add ..

-

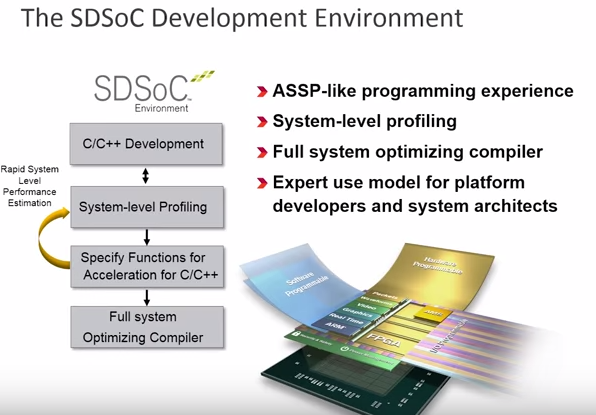

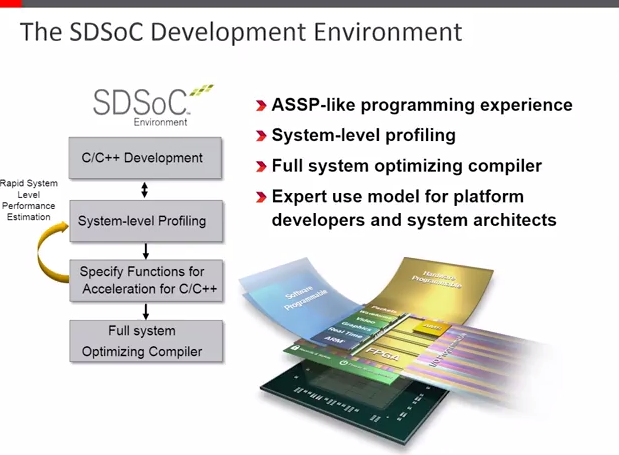

- SDSoC Development Environment Optimization & Debug

- Part 2 of 2 of introduction to SDSoC Development Enviro..

-

- SDSoC Development Environment Estimation & Implementation

- Part 1 of 2 of an introduction to the SDSoC™ ..

-

- Analog Devices demonstrates 5Gsps data acquisition and motor control at Embedded World 2015

- Analog Devices demonstrates interleaving of two AD9625 ..

-

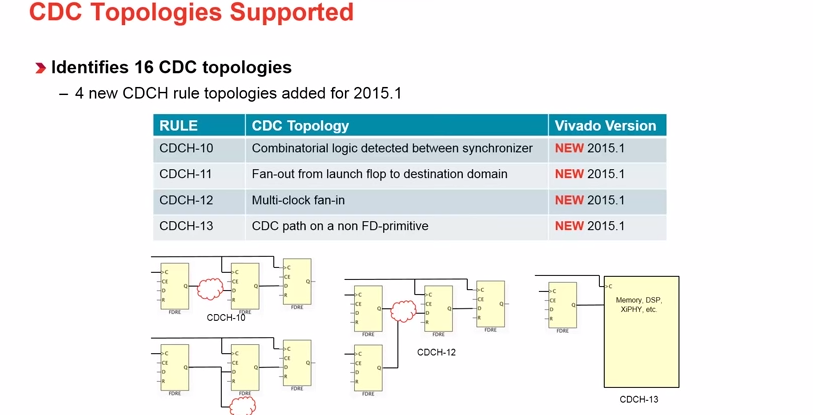

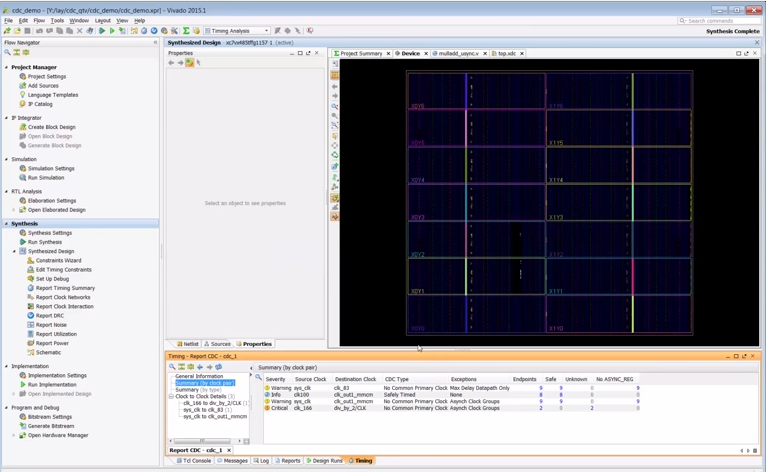

- Using report_cdc to Analyze CDC Structural Issues

- Learn how to analyze, debug and fix CDC issues in your ..

-

- Using report_cdc to Analyze CDC Structural Issues

- Learn how to analyze, debug and fix CDC issues in your ..

-

- Using Vivado Design Suite with Revision Control

- Learn the best practices for using Vivado Design Suite ..

-

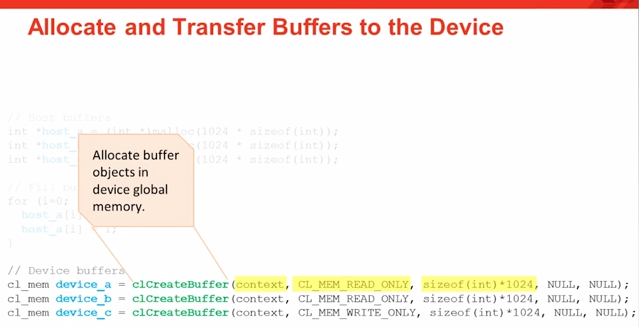

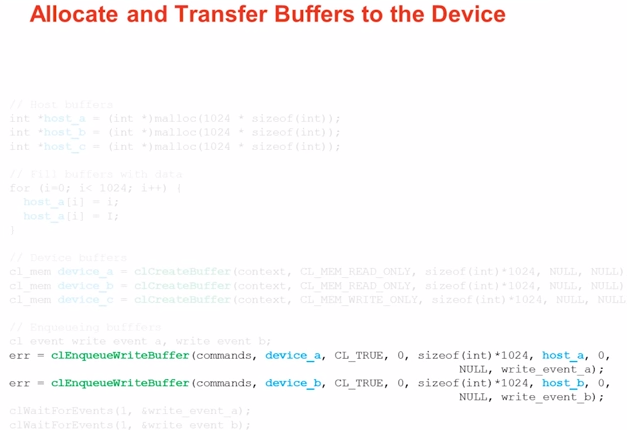

- Fundamental Concepts of Application Host Code

- The OpenCL standard for heterogeneous computing defines..

-

- Fundamental Concepts of Application Host Code

- The OpenCL standard for heterogeneous computing defines..

-

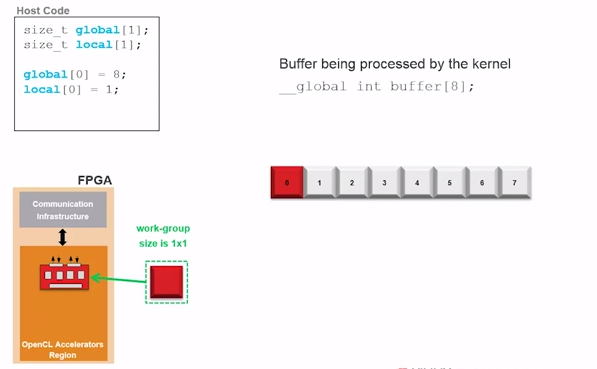

- N Dimensional Kernel Range

- One of the key concepts in OpenCL is the division of th..

-

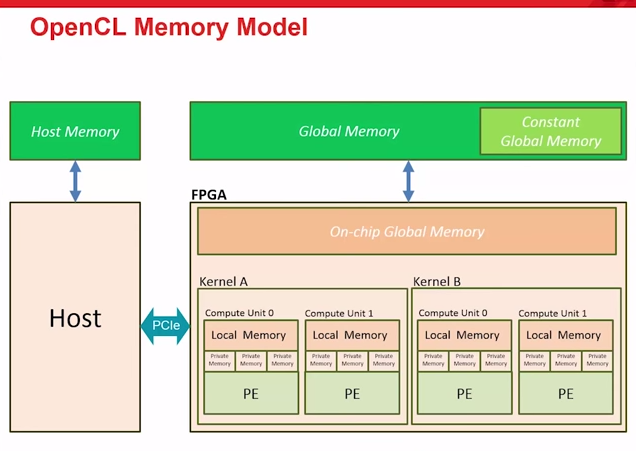

- OpenCL Memory Architecture

- OpenCL defines a memory architecture and abstraction mo..

-

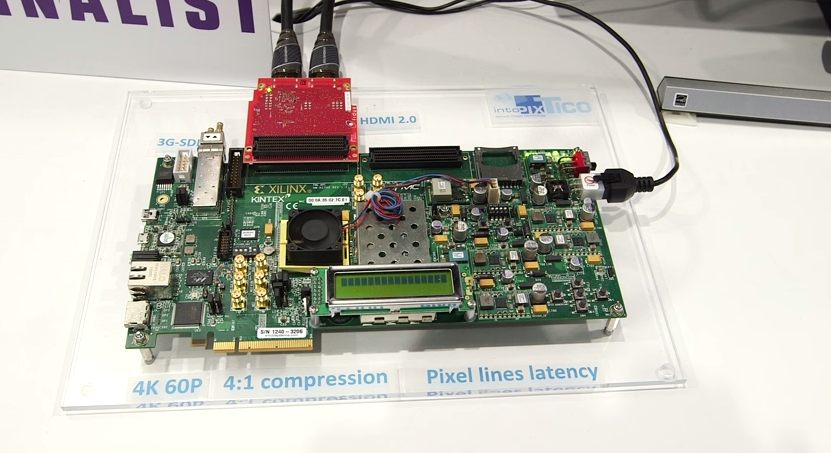

- intoPIX TICO

- The intoPIX TICO mezzanine compression provides up to 4..

-

- intoPIX JPEG 2000

- The video demonstrates 10GbE and 4K live video with its..

-

- NGCodec HEVC Encoder

- This demonstration implements an HEVC encoder running o..

-

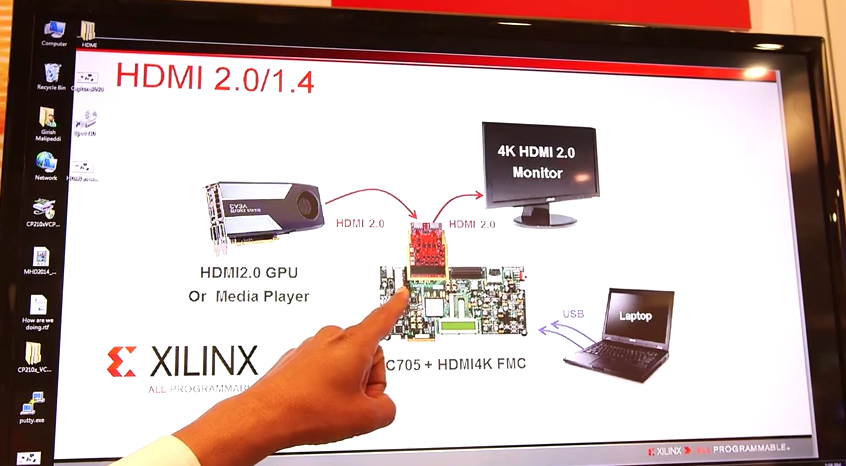

- IP cores for both HDMI 1.4 Tx/Rx and HDMI 2.0 Tx/Rx from Xilinx

- IP cores for both HDMI 1.4 Tx/Rx and HDMI 2.0 Tx/Rx fro..

-

- Xilinx SMPTE ST 2059 & ST 2022

- This early technology demonstration of the upcoming Xil..

-

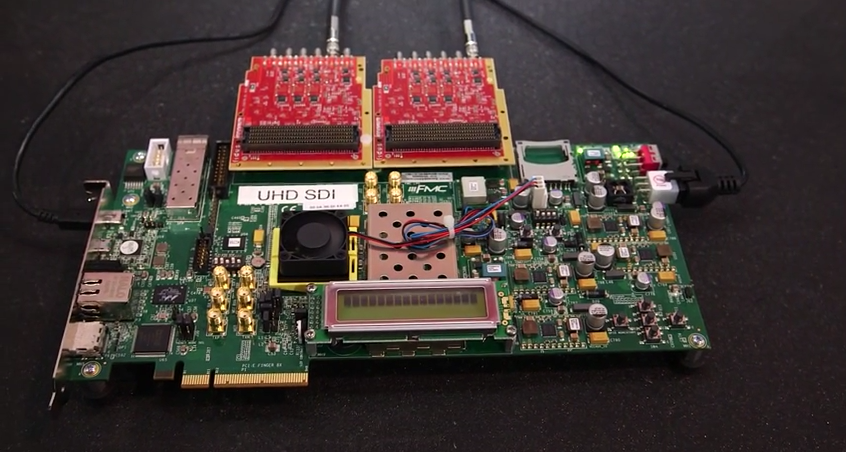

- Xilinx 6G & 12G SDI

- This demonstration showcases reference designs from Xil..

-

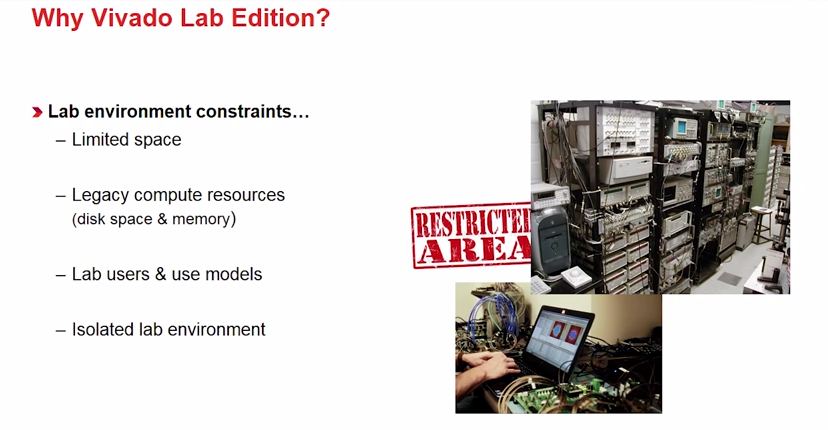

- Using Vivado Lab Edition

- Learn about the features and benefits of the new Vivado..

-

- 1000Base-X over LVDS in UltraScale FPGAs

- This video discusses 1000Base-X over LVDS in UltraScale..

-

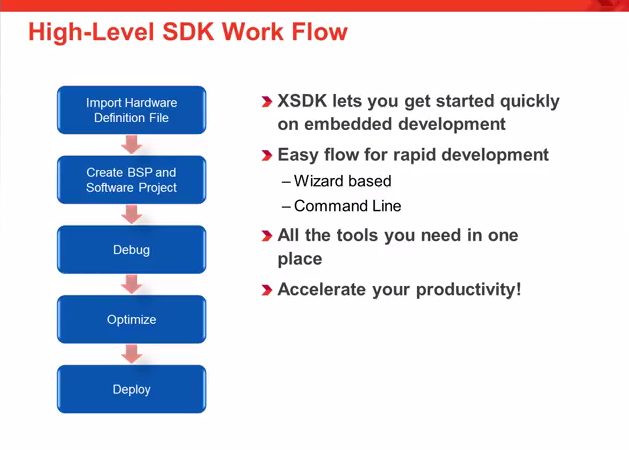

- Xilinx SDK Overview

- Learn how the Xilinx SDK provides you with all the tool..

-

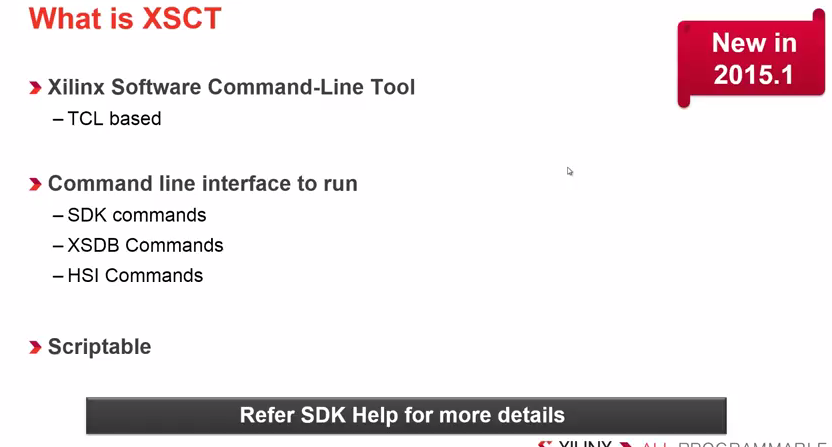

- How to Develop and Debug using XSCT

- Learn how to develop and debug using XSCT, Xilinx Softw..

-

- Working with System Generator for DSP and Platform Design Flows from IP Integrator

- Learn how automation allows DSP system architects, plat..

-

- Using New Dashboards in Vivado Logic Analyzer

-

Learn about the new dashboard improvements introduced..

-

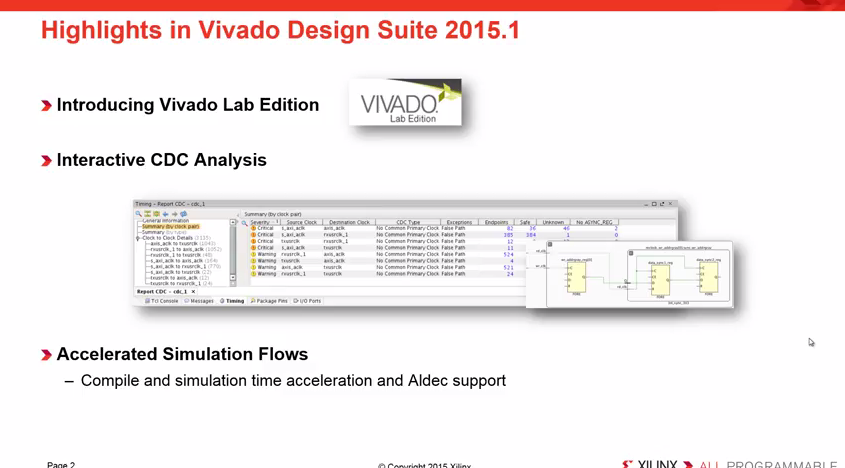

- What's New in Vivado 2015.1

- Learn what's new in the Vivado Design Suite 2015.1...

-

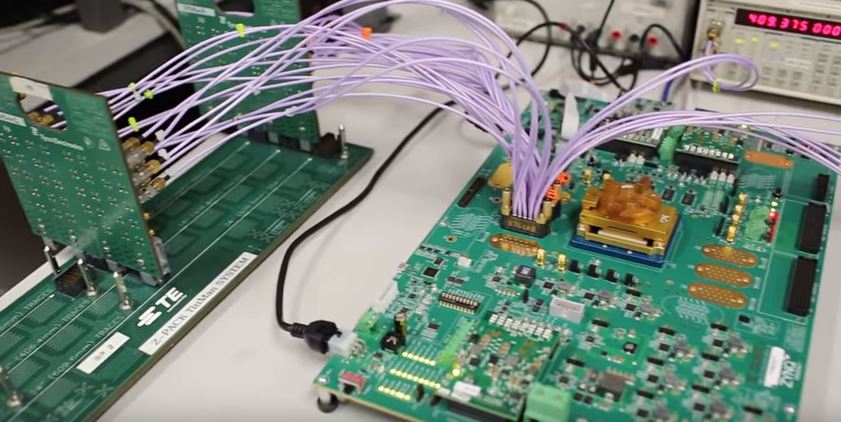

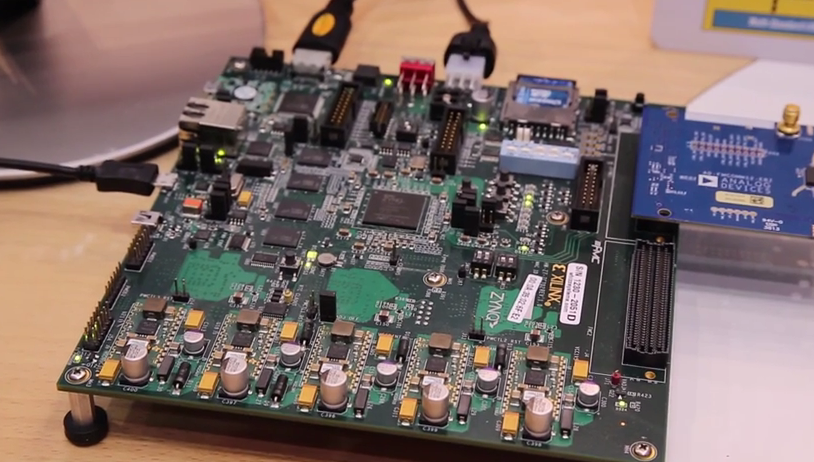

- Kintex UltraScale DSP Kit with 8 Lane JESD204B interface

- The video highlights the Xilinx® Kintex® UltraS..

-

- Designing with UltraScale Memory IP

- Learn how to create an UltraScale memory interface desi..

-

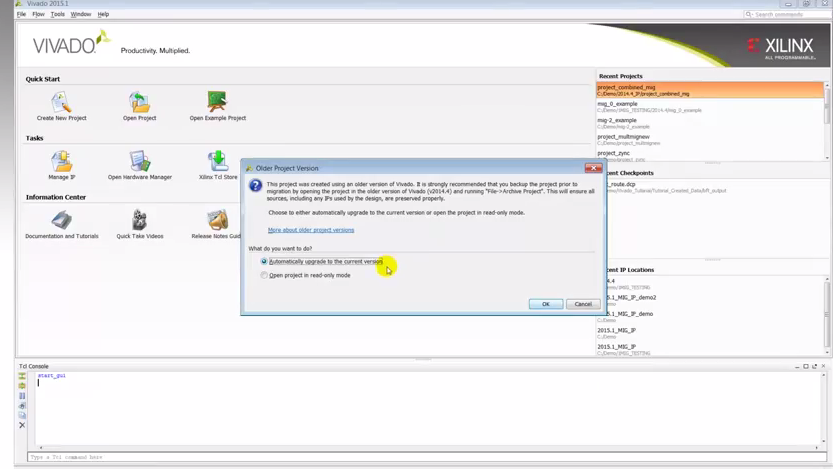

- Migrating UltraScale Memory IOs to 2015.1

- Learn the process involved to migrate the 2014.x Ultras..

-

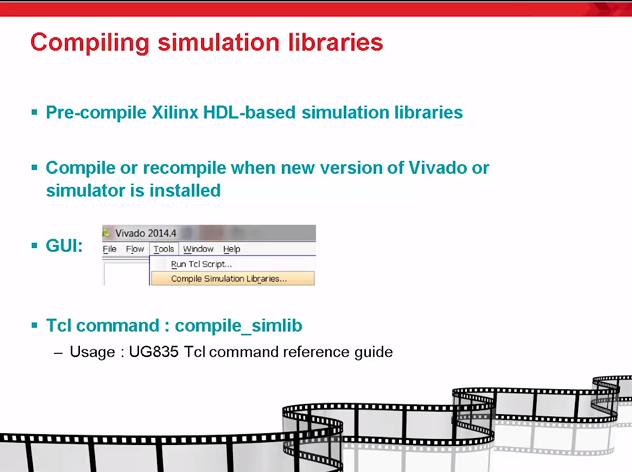

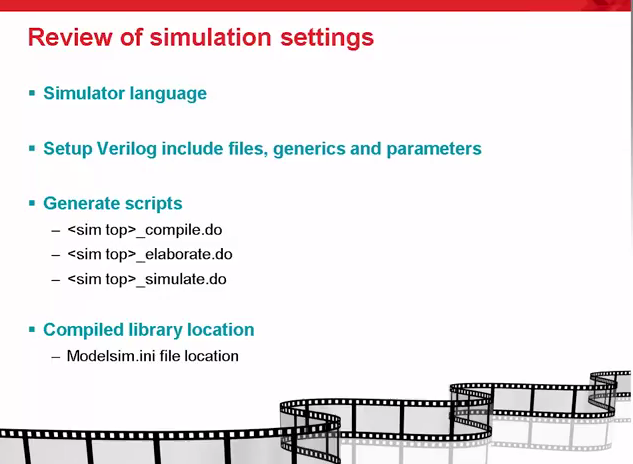

- Simulating with Cadence IES in Vivado

- Learn how to use Vivado design suite to compile simulat..

-

- Simulating with Mentor Questa in Vivado

- Learn how to use Vivado design suite to compile simulat..

-

- JDSU ONT 400GE test solution featuring Xilinx UltraScale FPGAs

- OFC 2015 demonstration of the JDSU ONT 400GE test solut..

-

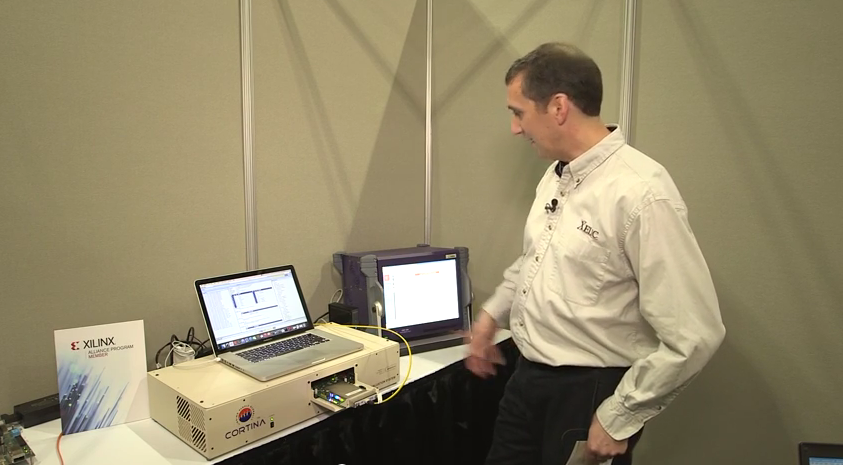

- Xelic 100G Staircase EFEC core

- Xilinx Alliance Member demonstration features the new X..

-

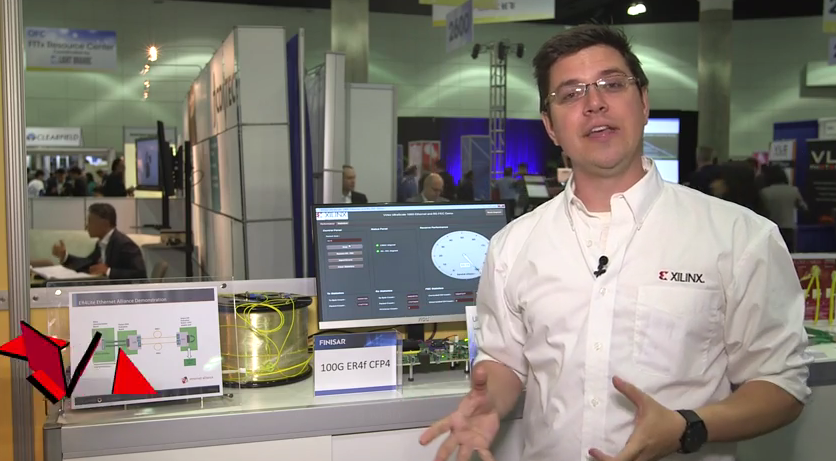

- Virtex UltraScale FPGA interoperates with Finisar CFP4 ER4f optics at OFC 2015

- This demonstration from OFC 2015 showcases the Virtex U..

-

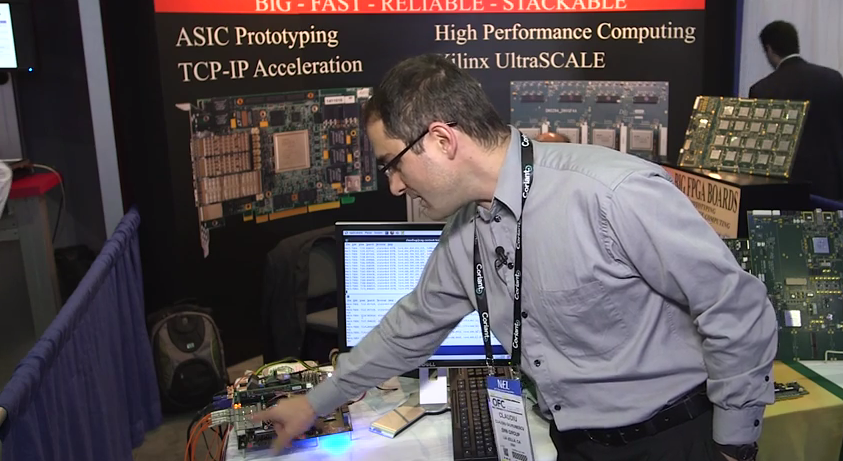

- TCP Offload Engine (TOE128) Demonstration featuring the Kintex UltraScale FPGA

- Xilinx Alliance Member The Dini Group demonstrates TCP ..

-

- MoSys Bandwidth Engine 2 ICs interfacing with Xilinx UltraScale FPGAs at OFC 2015

- Xilinx Alliance Member demonstration from OFC 2015 high..

-

- Virtex UltraScale FPGA interoperates with Sumitomo Electric QSFP28 LR4 optics at OFC 2015

- This demonstration featured at OFC 2015 showcases the V..

-

- High density 100G OTN switching solution demo at OFC 2015

- This OFC 2015 demonstration showcases Xilinx’s hi..

-

- Virtex UltraScale FPGA interoperates with TE QSFP28 SR4 optics at OFC 2015

- Demonstration from OFC 2015 showcasing the Virtex Ultra..

-

- Low latency 4x25G Ethernet MAC solution demo at OFC 2015

- This OFC 2015 demonstration showcases the Virtex UltraS..

-

- IP Light demos efficient CPRI over OTN solution at OFC 2015

- IP Light showcases this pre-standard OTU2r (CPRI over O..

-

- NI introduces new Xilinx-based products and discusses Airbus' Factory of the Future at EW 2015

- NI discusses its new System on Module (SOM) based on Xi..

-

- Xilinx and Ixia present 400GE and 25GE testing solutions at OFC 2015

- In this live presentation from OFC 2015, Xilinx talks w..

-

- MathWorks demonstrates vision processing on Zynq at Embedded World 2015

- MathWorks demonstrates Model-Based Design for rapid pro..

-

- Mentor Embedded demos their multicore framework on Zynq UltraScale+ MPSoC at EW 2015

- Mentor Embedded multicore framework allowing synchroniz..

-

- Enclustra demonstrates 500fps video application on their new Zynq-7045 module at Embedded World 2015

- Certified Xilinx Alliance Member Enclustra announces th..

-

- Xylon demonstrates latest advanced driver assist system (ADAS) based on Zynq-7000 at EW 2015

- Premier Xilinx Alliance Member Xylon demonstrates their..

-

- Topic launches new Zynq-based products and demonstrates medical solution at Embedded World 2015

- Xilinx Premier Alliance Program Member Topic Embedded P..

-

- Xilinx SDK System Performance Tools Overview

- Learn about the System Performance Analysis tools in SD..

-

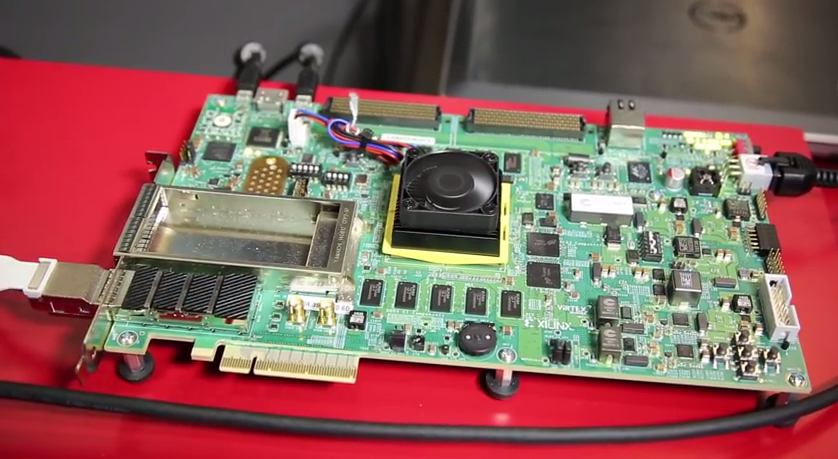

- UltraScale Integrated 100G Ethernet IP for 10x10G and 4x25G

- This video demonstrates how using an integrated Etherne..

-

- Three Byte Intermedia demonstrate MoMath Robot Swarm based on Zynq-7000 All Programmable SoC

- This interactive robot swarm demonstrates a vision-base..

-

- Metaio demonstrates Simultaneous Localization and Mapping (SLAM) for Automotive

- This demonstration presents a key algorithm for self-dr..

-

- Introducing the SDSoC Development Environment

- The SDSoC development environment provides a greatly si..

-

- Analog Devices: DDS HLS IP with Zynq SDR kit

- Analog Devices demonstrates DDS HLS IP with Zynq SDR ki..

-

- iVeia: Canny edge detection HLS IPs with iVeia vision kit

- iVeia demonstrates Canny edge detection HLS IPs with iV..

-

- Xylon: Face detection C-callable RTL IP with MicroZed vision kit

- Xylon demonstrates face detection C-callable RTL IP wit..

-

- DAVE Embedded Systems: Matrix multiply HLS IP with DAVE Bora kit

- DAVE Embedded Systems demonstrates Matrix multiply HLS ..

-

- SDSoC Development Environment Estimation & Implementation

- Part 1 of 2 of an introduction to the SDSoC™ Deve..

-

- SDSoC Development Environment Optimization & Debug

- Part 2 of 2 of introduction to SDSoC™ Development..

-

- Zynq UltraScale+ MPSoC by Vamsi Boppana, VP of Processor Development, Xilinx

- Building on the industry’s first All Programmable..

-

- 16nm UltraScale+ Family by Victor Peng, Executive Vice President of the Programmable Products Group

- Xilinx’s 16nm UltraScale+™ family of FPGAs,..

-

- How to Create Linux Applications using Xilinx SDK

- Learn how to create Linux Applications using Xilinx SDK..

-

- ynq PCI Express Root Complex Made Simple

- Creating a PCI Express Root Complex using IPI and PetaL..

-

- Vivado Hardware Manager For MIG IP

- Learn how to quickly verify the calibration and read wi..

-

- Xilinx at SPS Drives 2014 | SoC-e

- This High Availability Cyber-Physical System demonstrat..

-

- Xilinx at SPS Drives 2014 | Silicon Software

- This Embedded Computer Vision for Intelligent Stations ..

-

- Xilinx at SPS Drives 2014 | Qdesys

- This Silicon Carbine Multilevel Inverter demonstration ..

-

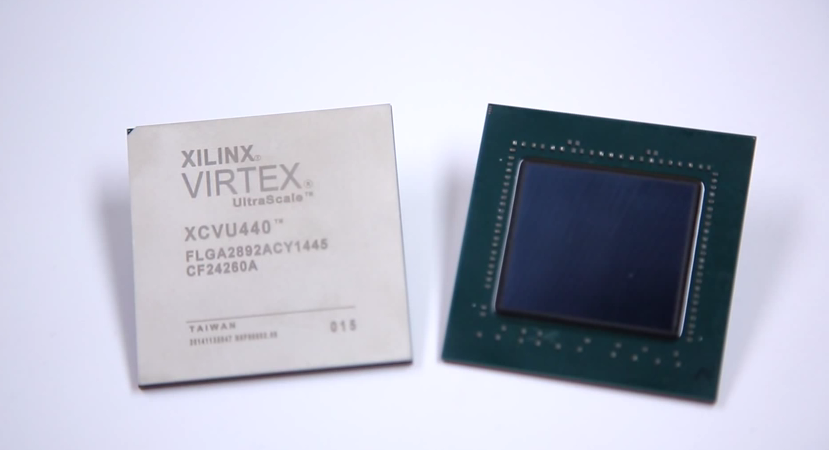

- Virtex UltraScale VU440 FPGA Demonstration

- See the new Virtex Ultrascale VU440, the world’s ..

-

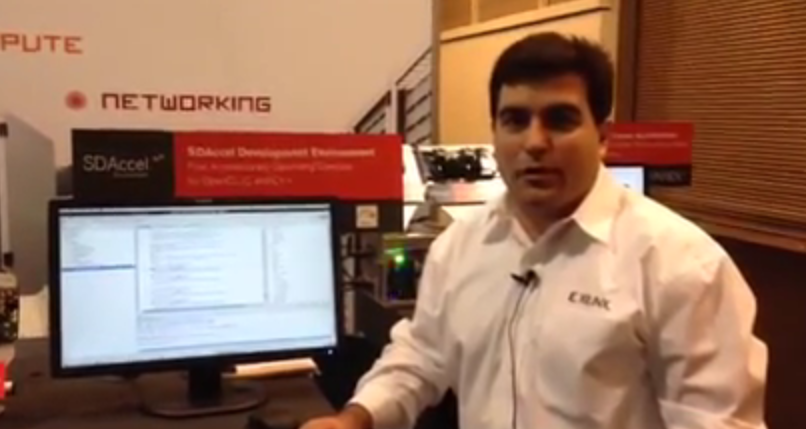

- SDAccel Development Environment Demonstration

- This video demonstrates the SDAccel development environ..

-

- Integrated Interlaken operating at 150 Gb/s in UltraScale FPGAs

- The UltraScale FPGAs now feature integrated Interlaken ..

-

- Hello World in 5 Minutes on Zynq with Xilinx SDK

- Learn how to create a simple application using the appl..

-

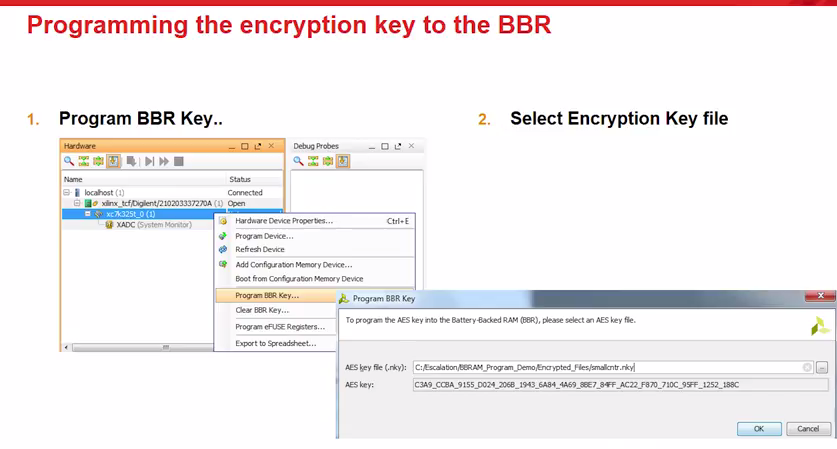

- Using Advanced Encryption Standard Keys with the Battery-Backed (BBR) RAM

- Learn how to use Vivado Design Suite to use the advance..

-

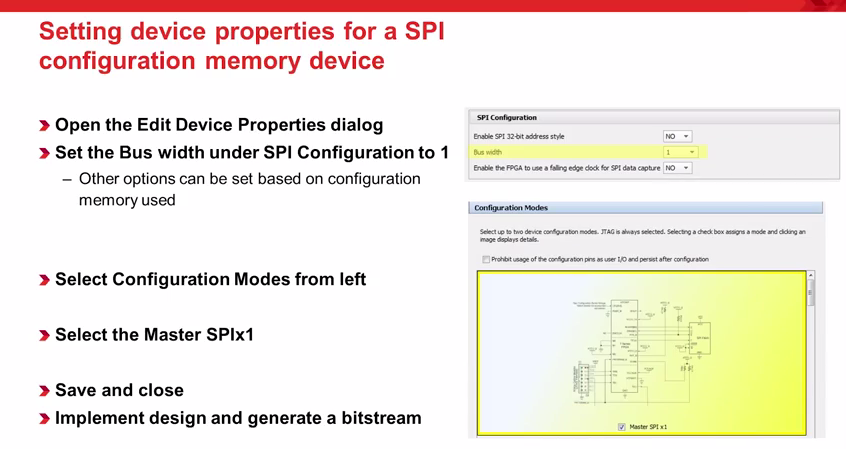

- Indirectly Program an FPGA using Vivado Device Programmer

- Learn how to use Vivado Device Programmer to create and..

-

- SDAccel Development Environment for OpenCL, C and C++

- Demonstration of Xilinx’s software defined develo..

-

- Partial Reconfiguration for UltraScale

- Learn how Xilinx has advanced their groundbreaking Part..

-

- SDAccel Development Environment for Xilinx Virtex-7 Devices

- Demonstration of OpenCL applications featuring the Alph..

-

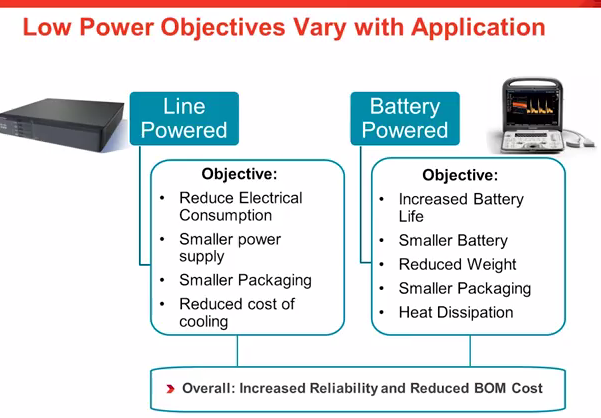

- Zynq 7000 All Programmable SoC Low Power Solutions

- Learn about power management techniques with the Zynq-7..

-

- SDAccel Development Environment for Kintex-7 Devices

- Demonstration featuring the Pico Computing M505-K325T a..

-

- Debugging at Device Startup

- Learn how to use Vivado to debug at and around device s..

-

- Introducing SDAccel Development Environment

- The SDAccel™ development environment for OpenCL&t..

-

- AXI PCI Express MIG Subsystem Built in IPI

- Learn how to use Xilinx's Vivado IP Integrator (IPI..

-

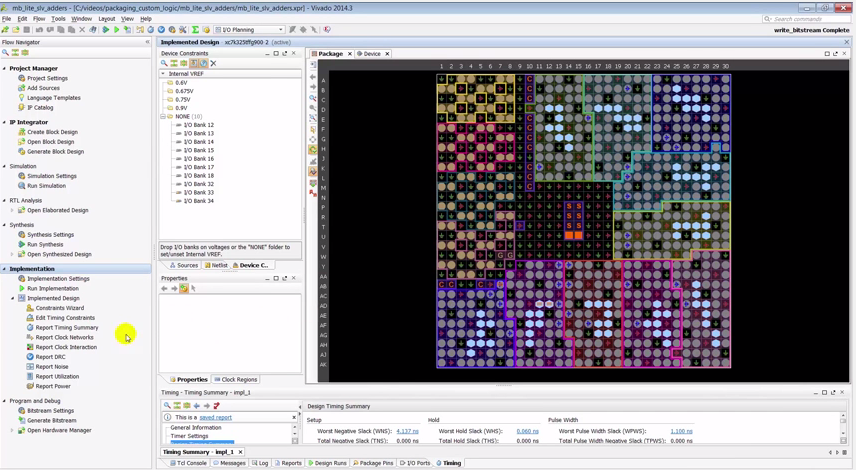

- Packaging Custom IP for using in IP Integrator

- Learn how to create an AXI Peripheral using the Create ..

-

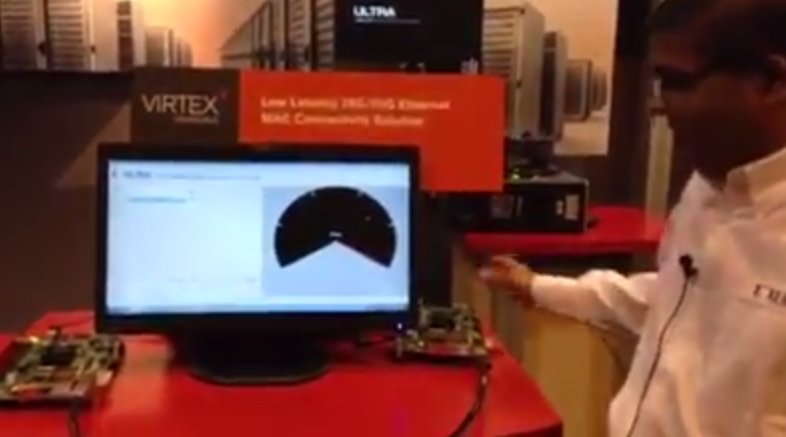

- Low Latency 25G/50G Ethernet MAC Connectivity Solution

- This demonstration utilizes two Virtex® UltraScale&..

-

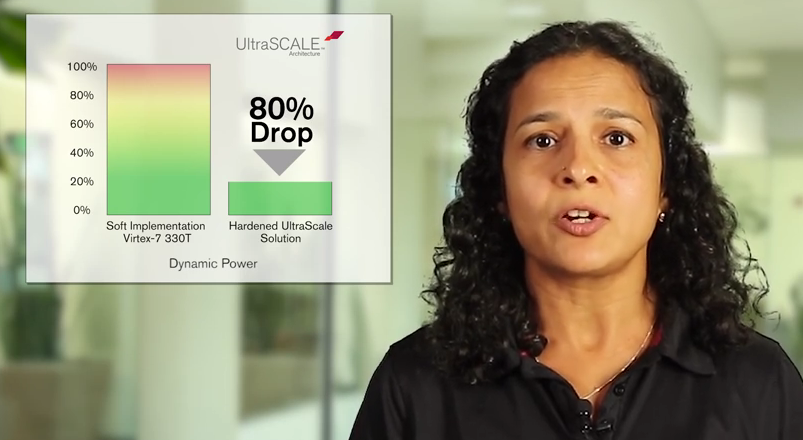

- The UltraScale Architecture for Highest Utilization and Superior Performance

- The UltraScale architecture introduces many innovations..

-

- Xilinx at ARM TechCon 2014 | NI

- Eric Myers, Product Manager for Embedded Products, NI, ..

-

- Xilinx at ARM TechCon 2014 | Van Gogh Imaging

- Greg Werth, VP of Marketing, Van Gogh Imaging shows how..

-

- Xilinx at ARM TechCon 2014 | Cloudium

- John Hickey, CEO, Cloudium Systems, demonstrates how th..

-

- Xilinx at ARM TechCon 2014 | Topic Embedded Systems

- Rene Zenden, Product Manager, Topic Embedded Systems, s..

-

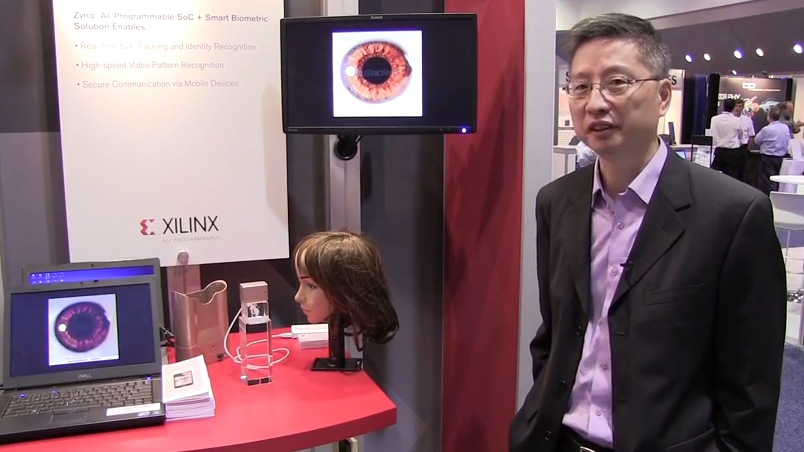

- Xilinx at ARM TechCon 2014 | Cornerstone Identity Company

- Larry Wang, CEO & Founder, Cornerstone Identity Com..

-

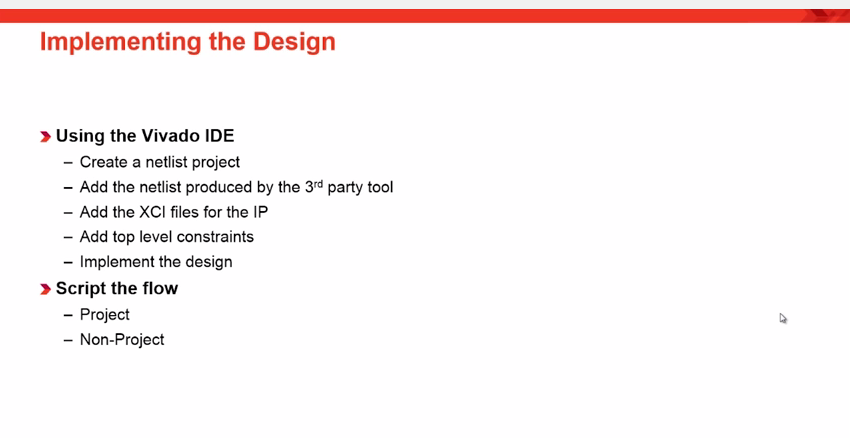

- Using IP with 3rd Party Synthesis Tools

- Learn how to use Vivado IP with 3rd party synthesis too..

자일링스의 최신 전략과 포트폴리오 소개

마케팅 전문인 Steve Glaser

가 이야기하는 자일링스의 최신 전력과 포트폴리오를 알아보세요

2016-03-21 오후 2:31:37